JPE 19-1-13

https://doi.org/10.6113/JPE.2019.19.1.134 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Single-Phase Step-Up Five-Level Inverter with Phase-Shifted Pulse Width Modulation

Jianfei Chen<sup>†</sup>, Caisheng Wang<sup>\*\*</sup>, and Jian Li<sup>\*</sup>

†,\*School of Electrical Engineering, Chongqing University, Chongqing, China \*\*Department of Electrical and Computer Engineering, Wayne State University, Detroit, MI, USA

#### **Abstract**

A single-phase step-up five-level inverter topology with a new phase-shifted pulse width modulation (PS-PWM) strategy is proposed in this paper. When compared with conventional single-phase five-level inverter topologies, the proposed topology can realize multilevel inversion with a double step-up ratio, a reduced number of switching devices and self-balanced capacitor voltages. When compared with the conventional PS-PWM strategy, the new PS-PWM strategy can be implemented with one carrier reduced, which makes it much easier to implement in a digital signal processor (DSP) system. Experimental results have been presented to verify the effectiveness of the proposed inverter and the PS-PWM strategy.

Key words: Five-level, PS-PWM, Self-balance, Single-phase, Step-up

# I. INTRODUCTION

Single-phase multilevel inverters have received increasing attention due to their interesting features such as low harmonic currents and low voltage stresses across switching devices. As the output voltage level increases, the output harmonic content of inverters decreases, which allows for the use of smaller and less expensive output filters. Single-phase five-level inverters are widely used single-phase multilevel topology. The single-phase five-level inverter was first proposed by cascading two H-bridge inverters (CHB) to produce a five-level waveform [1], [2]. However, eight switches and their corresponding drivers are necessary for the circuit. Moreover, two split dc sources are needed, which can result in voltage-imbalance issues that should be carefully studied [3]. A single-phase full-bridge five-level neutral-point potential clamped (NPC) inverter and an improved version of the inverter have been proposed in [4]. Both of the circuits have only one dc source, which reduces the cost when compared with CHB. An improved modulation strategy has been proposed to achieve voltage-balance control for the two split capacitor voltages in the single-phase active NPC (ANPC) [5]. In [6], a single-phase five-level inverter comprising an asymmetric flying-capacitor H-bridge with a novel PWM scheme was proposed. Although improved output waveforms, a small filter size and low total harmonics distortion (THD) can be achieved by the circuit in [6], a pre-charging problem increases the complexity of the modulation strategy due to the flying-capacitor. To reduce the number of switches, an alternative five-level inverter was proposed in [7] and further studied and improved in [8-10]. Only five switches are needed in these newly proposed inverters, which simplifies the corresponding drive circuits. However, there are four diodes in the circuit of each type of inverter, which is not helpful for improving efficiency.

Single-phase five-level inverter topologies employing a coupled-inductor technique were proposed in [11]-[13]. The drawback of these circuits is that the coupled inductors need to be carefully designed. In addition, the five-level ANPC with coupled inductors in [12] has many switches. A simplified single-phase multistring five-level inverter was proposed in [14], [15]. Although the circuit can have a smaller number of components and can achieve a high efficiency, the two dc link capacitors are not connected in series, which requires two front step-up dc/dc converters or separate input sources. This increases the cost of the whole two-stage dc/ac power conversion system. A five-level inverter consisting of only

Manuscript received May 19, 2018; accepted Nov. 6, 2018

Recommended for publication by Associate Editor Yijie Wang.

<sup>†</sup>Corresponding Author: cjf6221@gmail.com

Tel: +86-18883876496, Chongqing University

\*School of Electrical Engineering, Chongging University, China

\*\*Department of Electrical and Computer Engineering, USA

six switches was proposed to achieve five-level PWM operation without clamping diodes or flying capacitors [16]. However, four active switches endure full dc-bus voltage stress with a high frequency in this topology. Recently, an enhanced single-phase step-up five-level inverter was proposed in [17]. This inverter was based on the switched-diode-capacitor cell presented in [18]. When compared with conventional five-level inverters, the inverter in [17] can realize multilevel inversion with a high step-up output voltage and a simple structure, which is mostly attributed to the switched-diode-capacitor cell. However, additional power switches and diodes are necessary and the corresponding modulation strategy is complicated.

A new single-phase five-level inverter topology with a new PS-PWM strategy is proposed in this paper. A self-balanced function for the capacitor voltages and a two-time step-up function are integrated in the new topology with a reduced number of power components. Four switches operate at a high frequency with low voltage stresses, while the other two switches operate at the line frequency (50 Hz) with high voltage stresses. The proposed PS-PWM strategy could use fewer triangular carriers to achieve the same performance as the conventional PS-PWM strategy.

# II. PROPOSED INVERTER

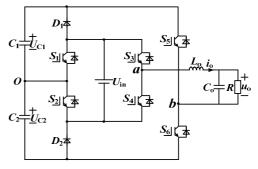

Fig. 1 shows the proposed single-phase five-level inverter. As shown in this figure, there are six active switches, two diodes, and one dc source with two separate capacitors. The power switches  $S_1$  and  $S_2$  complement each other; as do the switches  $S_3$  and  $S_4$ , and  $S_5$  and  $S_6$ . Therefore, there are three independent active switches  $S_1$ ,  $S_4$  and  $S_6$ . In Fig. 1,  $U_{C1}$  and  $U_{C2}$  represent the two split capacitor voltages,  $U_{in}$  represents the input voltage and  $u_0$  represents the output voltage. In addition, the two split capacitors have the same capacitance.

$$C_1 = C_2 \tag{1}$$

To some extent, the two capacitor voltages  $U_{C1}$  and  $U_{C2}$  remain stable. However, they fluctuate frequently due to the charging and discharging of the capacitors. Therefore, Table I gives the charge and discharge states of the two capacitors  $C_1$  and  $C_2$ . Due to the symmetry of the sine wave reference, the charging time of  $C_1$  is the same as that of  $C_2$ , i.e., the conduction time of  $S_2$  is the same as that of  $S_1$ .

For the proposed inverter, the two switches  $S_5$  and  $S_6$  are operated at the line frequency, while the other switches are operated at a high switching frequency. Based on the states of the switches, there are eight valid switching combinations that generate the required five output levels as shown in Table I. The corresponding operation stages of the five-level inverter are given in Fig. 2. For the convenience of the illustration, the switching function of the switches in Table I is defined as follows:

Fig. 1. Proposed single-phase step-up five-level inverter.

TABLE I SWITCHING COMBINATIONS

| Stage | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $u_{\mathrm{ab}}$           |

|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| I     | 0     | 1     | 1     | 0     | 0     | 1     | $U_{\rm C1} + U_{\rm C2}$   |

| II    | 0     | 1     | 0     | 1     | 0     | 1     | $U_{ m C2}$                 |

| III   | 1     | 0     | 1     | 0     | 0     | 1     | $U_{in}$                    |

| IV    | 1     | 0     | 0     | 1     | 0     | 1     | 0                           |

| V     | 0     | 1     | 1     | 0     | 1     | 0     | 0                           |

| VI    | 0     | 1     | 0     | 1     | 1     | 0     | - $U_{ m in}$               |

| VII   | 1     | 0     | 1     | 0     | 1     | 0     | $-U_{\mathrm{C1}}$          |

| VIII  | 1     | 0     | 0     | 1     | 1     | 0     | $-U_{\rm C1}$ $-U_{\rm C2}$ |

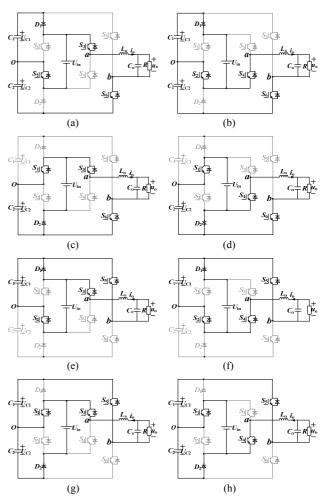

Fig. 2. Operating stages: (a) I; (b) II; (c) III; (d) IV; (e) V; (f) VI; (g) VII; (h) VIII.

$$S_{i} = \begin{cases} 1 & S_{i} \text{ is on} \\ 0 & S_{i} \text{ is off} \end{cases}, \quad i = 1, 2 \dots 6$$

(2)

The eight operating stages of the proposed inverter are given in Fig. 2 and described in details as follows.

- 1) Maximum positive output level ( $U_{C1}+U_{C2}$ ) (Stage I): in Stage I, the switches  $S_2$ ,  $D_1$ ,  $S_3$  and  $S_6$  are ON, and all of the other switches are off. The total voltage ( $U_{C1}+U_{C2}$ ) is applied to the LC output filter, and the capacitor  $C_1$  is charged by the input source  $U_{in}$ .

- 2) Half positive output level U<sub>in</sub> or U<sub>C2</sub> (Stages II and III): one switching combination shown in Stage II is such that the switches S<sub>2</sub>, D<sub>1</sub>, S<sub>4</sub> and S<sub>6</sub> are ON. The other switching combination is such that the switches S<sub>1</sub>, D<sub>2</sub>, S<sub>3</sub> and S<sub>6</sub> are ON. During Stage II, the voltage U<sub>C2</sub> is applied to the LC output filter and the capacitor C<sub>1</sub> is charged by U<sub>in</sub> simultaneously. During Stage III, U<sub>in</sub> is applied to the LC filter and charges the capacitor C<sub>2</sub>.

- 3) Zero output level (Stages IV and V): in Stage IV, the switches S<sub>1</sub>, D<sub>2</sub>, S<sub>4</sub> and S<sub>6</sub> are ON. In Stage V, the switches D<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> and S<sub>5</sub> are ON. During these two stages, zero voltage is applied to the LC output filter. The capacitor C<sub>2</sub> is charged by U<sub>in</sub> during Stage IV and the capacitor C<sub>1</sub> is charged by U<sub>in</sub> during Stage V.

- 4) Half negative output level  $U_{\rm in}$  or  $-U_{\rm C1}$  (Stages VI and VII): one switching combination shown in Stage VI is such that the switches  $D_1$ ,  $S_2$ ,  $S_4$  and  $S_5$  are ON. The other switching combination shown in Stage VII is such that the switches  $S_1$ ,  $D_2$ ,  $S_3$  and  $S_5$  are ON. During Stage VI,  $-U_{\rm in}$  is applied to the LC output filter and the capacitor  $C_1$  is charged by  $U_{\rm in}$  simultaneously. During Stage VII,  $-U_{\rm C1}$  is applied to the LC output filter and the capacitor  $C_2$  is charged by  $U_{\rm in}$  simultaneously.

- 5) Maximum negative output level -(UC1+UC2) (Stage VIII): in Stage VIII, the switches S1, D2, S4 and S5 are ON, and the total voltage -(UC1+UC2) is applied to the LC output filter. In addition, the capacitor C2 is charged by the input source Uin.

The two split capacitor voltages are self-balanced by the input voltage source  $U_{in}$ , i.e.:

$$U_{C1} = U_{C2} = U_{in} \tag{3}$$

# III. PS-PWM METHOD

For a multilevel inverter, the logic relationship among the drive signals of the switches, carrier signals and modulation signals should be achieved before selecting a certain modulation strategy. In the proposed inverter, with three pairs of complementary switches, it is only necessary to determine the logic relation among the drive signals of three switches, carrier signals and modulation signals. In this section, the eight switching combinations in Table I are rewritten in Table II with A, B and C to generate a five-level voltage waveform.

TABLE II TRUTH TABLE

| Stages | $S_1$ | $S_4$ | $S_6$ | $u_{\mathrm{ab}}$                             | A | В | C |

|--------|-------|-------|-------|-----------------------------------------------|---|---|---|

| I      | 0     | 0     | 1     | $U_{\rm C1} + U_{\rm C2} = 2U_{\rm in}$       | 1 | 1 | 1 |

| II     | 0     | 1     | 1     | $U_{ m C2}\!\!=\!\!U_{ m in}$                 | 1 | 1 | 0 |

| III    | 1     | 0     | 1     | $U_{ m in}$                                   | 1 | 0 | 1 |

| IV     | 1     | 1     | 1     | 0                                             | 1 | 0 | 0 |

| V      | 0     | 0     | 0     | 0                                             | 0 | 0 | 0 |

| VI     | 0     | 1     | 0     | - $U_{ m in}$                                 | 0 | 0 | 1 |

| VII    | 1     | 0     | 0     | $-U_{\rm C1} = -U_{\rm in}$                   | 0 | 1 | 0 |

| VIII   | 1     | 1     | 0     | $-U_{\rm C1}$ - $U_{\rm C2}$ =-2 $U_{\rm in}$ | 0 | 1 | 1 |

| AB    | C<br>00 | 01 | 11 | 10 |  |  |  |  |  |

|-------|---------|----|----|----|--|--|--|--|--|

| 0     | 0       | 0  |    | 1  |  |  |  |  |  |

| 1     | 1       | 1  | 0  | 0  |  |  |  |  |  |

| $S_1$ |         |    |    |    |  |  |  |  |  |

| V B   | 00      | 01 | 11 | 10 |  |  |  |  |  |

| 0     | 0       |    |    | 0  |  |  |  |  |  |

| 1     |         | 0  | 0  |    |  |  |  |  |  |

| BC S4 |         |    |    |    |  |  |  |  |  |

| A     | 00      | 01 | 11 | 10 |  |  |  |  |  |

| 0     | 0       | 0  | О  | 0  |  |  |  |  |  |

| 1     |         | 1  | 1  |    |  |  |  |  |  |

|       |         | S  | 6  |    |  |  |  |  |  |

Fig. 3. Karnaugh maps for  $S_1$ ,  $S_4$  and  $S_6$ .

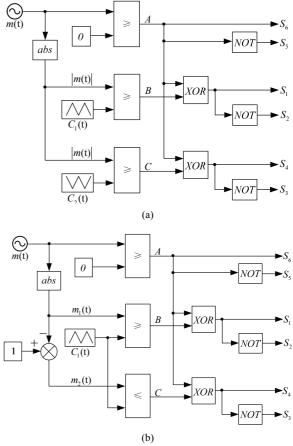

A, B and C represent the outputs of the three comparators, which are also given in Fig. 5.

To determine the relations among A, B and C and  $S_1$ ,  $S_4$  and  $S_6$ , three Karnaugh maps for the switches  $S_1$ ,  $S_4$  and  $S_6$  are presented in Fig. 3. According to Fig. 3, it is not difficult to obtain the logic relations shown in (4). The next step is to select a modulation strategy for the inverter.

$$\begin{cases} S_1 = A\overline{B} + \overline{A}B = A \oplus B \\ S_4 = A\overline{C} + \overline{A}C = A \oplus C \\ S_6 = A \end{cases} \tag{4}$$

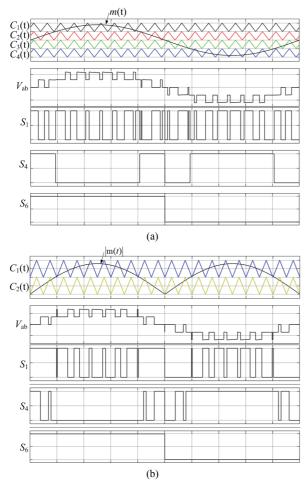

For a multilevel inverter, carrier-based phase disposition pulse width modulation (PD-PWM) is a common strategy. As shown in Fig. 4(a), the PD-PWM strategy is implemented by using four triangular carriers and one reference signal. Four carriers with the same frequency, amplitude and phase angle are disposed as the upper and lower four layers, labelled as  $C_1(t)$ ,  $C_2(t)$ ,  $C_3(t)$  and  $C_4(t)$ , which are symmetrically distributed in the two-side of the horizontal axis, and compared with a sine modulation wave m(t). However, it is difficult to produce so many triangular carriers with the phase disposition in a DSP control board. In addition, a lot of

Fig. 4. Switching patterns of PD-PWM strategies: (a) Conventional PD-PWM; (b) Optimal PD-PWM.

triangular carriers drain the computing resources of the DSP. Therefore, it is desirable to take a modulation strategy with a reduced number of triangular carriers that can achieve the same or much better output performance than the conventional PD-PWM strategy.

Referring to the modulation strategy in [17], [21], an optimal PD-PWM strategy with only two triangular carriers can be used to generate switching signals for the proposed inverter. The switching patterns of the inverter with the optimal PD-PWM strategy are presented in Fig. 4(b), where the two triangular carrier signals  $C_1(t)$  and  $C_2(t)$  have the same frequency, amplitude, and phase angle. The same output performance as the conventional PD-PWM can be achieved. However, it is still difficult to produce two triangular carriers with phase disposition in a DSP control board.

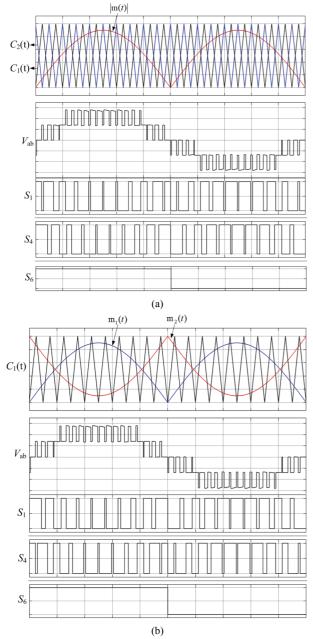

Another interesting strategy is phase-shifted pulse width modulation (PS-PWM) and its logic relation, shown in Fig. 5(a), is similar to that in the optimal PD-PWM. A small difference between them is that the two triangular carriers  $C_1(t)$  and  $C_2(t)$  in the PS-PWM strategy are phase-shifted 180 degrees instead of phase disposition. In Fig. 5(a), the

Fig. 5. Modulation logic diagram of PD-PWM strategies: (a) Conventional PS-PWM; (b) Proposed PS-PWM.

reference sinewave m(t) is used to compare with zero for zero-crossing detection and for providing the line frequency switching signals for  $S_5$  and  $S_6$ . The absolute value of the sinewave |m(t)| is used for comparison with the triangular carrier signals  $C_1(t)$  and  $C_2(t)$  to provide switching signals for the other four switches  $S_1$ - $S_4$ .

Producing two phase-shifted triangular carriers is a lot easier than producing two carriers with phase disposition in a DSP control board system. The switching patterns of an inverter with the conventional PS-PWM strategy was given in Fig. 6. By comparing Fig. 5(a) and Fig. 6(a), it can be found that the equivalent switching frequency of the output voltage using the PS-PWM strategy is two times that using the PD-PWM strategy or the optimal PD-PWM strategy. As a result, the output harmonic component can be largely reduced and the output filter can be designed with a smaller size by using the PS-PWM strategy. That is why the PS-PWM strategy is widely used in power converters.

In this paper, a new PS-PWM strategy is proposed using only one triangular carrier  $C_1(t)$  as shown in Fig. 5(b). In addition, its switching patterns are given in Fig. 6(b). Like the conventional PS-PWM strategy, the drive signals of  $S_1$  and  $S_4$  are phase-shifted 180 degrees. The same output performance as the conventional PS-PWM strategy can be achieved with

Fig. 6. Switching patterns of PS-PWM strategies: (a) Conventional PS-PWM; (b) Proposed PS-PWM.

one carrier reduced, which makes it a lot easier to implement in a DSP control board system. In the proposed PS-PWM strategy, the two reference waves  $m_1(t)$  and  $m_2(t)$  given in (5) are needed and it can be considered that  $m_2(t)$  is achieved by rotating  $m_1(t)$  180 degrees. It is easy to produce  $m_1(t)$  and  $m_2(t)$  in a DSP control board.

$$\begin{cases}

m_1(t) = |m(t)| \\

m_2(t) = 1 - |m(t)|

\end{cases}$$

(5)

In the proposed PS-PWM modulation strategy, the triangular carrier  $C_1(t)$  is used for comparison with  $m_1(t)$  and  $m_2(t)$  to generate the switching signals for  $S_1$  and  $S_4$ . Unlike

Fig. 7. Equivalent circuits of the switched-diode-capacitor cell: (a)  $S_1$  is on,  $S_2$  is off; (b)  $S_1$  is off,  $S_2$  is on.

the conventional PS-PWM strategy, the comparing logic for obtaining C (i.e., the output of the third comparator in Fig. 5(b)) in the proposed PS-PWM strategy is contrary to that of the conventional PS-PWM strategy. The second triangular carrier  $C_2(t)$  is not necessary in the proposed PS-PWM strategy. On the whole, the proposed PS-PWM strategy is easier to implement while guaranteeing the same inverter performance as the conventional PS-PWM strategy.

## IV. PERFORMANCE ANALYSIS

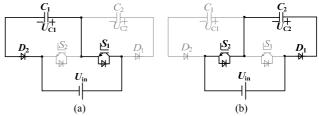

## A. Integration of Self-Balanced and Step-Up Function

It is easy to show that the two capacitors  $C_1$  and  $C_2$  are charged and discharged, as reported in [18]-[20]. Equivalent circuits of the switched-diode-capacitor network are presented in Fig. 7. It can be seen that when the switch  $S_1$  is on, the capacitor  $C_2$  is charged by the input source  $U_{in}$ through the diode  $D_2$ . It can also be seen that when  $S_2$  is on, the capacitor  $C_1$  is charged by the input source  $U_{in}$  through the diode  $D_1$ . Considering the voltage drops of the diodes,  $C_1$  is charged at  $U_{\text{in}}$ - $U_{\text{D1}}$  and  $C_2$  is charged at  $U_{\text{in}}$ - $U_{\text{D2}}$ . In the proposed topology, the two diodes  $D_1$  and  $D_2$  have the same characteristics and they are the same kind of diode in the experiment. Thus, the difference between  $U_{D1}$  and  $U_{D2}$  is very small even when considering practical parasitic parameters. In addition, the difference between  $C_1$  and  $C_2$  only influences their voltage ripples but does not influence their average voltages. Therefore, there is no need to consider the neutralpoint potential issue in this five-level inverter. Since there are idle states of the two capacitors, enough capacitance is provided to ensure stable capacitor voltages.

Considering that the reference wave m(t) is equal to  $m\sin(2\pi f_m t)$ , the output voltage  $u_0$  (RMS value) can be expressed as follows:

$$u_o = (U_{C1} + U_{C2}) * m \sin(2\pi f_m t) / \sqrt{2} = \sqrt{2} m U_{in} \sin(2\pi f_m t)$$

(6)

Where  $f_m$  is the line frequency and m is the modulation index that is expressed by:

$$m = \frac{A_m}{2A_c} \tag{7}$$

Therefore, the step-up ratio of the inverter can be defined as:

$$\frac{u_o}{U_{in}} = \sqrt{2m}\sin(2\pi f_m t) \tag{8}$$

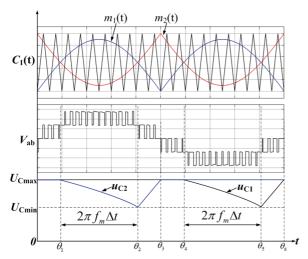

Fig. 8. Capacitor voltages during one fundamental period.

It can be concluded from (8) that the proposed inverter has step-up capacity and that the step-up ratio is two times that of the conventional single-phase two-level inverter.

## B. Loss Analysis

According to the theoretical analysis above, the two switches  $S_5$  and  $S_6$  experience voltage stresses equaling to  $2U_{\rm in}$  while the other four switches  $S_1$ - $S_4$  experience voltage stresses equal to  $U_{\rm in}$ . In addition, a great advantage of the proposed topology is a self-balancing function for capacitor voltages. As shown in Table II and Fig. 2, the two capacitors  $C_1$  and  $C_2$  are charged and discharged for the same period during a whole fundamental switching cycle. As a result, the two capacitor voltages are self-balanced. Meanwhile, a two-time step-up ratio is achieved.

When the modulation index m is less than or equal to 1/2, the inverter outputs three voltage levels while the two capacitors  $C_1$  and  $C_2$  are kept idle under this condition. When m is over 1/2, the capacitor voltage waveform during one fundamental period is presented in Fig. 8, in which there is:

$$\theta_{1} = \sin^{-1}(A_{c} / A_{m})$$

$$\theta_{2} = \pi - \sin^{-1}(A_{c} / A_{m})$$

$$\theta_{3} = \pi$$

$$\theta_{4} = \pi + \sin^{-1}(A_{c} / A_{m})$$

$$\theta_{5} = 2\pi - \sin^{-1}(A_{c} / A_{m})$$

$$\theta_{6} = 2\pi$$

$$(9)$$

Thus, the time period  $\Delta t$  in which the voltage of  $C_1$  or  $C_2$  decreases can be expressed as follows:

$$2\pi f_m \Delta t = \theta_2 - \theta_1 \tag{10}$$

According to (7), (9) and (10),  $\Delta t$  can be obtained by:

$$\Delta t = \frac{1}{2f_m} - \frac{\sin^{-1}(1/(2m))}{\pi f_m} \tag{11}$$

Therefore, the voltage across  $C_1$  or  $C_2$  can be obtained by:

$$u_c = U_{C \text{max}} e^{-\frac{2t}{RC}}, 0 < t < \Delta t$$

(12)

Where R and C are the output load and the capacitance of  $C_1$  and  $C_2$ . It can be concluded from Fig. 2 that the capacitor  $C_1$  is charged when  $S_2$  and  $D_1$  are turned on, and that the capacitor  $C_2$  is charged when  $S_1$  and  $D_2$  are turned on. For simplicity, the diodes  $D_1$  and  $D_2$  are assumed to have a voltage drop of  $U_D$ . By ignoring the on-state resistance of the power switches and parasitic resistors in the circuit, the maximum capacitor voltage across  $C_1$  and  $C_2$  can be calculated as follows:

$$U_{C\max} = U_{in} - U_{D} \tag{13}$$

Therefore, as shown in Fig. 9, the capacitor voltages of  $C_1$  and  $C_2$  can be calculated by:

$$u_c = (U_{in} - U_D) e^{-\frac{2t}{RC}}, 0 < t < \Delta t$$

(14)

In addition, the voltage ripple of  $C_1$  or  $C_2$  can be estimated based on (11) and (14).

$$\Delta u_c = U_{C_{\text{max}}} - U_{C_{\text{min}}} = (U_{in} - U_{D})(1 - e^{\frac{2\sin^{-1}(1/(2m))}{\pi f_m RC} - \frac{1}{f_m RC}}) \quad (15)$$

It can be seen from (15) that the voltage variation of the capacitor is related to the fundamental frequency  $f_m$ , modulation index m, output load R and capacitance C.

For switched-capacitor inverters, there are three types of power losses, including switching losses, conduction losses and capacitor distribution losses. In capacitor charging or discharging cycles, capacitor distribution losses are produced due to the voltage difference between the capacitors. Reference [22] indicates that the distribution losses are directly proportional to the capacitance and the capacitor voltage ripple. Thus, the capacitor distribution losses can be estimated by:

$$P_{dis} = f_s * \frac{1}{2} C (\frac{\Delta u_c}{2})^2 * 2 = \frac{1}{4} f_s C \Delta u_c^2$$

(16)

Where  $f_s$  is the switching frequency.

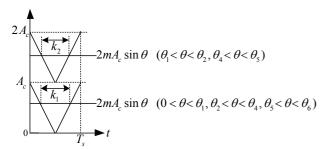

The conduction loss is caused by the parasitic parameters, including the on-state resistances of the switches and the forward voltage drops of the diodes. For the main power circuit with a load R, there are two different conduction paths. Fig. 9 shows the switching states according to their relative position between the modulation signal and the carrier signal during one switching period  $T_s$ . Since  $T_s$  is much shorter than the fundamental period, the modulation signal can be deemed as a straight horizontal line during  $T_s$ . In this way, the on-state ratio  $k_1$  in the operating states of Fig. 2(b)-(g), and the on-state ratio  $k_2$  in the operating states of Fig. 2(a) and Fig. 2(h), can be obtained.

$$\frac{2mA_{c}\sin\theta}{A_{c}-0} = \frac{k_{1}T_{s}}{T_{s}} \Rightarrow k_{1} = 2m\sin\theta \left(0 < \theta < \theta_{1}, \theta_{2} < \theta < \theta_{4}, \theta_{5} < \theta < \theta_{6}\right) \quad (17)$$

$$\frac{2mA_c\sin\theta - A_c}{2A_c - A_c} = \frac{k_2T_s}{T_s} \Rightarrow k_2 = 2m\sin\theta - 1 \ (\theta_1 < \theta < \theta_2, \theta_4 < \theta < \theta_5)$$

(18)

Fig. 9. Switching states according to the relative position between the modulation signal and the carrier signal during  $T_s$ .

For the operating states of Fig. 2(b), (c), (f) and (g), three switches are conducted with the conduction loss:

$$P_{con_{-1}} = \frac{1}{\pi} \left( \int_{0}^{\theta_{1}} d\theta + \int_{\theta_{2}}^{\theta_{4}} d\theta + \int_{\theta_{5}}^{\theta_{6}} d\theta \right) * \left( \frac{U_{in} - u_{ab}}{3r_{on} + R} \right)^{2} * 3r_{on} * k_{1}$$

(19)

For the operating states of Fig. 2(a) and Fig. 2(h), two switches and one diode are conducted, and the conduction loss can be calculated by:

$$P_{con_{2}} = \frac{1}{\pi} \left( \int_{\theta_{1}}^{\theta_{2}} d\theta + \int_{\theta_{4}}^{\theta_{5}} d\theta \right) * \left[ \left( \frac{2U_{in} - u_{ab}}{2r_{on} + R} \right)^{2} * 2r_{on} + \frac{2U_{in} - u_{ab}}{2r_{on} + R} U_{D} \right] * k_{2}$$

(20)

According to (17)-(20), the total conduction losses of the proposed inverter can be calculated by:

$$P_{con} = P_{con_{-1}} + P_{con_{-2}} = \frac{1}{\pi} \left[ \left( \frac{U_{in} - u_{cb}}{3r_{cn} + R} \right)^{2} * 24mr_{cn} * (1 - \sqrt{1 - \frac{1}{4m^{2}}}) + \left( \frac{1}{4m^{2}} - \pi + 2\sin^{-1}(\frac{1}{2m}) \right] * \left[ \left( \frac{2U_{in} - u_{cb}}{2r_{cn} + R} \right)^{2} * 4r_{cn} + \frac{2U_{in} - u_{cb}}{2r_{cn} + R} * U_{D} \right]$$

$$(21)$$

The switching loss can be estimated from the charging and discharging processes of the parasitic capacitance between the drain terminal and the source terminal. Due to the phase-shift modulation, the equivalent switching frequency is doubled. Thus, the switching loss can be estimated by:

$$P_{sw} = 2f_s * C_{ds}V_b^2 (22)$$

Where  $C_{\rm ds}$  and  $V_{\rm b}$  are the parasitic capacitance and the maximum block voltage of each switch. The block voltages of  $S_1$ - $S_4$  are all equal to  $U_{\rm in}$ , and the block voltages of  $S_5$  and  $S_6$  are equal to  $2U_{\rm in}$ . Therefore, the total switching loss of the proposed inverter can be calculated by:

$$P_{sw} = 2[f_s * C_{k1} * 4 * U_{in}^2 + f_m * C_{k2} * 2 * (2U_{in})^2] = (8f_s C_{k1} + 16f_m C_{k2})U_{in}^2$$

(23)

Where  $C_{ds1}$  is the parasitic capacitance of  $S_1$ - $S_4$  and  $C_{ds2}$  denotes the parasitic capacitance of  $S_5$ - $S_6$ . Finally, the total power losses of the proposed inverter can be calculated by:

$$P_{total} = P_{dis} + P_{con} + P_{sw} \tag{24}$$

# C. Comparative Analysis

As previously mentioned, many single-phase five-level inverter topologies have been proposed. In this section, Table III summarizes comparisons between popular five-level inverters and the proposed inverter. In Table III, *S, D, C* and

L represent the quantities of the switches, diodes, capacitors, and inductors used in the topologies. It can be observed that only five active switches are needed and that four diodes are added for the inverters reported in [7]-[10], which may increase the conduction losses of the inverters. The topology in [14], [15] has the lowest number of power components. However, two split dc sources are necessary, which greatly limits its application. A new hybrid five-level inverter was developed in [16] without clamped diodes or capacitors. The topology is simple with only six power switches. When compared with the hybrid five-level inverter, two more diodes are needed in the proposed inverter. However, under the same output voltage conditions, only two power switches in the proposed inverter bear a high voltage stress while four power switches in the inverter of [16] bear a high voltage stress. Moreover, only  $U_{C2}$  in the topology of [16] helps contribute to achieving the two voltage levels  $+0.5U_{\rm in}$  and  $-0.5U_{\rm in}$ , while  $U_{\rm C1}$  remains idle expect for contributing to achieving the two voltage levels  $U_{\rm in}$  and  $-U_{\rm in}$  together with  $U_{\rm C2}$ . This is the basic reason for an imbalanced potential issue, and a voltage-balance control strategy is necessary. However, this issue does not exist in the proposed five-level inverter because both  $U_{C1}$  and  $U_{C2}$  in the proposed topology help in achieving the two voltage levels  $+0.5U_{in}$  and  $-0.5U_{in}$ . The two capacitor voltages are self-balanced during the modulation process. Therefore, there is no need to consider voltagebalance control strategies for the proposed topology.

All of these topologies, except the topology in [17] and the proposed topology in this paper, have a common neutralpoint potential imbalance issue. The modulation strategies of these topologies should accurately balance the charging time for each of the capacitors for realizing the voltage-balance goal. However, this makes the modulation strategies more complicated. On the other hand, neutral-point potential imbalance is not an issue for the topology in [17] or the proposed topology due to the self-balanced function of the switched-diode-capacitor cell. The integration of the front step-up circuit and the back inversion circuit in [17] is a good advantage. However, it results in a complicated modulation scheme since the step-up function and inversion function should be considered simultaneously. Moreover, the proposed inverter in this paper has one less inductor and one less diode when compared with the topology in [17]. The proposed PS-PWM strategy makes it much easier to implement in an actual control system. Hence, the proposed topology is simpler and easier to implement.

On the whole, the double function of dc-dc step-up conversion with a two-time ratio and dc-ac inversion with a simple modulation strategy is realized in the proposed five-level inverter. On the one hand, one dc source with a reduced number of power switches and small voltage stresses are achieved. On the other hand, a new PS-PWM strategy with one carrier is proposed, and it is easy to implement in

| Topology          | S | D | С | L | Source | Step-up | Self-balanced | Modulation  | Phase-Shifted |

|-------------------|---|---|---|---|--------|---------|---------------|-------------|---------------|

| CHB [1, 2]        | 8 | 0 | 0 | 0 | 2      | No      | No            | Simple      | Yes           |

| NPC [4]           | 6 | 2 | 2 | 0 | 1      | No      | No            | Simple      | No            |

| ANPC [5]          | 8 | 0 | 3 | 0 | 1      | No      | No            | Complicated | No            |

| FC [6]            | 6 | 0 | 3 | 0 | 1      | No      | No            | Simple      | No            |

| [7-10]            | 5 | 4 | 2 | 0 | 1      | No      | No            | Simple      | Yes           |

| [14,15]           | 6 | 0 | 0 | 0 | 2      | No      | No            | Simple      | No            |

| [16]              | 6 | 0 | 2 | 0 | 1      | No      | No            | Simple      | No            |

| [17]              | 6 | 3 | 2 | 1 | 1      | Yes     | Yes           | Complicated | No            |

| Proposed inverter | 6 | 2 | 2 | 0 | 1      | Yes     | Yes           | Very Simple | Yes           |

TABLE III COMPARISON ANALYSIS

DSP control board systems. All of these merits make it superior to existing five-level inverters.

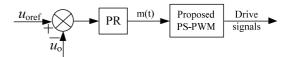

# D. Closed-Loop Control

The closed-loop implementation of the inverter is based on a proportional resonant (PR) controller with a resonant peak at the fundamental frequency 50Hz. An overall block diagram of the control scheme is presented in Fig. 10, and the PR controller structure is given as:

$$G(s) = k_p + \frac{2k_r \omega_c s}{s^2 + 2\omega_c s + \omega_o^2}$$

(25)

Where  $k_p$  is the proportional gain,  $k_r$  is the resonant gain,  $\omega_c$  is the cut-off frequency, and  $\omega_o$  is the fundamental radian frequency. The resonant gain of the PR controller will only integrate frequencies very close to the fundamental frequency and will not introduce stationary error or phase shift [23], [24]. Using the PR controller, reference tracking performance can be enhanced and the known drawback of a PI controller that the steady-state errors in the single-phase system can be alleviated.

According to the bilinear transformation (9) in [25], the expression (8) could be discretized as (10).

$$s = \frac{2}{T} \frac{1 - z^{-1}}{1 + z^{-1}} \tag{26}$$

$$G(z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{a_0 + a_1 z^{-1} + a_2 z^{-2}}$$

(27)

Where 1/T means the control frequency of the PR controller and  $a_0$ ,  $a_1$ ,  $a_2$ ,  $b_0$ ,  $b_1$  and  $b_2$  are:

$$\begin{cases} a_0 = 1 \\ a_1 = \frac{2\omega_0^2 T^2 - 8}{\omega_0^2 T^2 + 4\omega_c T + 4} \\ a_2 = \frac{\omega_0^2 T^2 - 4\omega_c T + 4}{\omega_0^2 T^2 + 4\omega_c T + 4} \\ b_0 = \frac{k_p (\omega_0^2 T^2 + 4\omega_c T + 4) + 4k_r \omega_c T}{\omega_0^2 T^2 + 4\omega_c T + 4} \\ b_1 = k_p a_1 \\ b_2 = \frac{k_p (\omega_0^2 T^2 - 4\omega_c T + 4) - 4k_r \omega_c T}{\omega_0^2 T^2 + 4\omega_c T + 4} \end{cases}$$

$$(28)$$

Fig. 10. Overall block diagram of the control scheme.

Therefore, a difference equation is obtained as follows:

$$u(k) = -\frac{a_1}{a_0}u(k-1) - \frac{a_2}{a_0}u(k-2) + \frac{b_0}{a_0}e(k) + \frac{b_1}{a_0}e(k-1) + \frac{b_2}{a_0}e(k-2)$$

(29)

In expression (29), u(k), u(k-1) and u(k-2) represent the output voltage signals at the moments k, k-1 and k-2. Meanwhile, e(k), e(k-1) and e(k-2) represent the corresponding error signals at the moments k, k-1 and k-2, respectively. The expression (29) can then be programmed into the DSP control board system to realize the PR control for stabilizing the output voltage of the proposed inverter.

## V. EXPERIMENTAL VERIFICATION

To verify the correctness of the proposed topology and modulation method, an experimental prototype with a 150W output power, as shown in Fig. 11, has been built according to the parameters presented at Table IV. The controller is implemented based on a digital signal processor TMS320F28335.

It should be noted that a three-phase LC filter board and a three-phase voltage-current sensor board are presented in the prototype picture. However, a single-phase LC filter and a single voltage sensor are used in the actual prototype. In the PR controller,  $k_p$  is 0.0001,  $k_r$  is 1.0,  $w_c$  is 5rad/s, and  $w_o$  is 314.15. Referring to [26], the inductor  $L_o$  is calculated as:

$$L_o = \frac{U_{in}}{4 * f_o * (\frac{\sqrt{2}P_o}{u_o} * \eta)}$$

(30)

In (30),  $f_0$  means the equivalent switching frequency of the output voltage  $u_{ab}$ ,  $P_0$  means the output power, and  $\eta$  means current ripple percentage. In the experiment,  $\eta$  is selected as 20%. With a switching frequency of 10 kHz, the equivalent switching frequency  $f_0$  of the output voltage  $u_{ab}$  should be 20 kHz due to the PS-PWM strategy. According to the

Fig. 11. Experimental prototype.

## TABLE IV Experimental Parameters

| Components                   | Rated Values |  |  |  |

|------------------------------|--------------|--|--|--|

| Input voltage $U_{\rm in}$   | 60V          |  |  |  |

| Output voltage $u_0$         | 60V          |  |  |  |

| Switching frequency $f_s$    | 10kHz        |  |  |  |

| Line frequency $f_{\rm m}$   | 50Hz         |  |  |  |

| Capacitors $C_1$ , $C_2$     | 470uF        |  |  |  |

| Switches $S_1$ - $S_4$       | IRFP250      |  |  |  |

| Switches $S_5$ , $S_6$       | IRFP450      |  |  |  |

| Diodes $D_1, D_2$            | FFB20UP20STM |  |  |  |

| Inductor $L_{\rm o}$         | 1.0mH        |  |  |  |

| Output capacitor $C_{\rm o}$ | 6.3uF        |  |  |  |

| Driver                       | A3120        |  |  |  |

|                              |              |  |  |  |

experimental parameters and (30), the inductor  $L_0$  is 1.06mH. In the prototype, the inductor is selected as 1.0mH. On the other hand, the cut-off frequency  $f_{\rm cut}$  of the output LC filter is usually regarded as ten percent of the switching frequency of the output voltage  $V_{\rm ab}$ , i.e., 2kHz.

$$f_{cut} = \frac{1}{2\pi\sqrt{L_o C_o}} = 2.0kHz$$

(31)

According to (31), the output capacitor  $C_0$  can be calculated as 6.3 uF. Therefore, the inductance and capacitance of the LC filter are 1.0 mH and 6.3 uF.

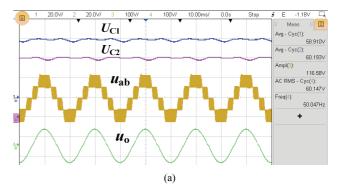

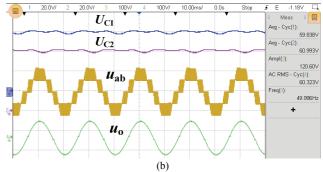

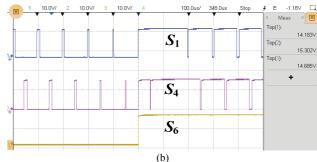

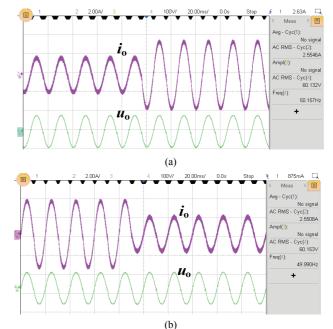

Comparison results of the conventional PS-PWM strategy and the proposed PS-PWM strategy are presented, including the key voltage waveforms in Fig. 12, the drive signals of  $S_1$ ,  $S_4$  and  $S_6$  in Fig. 13, the terminal voltage waveforms of the switches  $S_1$  and  $S_4$ , and the output voltage in Fig. 14. It can be seen from Fig. 12 that the output voltage  $u_{ab}$  presents a five-level shape and that the output voltage  $u_0$  presents a pure sine waveform. In addition, the two capacitor voltages are both nearly 60V, which is equal to the input voltage 60V. This verifies the correctness of the step-up capability and self-balance function. Low frequency capacitor voltage ripples are inevitable due to the charging and discharging of the capacitors. The drive signals of the switches in Fig. 13 show that the switches  $S_1$  and  $S_4$  have a 180 degrees difference in phase, which verifies the correctness of the proposed PS-PWM strategy. In Fig. 14, the output voltage is composed of a 20 kHz PWM voltage signal, which is two

Fig. 12. Key voltage waveforms: (a) Conventional PS-PWM; (b) Proposed PS-PWM.

Fig. 13. Drive signals: (a) Conventional PS-PWM; (b) Proposed PS-PWM.

times of the switching frequency of  $S_1$  and  $S_4$ . All of the comparison results in Figs. 12-14 verify the proposed PS-PWM strategy.

By comparing experimental results under the two different PS-PWM modulation strategies, it can be concluded that the proposed PS-PWM strategy has output performance equivalent to that of the conventional PS-PWM strategy. Thus, it can be

Fig. 14. Terminal voltage waveforms of  $S_1$ ,  $S_4$ , and the output voltage: (a) Conventional PS-PWM; (b) Proposed PS-PWM.

Fig. 15. Voltage waveforms of switches and diodes under the proposed modulation strategy: (a)  $D_1$ ,  $S_1$ ,  $S_2$ ,  $D_2$ ; (b)  $S_3$ ,  $S_4$ ,  $S_5$ ,  $S_6$ .

claimed that the proposed PS-PWM strategy is equivalent to the conventional PS-PWM strategy in terms of inverter output performance. Since one triangular carrier is reduced, the proposed PS-PWM strategy is better than the conventional PS-PWM strategy in actual implementation. In fact, the proposed PS-PWM strategy can be used or extended to other

Fig. 16. Dynamic results under a load step.

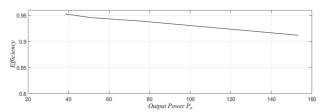

Fig. 17. Conversion efficiency curve.

power converter systems, such as a multi-phase dc/dc converter systems, cascaded multilevel converters, and modular multilevel converters. With the proposed PS-PWM strategy, half carriers can be saved and it becomes a lot easier to implement in a DSP.

Apart from the analysis mentioned above, it can be seen from Fig. 15 that all of the power components besides  $S_5$  and  $S_6$  endure half of the peak value of the output voltage. Although  $S_5$  and  $S_6$  endure the output peak voltage, the switching frequency for each of the switches is equal to the line frequency, which does not cause high switching losses. Moreover, the dynamic results of the inverter under a load step from 47 ohm to 23.5 ohm or vice versa are also given in Fig. 16. It can be seen that the output voltage is kept stable under the load step, and that the output current  $i_0$  increases by two times or half of its original value during a very short time, which indicates a very good dynamic response of the inverter.

Finally, the conversion efficiency of the inverter is presented in Fig. 17. The conversion efficiency of the inverter is over 95.27% at a light load and 91.19% at a full load (i.e., 23.5 ohm for the 150W power rating). As shown in Fig. 12, the voltage ripple  $\Delta u_c$  of  $C_1$  or  $C_2$  is around 3.0V. The parasitic capacitance  $C_{\rm ds1}$  of the switches  $S_1$ - $S_4$  (IRFP250) is 530pf, and the parasitic capacitance  $C_{\rm ds2}$  of the switches  $S_5$ - $S_6$

(IRFP450) is 380pf. In addition, the conduction resistance of  $S_1$ - $S_4$  (IRFP250) is 0.085ohm, and the conduction resistance of  $S_5$ - $S_6$  (IRFP450) is 0.4ohm. The equivalent series resistance of  $C_1$  or  $C_2$  is 0.1ohm. Based on the parameters and the formulas (16), (21) and (23), the capacitor distribution loss, conduction loss and switching loss of the proposed inverter with a full power load are calculated as 8.58W, 4.26W and 0.16W. It can be found that the capacitor distribution loss dominates the total power loss, while the switching loss is the lowest. The conversion efficiency of the proposed inverter with a full load is 91.33%, which basically matches its tested value of 91.19%.

## VI. CONCLUSION

A single-phase step-up five-level inverter has been proposed and implemented with a new PS-PWM strategy in this paper. The operating principle and performance analysis show that a double step-up ratio, reduced number of power devices and self-balanced capacitor voltages are achieved in the proposed inverter topology. Furthermore, the proposed PS-PWM strategy is equivalent to the conventional PS-PWM strategy with one less carrier, which makes it much easier to implement in a DSP control board system. The proposed PS-PWM strategy provides a new idea for implementing phase-shifted modulations and can be extended to other power converters. The PR control method was utilized to realize closed loop control for the output voltage of the proposed inverter.

#### ACKNOWLEDGMENT

This work was partially supported by China Postdoctoral Science Foundation under grant number 2017M612908 and partially supported by NSFC under award # U1609216.

#### REFERENCES

- [1] M. Calais, V. G. Agelidis, L. J. Borle, and M. S. Dymond, "A transformerless five level cascaded inverter based single phase photovoltaic system," *IEEE 31st Annual Power Electronics Specialists Conference*, pp. 1173-1178, 2000.

- [2] M. Calais, L. J. Borle, and V. G. Agelidis, "Analysis of multicarrier PWM strategies for a single-phase five level inverter," *IEEE 32nd Annual Power Electronics Specialists Conference*, pp. 1351-1356, 2001.

- [3] A. Ghazanfari, H. Mokhtari, and M. Firouzi, "Simple Voltage balancing approach for CHB multilevel inverter considering low harmonic content based on a hybrid optimal modulation strategy," *IEEE Trans. Power Del.*, Vol. 27, No. 4, pp. 2150-2158, Oct. 2012.

- [4] S. Iturriaga-Medina, C. A. Limones-Pozos, P. R. Martinez-Rodriguez, G. Escobar, J. M. Sosa, A. A. Valdez-Fernandez, and J. F. Martinez-Garcia, "A Comparative analysis of grid-tied single-phase transformerless five-level NPC-based inverters for photovoltaic applications," 13th International Conference on Power Electronics (CIEP), pp. 323-328, 2016.

- [5] H. R. Teymour, D. Sutanto, K. M. Muttaqi, and P. Ciufo, "A novel modulation technique and a new balancing control strategy for a single-phase five-level ANPC converter," *IEEE Trans. Ind. Appl.*, Vol. 51, No. 2, pp. 1215-1227, Mar. 2015

- [6] Y. Zhang and L. Sun, "An efficient control strategy for a five-level inverter comprising flying-capacitor asymmetric H-bridge," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 9, pp. 4000-4009, Sep. 2011.

- [7] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and M. I. Gimenez, "A new simplified multilevel inverter topology for DC-AC conversion," *IEEE Trans. Power Electron.*, Vol. 21, No. 5, pp. 1311-1319, Sep. 2006.

- [8] J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital pi controller," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 1, pp. 149-158, Jan. 2009.

- [9] N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 6, pp. 2111-2123, Jun. 2010

- [10] J. C. Kartick, B. K. Sujit, and K. Suparna, "Dual reference phase shifted pulse width modulation technique for a N-level inverter based grid connected solar photovoltaic system," *IET Renew. Power Gener.*, Vol. 10, No. 7, pp. 928-935, Jul. 2016.

- [11] Z. Li, P. Wang, Y. Li, and F. Gao, "A novel single-phase five-level inverter with coupled inductors," *IEEE Trans. Power Electron.*, Vol. 27, No. 6, pp. 2716-2725, Jun. 2012.

- [12] D. Floricau, E. Floricau, and G. Gateau, "New multilevel converters with coupled inductors: Properties and control," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 12, pp. 5344-5351, Dec. 2011.

- [13] J. Salmon, A. M. Knight, and J. Ewanchuk, "Single-phase multilevel PWM inverter topologies using coupled inductors," *IEEE Trans. Power Electron.*, Vol. 24, No. 5, pp. 1259-1266, May 2009.

- [14] Y. H. Liao and C. M. Lai, "Newly-constructed simplified single-phase multistring multilevel inverter topology for distributed energy resources," *IEEE Trans. Power Electron.*, Vol. 26, No. 9, pp. 2386-2392, Sep. 2011.

- [15] K. K. Gupta and S. Jain, "A novel multilevel inverter based on switched DC sources," *IEEE Trans. Ind. Electron.*, Vol. 61, No. 7, pp. 3269-3278, Jul. 2014.

- [16] F. P. Zeng, G. H. Tan, J. Z. Wang, and Y. C. Ji, "Novel Single-phase five-level voltage-source inverter for he shunt active power filter," *IET Power Electron.*, Vol. 3, No. 4, pp. 480-489, Jul. 2010.

- [17] F. Gao, "An enhanced single-phase step-up five-level inverter,", IEEE Trans. Power Electron., Vol. 31, No. 12, pp. 8024-8030, Dec. 2016.

- [18] S. Hou, J. Chen, T. Sun, and X. Bi, "Multi-input step-up converters based on the switched-diode-capacitor voltage accumulator," *IEEE Trans. Power Electron.*, Vol. 31, No. 1, pp. 381-393, Jan. 2016.

- [19] J. Chen, S. Hou, F. Deng, Z. Chen, and J. Li, "An interleaved five-level boost converter with voltage-balance control," *J. Power Electron.*, Vol. 16, No. 5, pp. 1735-1742, Sep. 2016.

- [20] J. Chen, C. Wang, and J. Li, "An input-parallel-output-series switched-capacitor three-level boost converter with a three-loop control strategy," *Energies*, Vol. 11, No. 10,

- 2631, Oct. 2018.

- [21] J.-S. Choi and F.-S. Kang, "Seven-level PWM inverter employing series-connected capacitors paralleled to a single DC voltage source," *IEEE Trans. Ind. Electron.*, Vol. 62, No. 6, pp. 3448-3459, Jun. 2015.

- [22] K. Zou, "The topology and voltage regulation for highpower switched-capacitor converters," Ohio State University, Phd Dissertation, 2012.

- [23] R. Teodorescu, F. Blaabjerg, M. Liserre, and P. C. Loh, "Proportional-resonant controller and filters for gridconnected voltage-source converters," *IEE Proc.-Electr. Power Appl.*, Vol. 153, No. 5, Sep. 2006.

- [24] N. Zhang, H. Tang, and C. Yao, "A systematic method for designing a PR controller and active damping of the LCL filter for single-phase grid-connected PV inverters," *Energies*, Vol. 7, No. 6, pp. 3934-3954, Jun. 2014.

- [25] F. Groutage, L. Volfson, and A. Schneider, "S-plane to Z-plane mapping using a simultaneous equation algorithm based on the bilinear transformation," *IEEE Trans. Autom. Contr.*, Vol. 32, No. 7, pp. 635-637, Jul. 1987.

- [26] TI Designs: TIDM-HV-1PH-DCAC Voltage Source Inverter Design Guide, Texas Instruments, 1-47, Apr. 2017.

**Jianfei Chen** (S'15-M'17) received his B.S. degree from the Department of Electronic Information, Science and Technology, Chongqing Normal University, Chongqing, China, in 2011; and his Ph.D. degree from the School of Electrical Engineering, Chongqing University, Chongqing, China, in 2016. From January 2015 to March 2016, he

was a visiting Ph.D. student in the Department of Energy Technology, Aalborg University, Aalborg, Denmark. He is presently working as a Postdoctoral Researcher at Wayne State University, Detroit, MI, USA. His current research interests include multilevel converters, motor control and wide bandgap device based power converter design.

Caisheng Wang (S'02 – M'06 – SM'08) received his B.S. and M.S. degrees in Electrical Engineering from Chongqing University, Chongqing, China, in 1994 and 1997, respectively. He received his Ph.D. degree in Electrical Engineering from Montana State University, Bozeman, MT, USA, in 2006. From August 1997 to May

2002, he worked as an Electrical Engineer and then as a Vice Department Chair in the Zhejiang Electric Power Test and Research Institute, Hangzhou, China. Since August 2006, he has been working at Wayne State University, Detroit, MI, USA, where he is presently a Professor in the Department of Electrical and Computer Engineering. His current research interests include the modeling and control of power systems and electric vehicles, energy storage devices, power electronics, distributed generation and microgrids, alternative/hybrid energy power generation systems, and the fault diagnosis and on-line monitoring of electric apparatus. He is an Associate Editor of IEEE Transactions on Smart Grid.

Jian Li (M'05-SM'11) received his M.S. and Ph.D. degrees in Electrical Engineering from Chongqing University, Chongqing, China, in 1997 and 2001, respectively. He is presently working as a Professor and as the Associate Dean of the School of Electrical Engineering at Chongqing University. He is the author or co-author of more than 140 papers published

in journals and conference proceedings. His current research interests include the online condition monitoring and fault diagnosis of HV equipment, environmentally friendly insulation materials and nano dielectrics.