## JPE 15-2-6

http://dx.doi.org/10.6113/JPE.2015.15.2.346 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# An FPGA-Based Modified Adaptive PID Controller for DC/DC Buck Converters

Ling  $Lv^*$ , Changyuan Chang<sup>†</sup>, Zhiqi Zhou<sup>\*</sup>, and Yubo Yuan<sup>\*</sup>

<sup>†\*</sup>School of Integrated Circuits, Southeast University, Nanjing, China

## Abstract

On the basis of the conventional PID control algorithm, a modified adaptive PID (MA-PID) control algorithm is presented to improve the steady-state and dynamic performance of closed-loop systems. The proposed method has a straightforward structure without excessively increasing the complexity and cost. It can adaptively adjust the values of the control parameters ( $K_p$ ,  $K_i$  and  $K_d$ ) by following a new control law. Simulation results show that the line transient response of the MA-PID is better than that of the adaptive digital PID because the differential coefficient  $K_d$  is introduced to changes. In addition, experimental results based on a FPGA indicate that the MA-PID control algorithm reduces the recovery time by 62.5% in response to a 1V line transient, 50% in response to a 500mA load transient, and 23.6% in response to a steady-state deviation, when compared with the conventional PID control algorithm.

Key words: Dynamic performance, FPGA, MA-PID, Steady-state deviation

### I. INTRODUCTION

Digital control for switch-mode power converters (SMPCs) has gained more popularity in a wide range of applications due to its many advantages when compared to analog control, including design flexibility, lower sensitivity, elimination of passive tuning components, programmability, etc.[1]-[3]. For digital SMPCs, the two most important types of performance are the dynamic performance and the static performance. With the rapid development of electronic devices and large-scale digital integrated circuits, power converters are required to have a smaller area and a faster dynamic response.

Many of the classical control schemes for SMPCs have some inherent limitations in the design of the controller that can limit the stability margins, robustness and dynamic performance of a system. However, conventional PID controllers are commonly used in SMPCs due to their simplicity, intuition, and ease of implementation. Recent research trends in the PID control area have been well summarized in many studies. In [4], a Genetic algorithm is applied to discover the supreme values for the PID controller's

Recommended for publication by Associate Editor Se-Kyo Chung.

<sup>†</sup>Corresponding Author: ccyycc@seu.edu.cn

Tel: +86-130-0253-5267, Southeast University

parameters within a short time period. This algorithm has stability robustness, efficiency and optimum dynamic response in a very short time period. An online compensator auto-tuning method which tunes the parameters of the compensator has been proposed to achieve optimized dynamic performance in [5]-[6]. In addition, a fast PID method has been presented in [7]-[9]. In this method, the PID control is divided into two parts, the P control and the I-D control. An 8 bit A-D Converter is used for the P control and an 11 bit A-D Converter is used for the I-D control. However, these methods require relatively complex algorithmic steps to tune the control parameters, or extra software and hardware conditions [10]-[15]. In addition, they may introduce undesirable oscillations in the output. In [11], a novel trajectory prediction control algorithm has been presented. It uses current detection and voltage detection, requiring more than two A/D converters.

In order to overcome the aforementioned limitations, an adaptive digital PID (AD-PID) controller is presented in [15]. This controller reduces the output voltage deviation and settling time by changing the values of the parameters ( $K_p$  and  $K_i$ ). One of the advantages of this method is that it is easy to implement. Nevertheless, this algorithm still has some risks in terms of dynamic performance and static performance. Based on this method, this paper presents a modified adaptive PID (MA-PID) control algorithm. This algorithm tunes the parameters ( $K_p$ ,  $K_i$  and  $K_d$ ) using predetermined rules, such as

Manuscript received Sep. 28, 2014; accepted Dec. 31, 2014

School of Integrated Circuits, Southeast University, Nanjing, China

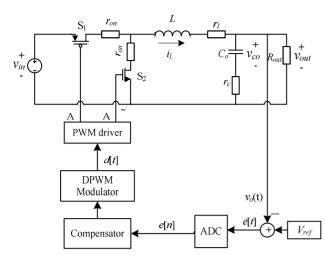

Fig. 1. Block diagram of a power converter with digital controller.

phase margin and gain requirements. The modified algorithm can further improve the dynamic performance (e.g. line transient response). However, it can also effectively eliminate the unstable facts that exit in the literature [15].

The following section introduces the modified adaptive PID control method and algorithm. In addition, it gives a description of the difference between the conventional and MA-PID controls. Section III describes the simulation process of a DC-DC buck converter using MATLAB software, and it presents simulation results. Section IV presents the process of FPGA implementation and an experimental comparison between the conventional PID and MA-PID controllers. Finally, some conclusion are given in section V.

#### II. MA-PID CONTROL TECHNIQUE

#### A. Conventional PID Control Law

An A/D converter, a compensator and a DPWM constitute a feedback loop, with which the power stage forms a closed-loop feedback system, as shown in Fig. 1. The purpose of the closed-loop system is primarily to adjust the output voltage  $V_{out}$  to match a precise and stable voltage reference  $V_{ref}$  over a range of load currents, input voltage values and temperature variations [1].

Based on [16] and [17], a precise mathematical model of the converter can be established under non-ideal conditions. Using a small signal approximation, the open-loop gain function of the original ring without a compensating network can be written as equation (1).

Where  $r_{on}$ ,  $r_l$  and  $r_c$  are the switch-tube on-resistance, the equivalent series resistance of the inductance, and the equivalent series resistance of the capacitance, respectively.

$G_m(s) = 1/U_m$ , and  $U_m$  is the amplitude of the saw-tooth wave.

In [18], the essence of the compensation is to join the calibration device with a suitable frequency characteristic, and to make the shape of the frequency characteristic of the open-loop system into a desire shape, as follows:

- The low-frequency gain is sufficiently large to enhance the steady-state accuracy of the system.

- The slope of the logarithmic amplitude-frequency characteristic in the middle-frequency stage is always -20dB/dec and it occupies a sufficiently wide frequency band, to guarantee that the system has a proper phase margin.

- The higher the cross frequency of the loop gain, the faster the transient response of system will be.

According to the above principles, the transfer function of a digital PID compensator via the s-z transformation can be calculated as:

$$G_{PID}(z) = \frac{U(z)}{E(z)} = K_P + K_I / (1 - Z^{-1}) + K_D (1 - Z^{-1})$$

(2)

Where  $K_p$ ,  $K_i$  and  $K_d$  are the constant coefficients of the proportional gain, integral term, and derivative term, respectively.

### B. Modified Adaptive PID (MA-PID) Control Law

In general, the higher the loop bandwidths which can still guarantee the stability of the system, the better the dynamic performance of the closed-loop system. The theoretical bandwidth have to be under half of the switching frequency. However, the bandwidth of the loop is not more than one-tenth of the switching frequency in practical designs [20]. In the steady state, it may lead to unsteadiness if the bandwidth of a system is more than that limitation. Nevertheless, the dynamic performance can be improved by increasing the proper bandwidth in the transient state, which can be obtained by altering the values of  $K_{p}$ ,  $K_i$  and  $K_d$ .

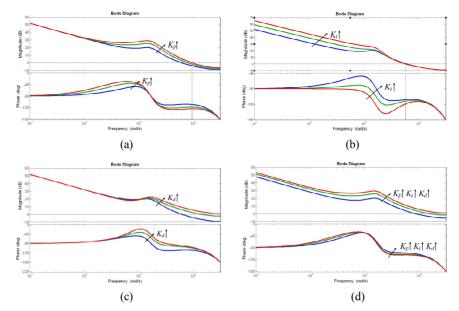

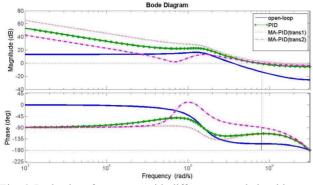

Fig. 2 shows the variation tendencies of the bode-plots for different values of  $K_p$ ,  $K_i$  and  $K_d$ . From Fig. 2(a), it can be seen that as  $K_p$  increases, the bandwidth of the closed-loop system becomes higher and the phase margin decreases. From Fig. 2(b), it can be observed that the gain increases and the phase margin decreases when  $K_i$  increases. From Fig. 2(c), it can be seen that the cross-frequency of the system becomes higher and the phase margin increases as  $K_d$  increases. By comparing Fig. 2(a) and Fig. 2(c), it can be observed that these two parameters  $(K_p \text{ and } K_d)$  are complementary and act as a mutual restraint. Hence, the three parameters should be properly adjusted in order to achieve the desired gain, bandwidth and phase margin requirements. Fig. 2(d) shows the variation tendencies of the bode-plots when  $K_p$ ,  $K_i$  and  $K_d$  increase simultaneously. It can

$$G_{O}(s) = G_{m}(s)G_{d}(s) = \frac{1}{U_{m}} \frac{V_{out}}{D} * \frac{1 + sCr_{C}}{1 + s[\frac{L}{R_{out} + r_{on} + r_{l}} + \frac{CR_{out}(r_{on} + r_{l})}{R_{out} + r_{on} + r_{l}} + Cr_{C}] + s^{2}LC\frac{R_{out} + r_{C}}{R_{out} + r_{on} + r_{l}}$$

(1)

Fig. 2. The variation tendency of bode-plots for different values of  $K_p$ ,  $K_i$  and  $K_d$  (a)  $K_p$  increases. (b)  $K_i$  increases. (c)  $K_d$  increases. (d)  $K_p$ ,  $K_i$  and  $K_d$  increase.

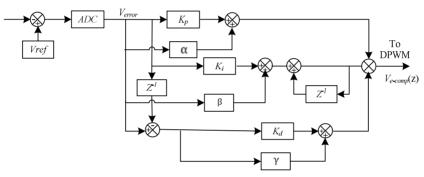

Fig. 3. Adaptively digital PID compensator realization diagram.

be seen from Fig. 2(d) that the compensated system has a proper phase margin, a sufficiently wide frequency band and a sufficiently large low-frequency gain to enhance the steady-state accuracy of the system and improve the transient response.

Therefore, a modified adaptive PID (MA-PID) compensator is proposed. It maintains a lower bandwidth in the steady state to make the system stable and has a higher bandwidth in the transient state, which can make the voltage deviation lower and the recovery time shorter. The transfer function of the MA-PID controller, as shown in Fig. 3, is given by:

$$G_{MA-PID}(z) = (K_p + \alpha) + (K_I + \beta)/(1 - Z^{-1}) + (K_p + \gamma)^*(1 - Z^{-1})$$

(3)

Where  $\alpha$ ,  $\beta$  and  $\gamma$  are adaptively varied following the error signal during the transient state and remain zero in the steady state.

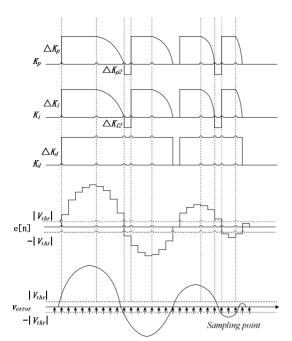

It can be observed from Fig. 4 that the error signal ( $v_{error}$ ) is divided into four states. These states are the rising transient state, falling transient state, transition state and steady state. Once the error signal ( $v_{error}$ ) surpasses the threshold voltage  $V_{thr}$ as a result of a transient, the values of  $\alpha$ ,  $\beta$  and  $\gamma$ , whose values are zero during steady state, are changed abruptly to different values in order to increase the bandwidth and gain of the loop. The MA-PID control algorithm tracks  $v_{error}$  to detect its peak value ( $V_{error-peak}$ ). Once the absolute value of the error signal changes, the values of  $\alpha$ ,  $\beta$  and  $\gamma$  are adjusted as given by (4), (5) and (6).

$$\alpha = \begin{cases} 0, & |v_{error}(k)| < |V_{thr}| \\ \Delta K_{p}, & |v_{error}(k-1)| \le |v_{error}(k)| \\ \frac{|v_{error}(k)|}{|V_{error-peak}|} * \Delta K_{p}, |v_{error}(k-1)| > |v_{error}(k)| \\ \Delta K_{p2}, & v_{error}(k) * v_{error}(k-1) \le 0 \end{cases} |v_{error}(k)| \ge |V_{thr}|$$

$$(4)$$

Fig. 4. Waveforms of MA-PID controller operation.

| DESIGN SPECIFICATION FOR THE BUCK CONVERTER |       |      |  |

|---------------------------------------------|-------|------|--|

| Parameter                                   | Value | Unit |  |

| Input voltage $(V_{in})$                    | 5     | V    |  |

| Output voltage (Vout)                       | 1.8   | V    |  |

| Inductor (L)                                | 4.7   | μΗ   |  |

| Inductor DCR ( <u>r</u> )                   | 200   | mΩ   |  |

| Output capacitor $(C_o)$                    | 10    | μF   |  |

| Capacitor ESR $(r_c)$                       | 100   | mΩ   |  |

| Switching frequency $(f_s)$                 | 1     | MHz  |  |

TABLE I

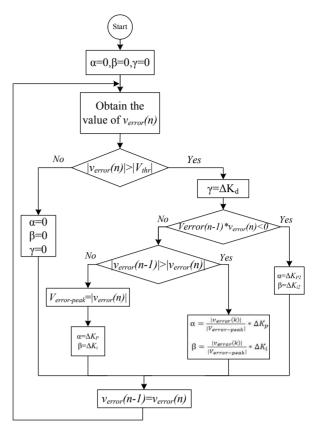

Fig. 5 shows a flowchart of the MA-PID algorithm. It can be seen that the value of  $V_{error-peak}$  is different for different dynamic variations. As in [15],  $V_{error-peak}$  is a variable but not fixed because the ratio of  $v_{error}$  and  $V_{error-peak}$  is not equivalent to one for all transient conditions. In addition, the error signal is handled specially during the transition state to avoid the number of overshoot/undershoot. Thus, the MA-PID control strategy has the ability to adapt and work well under different dynamic types.

Fig. 5. The flowchart of MA-PID algorithm.

## III. SIMULATION PROCESS OF THE DC-DC CONVERTER

#### A. The Selection of Parameters for the Digital Controller

Based on the MATLAB/Simulation platform, the universal model of a DC-DC buck converter can be built in the Simulink environment. The following parameters are taken into account for the model, as shown in Table I.

With the specified parameters, the open-loop gain function of the original ring based on equation (1) can be calculated. Hence, the open-loop gain function, which is translated into z-domain by the zero-order hold, can be given by:

$$G_o(z) = \frac{0.1469z - 0.04947}{z^2 - 1.87z + 0.8911} \tag{7}$$

Equation (7) can be used to design a PID controller. The cross-over frequency of the compensated loop should be

$$\beta = \begin{cases} 0, & |v_{error}(k)| < |V_{thr}| \\ \Delta K_i, & |v_{error}(k-1)| \le |v_{error}(k)| \\ \frac{|v_{error}(k)|}{|V_{error-peak}|} * \Delta K_i, |v_{error}(k-1)| > |v_{error}(k)| \\ \Delta K_{i2}, & v_{error}(k) * v_{error}(k-1) \le 0 \\ \gamma = \begin{cases} 0, & |v_{error}(k)| < |V_{thr}| \\ \Delta K_d, & |v_{error}(k)| \ge |V_{thr}| \end{cases}$$

(6)

Fig. 6. Bode plot of converter with different control algorithms.

about one-tenth of the switching frequency, and the phase margin of the closed-loop system should be approximately 60 degrees [21]. The bode-plot-based technique and the root-locus technique are the common methods which can be operated using MATLAB's Single-Input Single-output (SISO) tool in a trial-and-error process. On the basis of equations (2) and (7), the compensated loop can be achieved by means of the above techniques whose cross-over frequency and phase margin meet the requirements. By adjustment and observation, the transfer function of the PID compensator is obtained as follows:

$$G_{C}(z) = 2 + \frac{0.1}{1 - Z^{-1}} + 4(1 - Z^{-1})$$

(8)

Hence, the parameters of the PID controller are as follows:  $K_p=2$ ,  $K_i=0.1$ , and  $K_d=4$ . Fig. 6 shows a bode plot of uncompensated and compensated closed-loop systems. It can be observed from Fig. 6 that the cross-over frequency of the compensated system is 114 kHz and that the phase margin is 65 degrees.

The parameters of the controller should be optimized to achieve a preferable dynamic response. Thus, the MA-PID control strategy is presented which smoothly transitions the PID parameters between steady state values and dynamic state values.

In order to obtain  $\Delta K_p$ ,  $\Delta K_i$  and  $\Delta K_d$ , the parameters during the steady state should be adjusted until the original bandwidth is increased to approximately one-fifth of the switching frequency and the low-frequency loop gain is increased by 10%~30%. Therefore,  $\Delta K_p$ ,  $\Delta K_i$  and  $\Delta K_d$  are the differences between the correspondingly newfound values and original values, respectively.

Based on the conventional PID parameters and the above design guidelines, the MA-PID parameters can be calculated. As a result,  $\Delta K_p=0.7$ ,  $\Delta K_i=0.3$ ,  $\Delta K_d=2.3$ ,  $\Delta K_{p2}=-1.8$ ,  $\Delta K_{i2}=-0.02$  and  $V_{thr}$  =60mV. When compared with the conventional PID controller, the MA-PID controller possesses an additional 9% bandwidth and a 23% increase in the low-frequency gain. Table II indicates the values of the parameters in the design example.

TABLE II

| VALUES OF THE PARAMETERS IN THE | DESIGN EXAMPLE |

|---------------------------------|----------------|

|---------------------------------|----------------|

| State  | Para.           | Values | GBW   | Low-freq. | Phase  |  |

|--------|-----------------|--------|-------|-----------|--------|--|

|        | raia. values    |        | (kHz) | Gain (dB) | margin |  |

|        | $K_p$           | 2      |       | 53.3      | 65°    |  |

| Steady | K <sub>i</sub>  | 0.1    | 114   |           |        |  |

|        | K <sub>d</sub>  | 4      |       |           |        |  |

| Trans  | $\Delta K_p$    | 0.7    |       | 65.3      | 61°    |  |

|        | $\Delta K_i$    | 0.3    | 202   |           |        |  |

|        | $\Delta K_d$    | 2.3    |       |           |        |  |

|        | $\Delta K_{p2}$ | -1.8   | 120   | 42.8      | 88°    |  |

|        | $\Delta K_{i2}$ | -0.07  | 120   | 42.0      |        |  |

| TABLE III                              |

|----------------------------------------|

| CONVENTIONAL PID ALGORITHM DESCRIPTION |

|                                        |

| Step | Equation                                                            |

|------|---------------------------------------------------------------------|

|      | Initialization:                                                     |

|      | $v_{error}(k) = v_{error}(k-1) = v_{error}(k-2)=0, u(k) = u(k-1)=0$ |

| 1    | $V_{oNow} = V_{ADC}$                                                |

| 2    | $v_{error}(k-2) = v_{error}(k-1), v_{error}(k-1) = v_{error}(k),$   |

| 2    | $v_{error}(\mathbf{k}) = V_{oNow}$ , Flag = 1                       |

| 3    | If Flag=1, then $K_p=2, K_i=0.1, K_d=4$                             |

|      | $P=K_p*[v_{error}(\mathbf{k}) - v_{error}(\mathbf{k}-1)]$           |

| 4    | $I = K_i * v_{error}(k)$                                            |

|      | $D=K_d*[v_{error}(k)-2*v_{error}(k-1)+v_{error}(k-2)]$              |

| 5    | u(k)=u(k-1)+P+I+D Flag=0                                            |

| 6    | If Flag=0, repeat for step 1                                        |

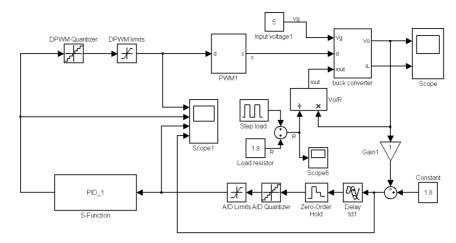

#### B. The Establishment of a Simulation Model

Fig. 7 shows a MALAB/Simulink system model, which consists of an A/D converter, a compensator, a digital pulse width modulator and a power stage. The A/D converter is composed by delay, sample and hold, quantization and saturation blocks. Then, the DPWM module contains quantization, a limit block and a pulse width modulator which can generate the constant-frequency duty ratio signal to control the switch-tube. Buck converter block denotes the power stage which is realized by the state space averaging method, and can change the load resistor in order to simulate a transient response. The dynamic characteristics of the controller are reflected by applying a reduplicative step change in the load, which leads to a load current change.

As shown in Fig. 7, the compensator can be implemented by S-function code. S-function is a computer language to describe dynamic systems which can interact with the Simulink equation solver. As a rule, the algorithm is shown as:

$$u(k) = u(k-1) + K_{p}[e(k) - e(k-1)] + K_{I}e(k) + K_{p}[e(k) - 2e(k-1) + e(k-2)]$$

(9)

From equation (9), it can be seen that the controller just needs the current (e(k)), previous (i.e. e(k-1), e(k-2)) samples of the error signal and previous values of the control output (u(k-1)). Table III shows the operational process of the conventional PID algorithm.

Fig. 7. MATLAB/Simulink model of a buck converter with a digital controller.

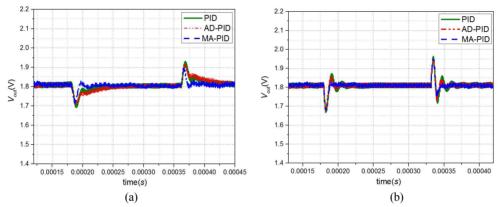

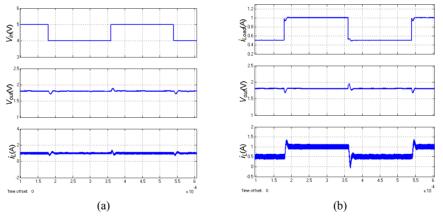

Fig. 8. Comparison of transient response between PID, AD-PID and MA-PID. (a) Input voltage charge between 4V and 5V. (b) Load charge between 0.5A and 1A.

Fig. 9. Transient simulation of the proposed MA-PID controller. Simulated (a) line transient response, (b) load transient response, top-to-bottom: input voltage, output voltage, inductor current.

For simulations of the PID and MA-PID architecture, the parameters  $K_p$ ,  $K_i$  and  $K_d$  should use the corresponding specific values. For example, equation (9) can be rewritten for the MA-PID architecture as:

$$u(k) = u(k-1) + (K_{p} + \alpha)[e(k) - e(k-1)] + (K_{I} + \beta)e(k) + (K_{p} + \gamma)[e(k) - 2e(k-1) + e(k-2)]$$

(10)

The transient response of the designed converter is shown in

Fig. 8 in order to compare the PID control, the AD-PID control and the MA-PID control. The load transient response is simulated by producing a 500mA step in the Load. The line transient response is simulated with an input voltage change from 4V to 5V. It can be seen that there are no additional oscillations or ringing during the MA-PID operation, and that the MA-PID algorithm has a better line transient response than the AD-PID algorithm. Fig. 9 shows the simulated line and

Fig. 10. HDL block for synthesized on the FPGA.

load transient responses with the MA-PID controller. Table IV summarizes the comparison results of the simulation recovery time. It can be observed that the MA-PID control algorithm reduces the recovery time by  $25\mu$ s (>60%) in the overshoot and by  $45\mu$ s (about 80%) in the undershoot under the line transient response. Meanwhile, for the load transient response, the recovery time is reduced by  $15\mu$ s (about 50%) and  $10\mu$ s (about 50%), respectively. Thus, the MA-PID algorithm immensely improves the dynamic response to enhance the system performance.

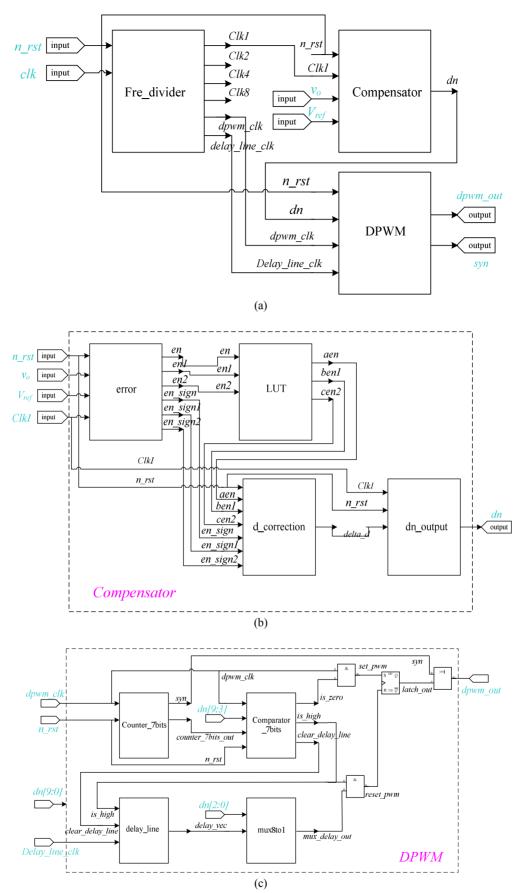

### IV. FPGA IMPLEMENTATION OF THE MA-PID CONTROL ALGORITHM

Digital controllers based on Field-Programmable Gate Arrays (FPGAs) are widely used in various applications. They have some advantages such as flexibility, parallel computing capability and integration. The digital compensator and DPWM are the main part of the implemented digital control circuit based on a FPGA. They are described using Hardware Description Language (HDL). Fig. 10 illustrates the HDL blocks which will be synthesized on the FPGA. It can be seen that compensator module uses a look-up table, and that the DPWM module uses a hybrid structure.

For the static voltage requirement, this paper requires that the output voltage  $V_{out}$  should be kept at 1% around the reference voltage  $V_{ref}$ =1.8V. In addition, according to the compensation method in section V, the actual controller parameters have a fractional part which cannot been realized directly using hardware description language. Therefore, the parameters should be amplified by a factor of 2<sup>n</sup> and rounded to their nearest value [22]. The amplification factor decides the rounding error, and the larger the factor is, the smaller the rounding error becomes. However, if the amplification factor is larger, the area consumption increases. Therefore, the compromise between the factor and the area is particularly important. Finally, the duty command u(k) in equations (9) and (10) should be scaled to  $1/2^n$  to compute the actual duty ratio.

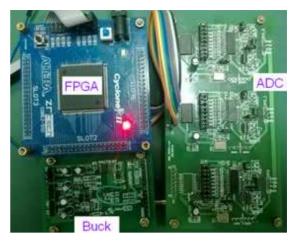

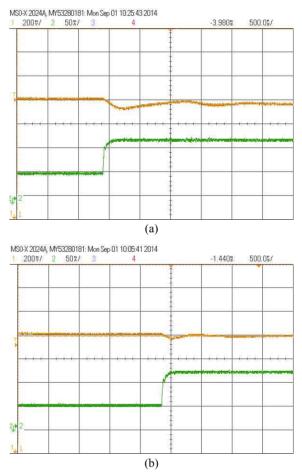

In order to test these two control algorithms, a buck converter prototype has been implemented as shown in Fig. 11. The power MOSFET transistor is a UPA2791, and the driver chip is a UCC27524. An Altera Cyclone II chip (EP2C50208C8N) is used to implement the conventional PID and MA-PID control algorithms. The input voltage  $v_{in} = 5V$  is set to the closed-loop to achieve an output voltage at 1.8V. Fig. 12 shows the output voltage transient waveforms of the converter with the conventional PID and MA-PID controllers under load current changes. The results indicate that the MA-PID control algorithm possesses a lower amplitude of overshoot/undershoot, a faster recovery time and a smaller voltage deviation. The recovery time of the MA-PID controller is about 300µs, which is a reduction of 60%, and the amplitude of the undershoot is 34mV, which is a reduction of 53%, when compared with the conventional PID controller.

Fig. 11. A buck converter prototype and control system (FPGA+ADC).

Fig. 12. Transient waveforms under load change of 0.8 to 1.5A Top-to-bottom: output voltage, load current. (a)Conventional PID. (b)MA-PID.

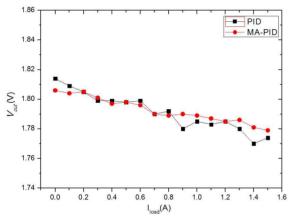

Fig. 13 shows the corresponding steady-state output voltage under a different load current. It can be seen that the proposed MA-PID control algorithm achieves a smaller steady-state deviation ( $<18\mu$ V/mA), when compared with the conventional PID algorithm.

The specifications and performances of the proposed

| COMPARISON OF THE SIMULATION RECOVERY TIME OF BOTH METHODS |                             |            |                                |            |  |

|------------------------------------------------------------|-----------------------------|------------|--------------------------------|------------|--|

| Algorithm                                                  | Line transient response(1V) |            | Load transient response(500mA) |            |  |

| Algorithm                                                  | overshoot                   | undershoot | overshoot                      | undershoot |  |

| PID                                                        | 40µs                        | 60µs       | 30µs                           | 20µs       |  |

| MA-PID                                                     | 15us                        | 15us       | 15us                           | 10µs       |  |

TABLE V

TABLE IV

Comparison of the Simulation Recovery Time of both Method

|                       | This paper               | [23]                             | [24]                     | [25]                         | LTC3530              |

|-----------------------|--------------------------|----------------------------------|--------------------------|------------------------------|----------------------|

| Control type          | Digital                  | Digital                          | Digital                  | Digital                      | Analog               |

| Control algorithm     | Adaptive digital<br>PID  | Improved digital<br>peak current | Adaptive PD+I<br>DCD-RLS | Fist-order digital<br>filter | NA                   |

| Switch frequency      | 1MHz                     | 50kHz                            | 20kHz                    | 3.125MHz                     | 1MHz                 |

| Input voltage         | 3.6-5V                   | 5V                               | 10V                      | 0-3.3V                       | 1.8-5.5V             |

| Output voltage        | 1.8V                     | 1.5V                             | 3.3V                     | 0.1-3.3V                     | 3.3V                 |

| Filter inductor @DCR  | 4.7µH@200mΩ              | 20µH                             | 220µH@63mΩ               | 2.2µH                        | 4.7µH                |

| Filter capacitor @ESR | 10µF@100mΩ               | 1420µF                           | 330µF@25mΩ               | 10µF                         | 22µF                 |

| Number of A/D         | 1                        | 2                                | 1                        | 1                            | 0                    |

| The precision of A/D  | 8bit                     | 8bit                             | 12bit                    | 10bit                        | NA                   |

| The precision of DPWM | 10bit                    | 10bit                            | >12bit                   | >10bit                       | NA                   |

| Load Step Response    | 0.43µs/mA<br>0.049 mV/mA | 1.24µs/mA<br>0.07mV/mA           | 1.82µs/mA<br>0.38mV/mA   | 2µs/mA<br>0.08mV/mA          | 1µs/mA<br>0.33 mV/mA |

Fig. 13. Output voltages under different load currents.

MA-PID control algorithm are compared with those reported for DC-DC converters in recent studies. This comparison is summarized in Table V. It shows that the proposed MA-PID control algorithm achieves a better load step response than those of references [23]-[25] and a LTC3530 chip under the condition of reduced hardware requirements.

#### V. CONCLUSIONS

This paper presents a modified adaptive PID algorithm for digitally controlled DC/DC buck converters. The proposed algorithm does not require any additional components, and it does not detect any extra signals which reduces the complexity and cost of the controller. In addition, this paper also gives a step-by-step design flow of models, simulations and implementations based on FPGA for DC/DC converters. The simulation results indicate that the proposed control algorithm improves the line and load transient responses when compared with the conventional PID and AD-PID algorithms. Meanwhile, it can be seen from the experimental results that the proposed MA-PID algorithm possess better dynamic performance, such as a faster recovery time, a smaller steady-state deviation and a lower amplitude of the overshoot/undershoot.

Although this paper uses a Buck-type power converter topology as an example, a similar concept can be extended to other digital control switching converter systems.

#### ACKNOWLEDGMENT

This work was supported in part by the National Nature Sci ence Foundation of China under grant no. 61376029 called St udy of Nonlinear Theory and Single Input PID Fuzzy Control Algorithm on Digitally Controlled DC-DC Converters. Any opinions and conclusions are those of the authors and do not necessarily reflect the views of the National Nature Science F oundation.

#### REFERENCES

- B. J. Patella, A. Prodic, A. Zirder, and D. Maksimovic, "High-frequency digital controller IC for DC/DC converters," in *Proc. Applied Power Electronics Conference* and Exposition (APEC), pp. 374-380, 2002.

- [2] P. Zumel, C. Fernandez, M. Sanz, A. Lazaro, and A. Barrado, "Step-by-step design of an FPGA-based digital compensator for DC/DC converters oriented to an introductory course," *IEEE Trans. Educ.*, Vol. 54, No. 4, pp. 599-609, Nov. 2011.

- [3] Y. F. Liu, E. Meyer, and X.D. Liu, "Recent developments in digital control strategies for DC/DC switching power converters," *IEEE Trans. Power Electron.*, Vol. 24, No. 11,

pp. 2567-2577, Nov. 2009.

- [4] M. Mahdavian, M. B. Poudeh, and N. Wattanapongsakorn, "Improving the efficiency of power supplies with an adaptive control method," in *Proc. ECTI-CON*, pp. 1-4, 2013.

- [5] H. Wangxin and J. A. A. Qahouq, "Tuning of a digital proportional-integral compensator for DC-DC power converter," in *Proc. APEC*, pp. 270-275, 2013.

- [6] J. A. A. Qahouq and V. Arikatla., "Online closed-loop auto-tuning digital controller for switching power converters," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 5, pp. 1747-1758, May 2013.

- [7] F. Kurokawa, R. Yoshida, Y. Maeda, K. Murata, "Transient response of novel fast digital PID control DC-DC converter," in *Proc. ICEMS*, pp. 1-4, 2011.

- [8] F. Kurokawa, Y. Maeda, Y. Shibata, H. Maruta, T. Takahashi, K. Bansho, T. Tanaka, and K. Hirose, "Fast response digital PID control circuit for DC-DC converter," in *Proc. IEEE Region 10 Conference*, pp. 2159-2164, 2010.

- [9] F. Kurokawa and R. Yoshida, "Transient response of fast digital PID control switching power supply," in *Proc. IEEE Vehicle Power and Propulsion Conference*, pp. 614-617, 2012.

- [10] A. T. L. Lee Albert, J. K. O. Sin Johnny, P. C. H. Chan, "Adaptive high-bandwidth digitally controlled buck converter with improved line and load transient response," *IET Power Electron.*, Vol. 7, No. 3, pp. 515-526, Mar. 2014.

- [11] Wang Qing, Chen Ning, Xu Shen, et al, "Trajectory prediction control for digital control DC-DC converters with fast transient response," *Microelectronics Journal*, Vol. 45, No. 6, pp. 767-774, Jun. 2014.

- [12] V. Yousefzadeh, A. Babazadeh, B. Ramachandran, E. Alarcon, L. Pao, and D. Maksimovic, "Proximate time-optimal digital control for synchronous buck DC-DC Converters," *IEEE Trans. Power Electron.*, Vol. 23, No. 4, pp. 2018-2026, Jul. 2008.

- [13] C. E. Carreio, E. Vidal-Idiarte, R. Giral, and L. Martinez-Salamero, "Predictive digital interpolation current control for DC-DC power converters," *IET Power Electron.*, Vol. 2, No. 5, pp. 545-554, Sep. 2009.

- [14] J.-T. Su, D.-M. Liu, C.-W. Liu, and C.-W. Hung, "An adaptive control method for two-phase DC/DC converter," in *Proc. International Conference on Power Electronics and Drive Systems (PEDS)*, pp. 288-293, 2009.

- [15] V. Arikatla and J. A. A. Qahouq, "Adaptive digital proportional-integral-derivative controller for power converters," *IET Power Electron.*, Vol. 5, No. 3, pp. 341-348, Mar. 2012.

- [16] P. Ovidiu and L. Serban, "Switching mode power converters modeling with parasitic components," in *Proc.* 30<sup>th</sup> *International Spring Seminar on Electronics Technology*, pp. 545-550, 2007.

- [17] Z. Xu and X. Shi, "Simulation study of buck converters based on Matlab/GUI," *Journal of East China Jiaotong University*, Vol. 29, No. 4, pp. 35-39, 2012.

- [18] H. Cheng, C. Wang, and J. Wang, Modeling, Control and Digital Controller Implementation of Switching Power Converters, Tsinghua University Press, pp. 104-106, 2013.

- [19] S. P. Li and Q. S. Jiang, "Study on PID Parameters Tuning Method Based on Matlab/Simulink," in *Proc. IEEE International Conference on Communication Software and Networks*, pp. 408-411, 2011.

- [20] V. Arikatla and J. A. A. Qahouq, "DC-DC power converter with digital PID controller," in *Proc. Applied Power Electronics Conference and Exposition (APEC)*, 2011.

- [21] J. H. Su, J. J. Chen, and D. S. Wu, "Learning feedback controller design of switching converters via Matlab/Simulink," *IEEE Trans. Educ.*, Vol. 45, No. 4, pp. 307-315, Nov. 2002.

- [22] S. Chander, P. Agarwal, and I. Gupta, "FPGA-based PID controller for DC-DC converter," in *Proc. Joint International Conference on Power Electronics, Drives and Energy Systems*, pp. 1-6, 2010.

- [23] G. Zhou, J. Xu, and Y. Jin, "Improved digital peak current predictive control for switching DC-DC converters," *IET Power Electron.*, Vol. 4, No. 2, pp. 227-234, Feb. 2011.

- [24] A. Mather, A. Matthew, and G. Damian, "Adaptive PD+I control of a switch-mode DC-DC power using a recursive FIR predictor," *IEEE Trans. Ind. Appl.*, Vol. 47, No. 5, pp. 2135-2144, Sep./Oct. 2011.

- [25] E. G. Soenen, A. Roth, J. Shi, M. Kinyua, J. Gaither, and E. Ortynska, "A robust digital dc-dc converter with rail-to-rail output range in 40nm CMOS," in *Proc. IEEE Int. Solid-State Circuits*, pp. 198-199, 2010.

Ling Lv received her B.S. degree from the China Three Gorges University, Yichang, China, in 2012. She is presently pursuing her M.S. degree in Integrated Circuit (IC) Engineering from the Southeast University, Nanjing, China. Her current research interests include the digital controllers for DC/DC power converters.

Changyuan Chang received his M.S. and Ph.D. degrees in Electronic Engineering from the Southeast University, Nanjing, China, in 1990 and 2000, respectively. He is presently an Associate Professor in the School of Integrated Circuits, Southeast University. His current research interests include analog controlled and digitally ps for power management

controlled IC designs for power management.

**Zhiqi Zhou** received her B.S. degree from the Xi'an University of Posts and Telecommunications, Shanxi, China, in 2013. She is presently pursuing her M.S. degree in Integrated Circuit (IC) Engineering at Southeast University, Nanjing, China. Her current research interests include digital controlled ICs for DC/DC power converters.

Yubo Yuan received his B.S. degree from Chang'an University, Xi'an, China, in 2013. He is presently pursuing his M.S. degree in Integrated Circuit (IC) Engineering at Southeast University, Nanjing, China. His current research interests include control algorithms and the design of power converters.