JPE 15-4-1

http://dx.doi.org/10.6113/JPE.2015.15.4.861 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Wide Frequency Range LLC Resonant Controller IC with a Phase-Domain Resonance Deviation Prevention Circuit for LED Backlight Units

YoungJun Park\*, Hongjin Kim\*, Joo-Young Chun\*, JooYoung Lee\*, YoungGun Pu\*, and Kang-Yoon Lee<sup>†\*</sup>

### **Abstract**

This paper presents a wide frequency range LLC resonant controller IC for LED backlight units. In this paper a new phase-domain resonance deviation prevention circuit (RDPC), which covers a wide frequency and input voltage range, is proposed. In addition, a wide range gate clock generator and an automatic dead time generator are proposed. The chip is fabricated using  $0.35~\mu m$  BCD technology. The die size is 2~x~2~mm2. The frequency of the clock generator ranges from 38~kHz to 400~kHz, and the dead time ranges from 300~ns to  $2~\mu s$ . The current consumption of the LLC resonant controller IC is 4~mA for a 100~kHz operation frequency using a supply voltage of 15~V.

**Key words:** Backlight unit, Clock generator, Dead time, LED driver, LLC resonant controller, Prevention Circuit (RDPC), Resonance Deviation, Wide range

### I. INTRODUCTION

In recent years, Liquid Crystal Display (LCD) flat panels have become one of the fastest growing markets in large screen displays due to their various advantages, such as a low power consumption, long lifespan, low profile and high contrast ratio [1], [2]. Since LCDs are non-emissive display devices, they usually require a Back Light Unit (BLU) for monitor or TV applications. Recently, Light-Emitting Diodes (LEDs) have become one of the most promising candidates for BLUs and other lighting applications [3]. Since power consumption is directly related to the screen size in an LCD backlighting system, the demand for large screen LCDs and high power density is gradually increasing. As a result, a variety of higher-power topologies have been considered in order to achieve high efficiency in a compact space with low-EMI generation. LLC resonant converters are popularly adapted to consumer and industrial electronics due to their inherent advantages over contending topologies [4]-[7]. Such advantages enable highly efficient operation over a wide input voltage range as a consequence of the very low switching losses found in zero voltage switching (ZVS) conditions. In addition, these converters are suitable for integration, since the two inductors required to form an LLC tank can be integrated into one magnetic core without the need for extra components [10]-[13].

The architecture of the proposed wide range LLC resonant controller IC is discussed in Section II, and the building blocks are described in Section III. Sections IV and V present the simulation and measurement results and the conclusion, respectively.

# II. THE PROPOSED LLC RESONANT CONVERTER SYSTEM ARCHITECTURE

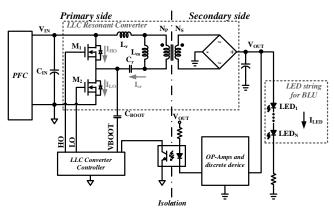

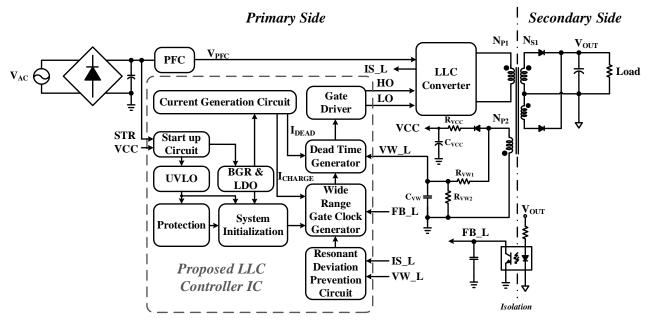

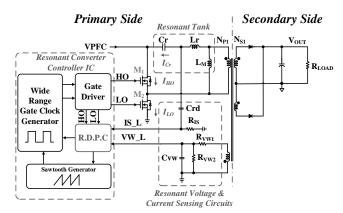

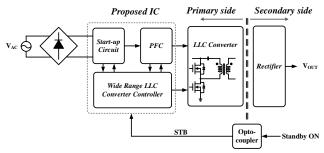

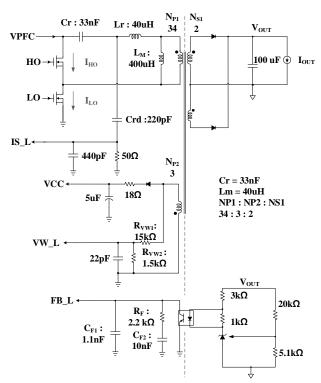

Fig. 1 shows the proposed half-bridge LLC resonant LED driving circuit. The LLC resonant controller IC is located on the primary side.

Fig. 2 shows the DC gain characteristics of the LLC converter. When the switching frequency is higher than the resonant frequency ( $f_0$ ), the voltage gain of the LLC resonant converter is always less than one. Thus, the Zero Voltage

Manuscript received Oct. 25, 2014; accepted Mar. 6, 2015 Recommended for publication by Associate Editor Joung-Hu Park. †Corresponding Author: klee@skku.edu

Tel: +82-31-299-4954, Fax: +82-31-299-4629, Sungkyunkwan Univ. \*College of Information and Communication Eng., Sungkyunkwan University, Korea

<sup>\*†</sup>College of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea

Fig. 1. The proposed half-bridge LLC resonant converter.

fo: Resonant Frequency f<sub>P</sub>: Maximum Gain Frequency Gain Max Gain Wide Range ZCS Region **ZVS** Region LLC Converter Active Region Conventional LC Converter Active Region  $\mathbf{f}_{\mathbf{P}}$  $f_{SW(Min)}$  $f_{O}$ f<sub>SW(Max)</sub>

f<sub>SW</sub>: Switching Frequency

Fig. 2. The DC gain characteristics of the LLC resonant converter.

Switching (ZVS) mode can be achieved. When the switching frequency is lower than the resonant frequency (f<sub>0</sub>), either the ZVS or Zero Current Switching (ZCS) modes can be achieved [5].

As a result, the converter must be operated at a frequency higher than f<sub>P</sub>, which depends on the value of Q, so that it can always work in the ZVS region.

Eq. (1)-(3) represent the resonant frequency  $(f_0)$  and the minimum frequency (f<sub>P</sub>) needed to achieve the ZVS mode for different load conditions and quality factors (Q), respectively. f<sub>sw</sub> is the operating frequency of the converter.

$$f_0 = \frac{1}{2\pi \sqrt{LC}} \tag{1}$$

$$f_P = \frac{1}{2\pi \sqrt{(L+L)C}} \tag{2}$$

$$f_{o} = \frac{1}{2\pi\sqrt{L_{r}C_{r}}}$$

$$f_{P} = \frac{1}{2\pi\sqrt{(L_{r} + L_{m})C_{r}}}$$

$$Q = \frac{\sqrt{L_{r}/C_{r}}}{R_{LOAD}}$$

(1)

(2)

The operating frequency of the LLC resonant converter must operate in the ZVS region. When the operating region enters the ZCS region, the external Power FET can break down because of the inrush peak current which flows into the back gate diode. To compensate for this defect, previously proposed LLC resonant converters were limited to a minimum frequency to limit the maximum gain.

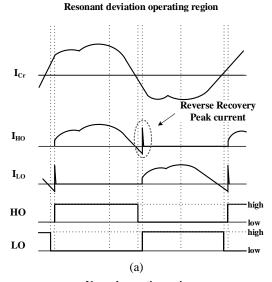

Fig. 3(a) and 3(b) show a timing diagram during the

Fig. 3. Timing diagrams of LLC converter operating region. (a) Resonance deviation operating region. (b) Normal operating

resonance deviation region operation and the normal region operation, respectively. Fig. 3(a) and 3(b) show a timing diagram in the resonance deviation region operation and the normal region operation, respectively. Fig. 3(a) shows the operation in the resonance deviation region. During the high duration of the HO signal, the I<sub>HO</sub> current decreases after reaching its maximum value. The resonant current, I<sub>Cr</sub>, changes from positive to negative. In this state, if HO is at a low level, the current goes through the parasitic diode of M<sub>1</sub> in Fig. 1 because of the forward bias. If the LO signal is at a high level, the parasitic diode of  $M_1$  in Fig. 1 goes in to the reverse recovery mode because of the reverse bias. In the reverse recovery mode, the impedance of the M<sub>1</sub> parasitic diode momentarily becomes very low and a peak current occurs. Therefore,  $M_1$  is damaged, as shown in Fig. 1.

During a high level state of LO, the I<sub>LO</sub> current decreases after reaching its maximum value. As shown in Fig. 3 (a), the

Fig. 4. The architecture of proposed half-bridge LLC resonant converter system.

resonant current,  $I_{Cr}$ , changes from negative to positive. In this state, if the LO signal is low, the current goes through the parasitic diode of  $M_2$  in Fig. 1 because of the forward bias. If HO is at a high level, the parasitic diode of  $M_2$  in Fig. 1 is put in the reverse recovery mode because it meets the reverse bias condition. In the reverse recovery mode, the impedance of the  $M_2$  parasitic diode momentarily becomes very low and a peak current occurs. Therefore,  $M_2$  can be damaged, as shown in Fig. 1.

Fig. 3(b) shows the operation in the normal region. During a high level state of HO, the  $I_{HO}$  current decreases after reaching its maximum value. If  $I_{HO}$  is positive and turns off the HO signal, the current goes through the parasitic diode in  $M_1$  in Fig. 1 because the parasitic diode of  $M_1$  is in the forward bias condition.

If the HO signal is at a high level, the resonant current, I<sub>Cr</sub>, changes continuously. During a high level state of LO, the I<sub>LO</sub> current decreases after reaching its maximum value. If I<sub>LO</sub> is positive with a low level LO, the current goes through the parasitic diode of M<sub>2</sub> in Fig. 1 because of the forward bias. If HO is at a high level, the resonant current, I<sub>Cr</sub>, changes continuously. As a result, if the I<sub>Cr</sub> signal is positive, the HO signal is high. However, LO signal is high and the LLC converter operates in the ZVS region, if the I<sub>Cr</sub> signal is negative. The maximum gain of the LLC converter can be achieved by adding a circuit that senses the I<sub>Cr</sub> signal to limit the minimum switching frequency. The proposed LLC resonant controller IC protects the circuit by limiting the switching frequency at which it receives feedback from the resonant state of the LLC converter. Therefore, the proposed LLC resonant converter can achieve a much higher gain when compared to previous designs.

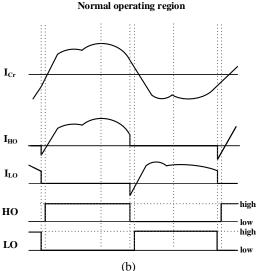

Fig. 4 shows the detailed architecture of the proposed LLC

controller IC. The proposed LLC controller IC is composed of a Resonance Deviation Prevention Circuit (RDPC), a wide range gate clock generator, a dead time generator, a startup circuit, a gate driver, a protection circuit, a current generation circuit, a system initialization circuit, a BandGap Reference (BGR), a Low Drop Out (LDO) and an Under Voltage Lock Out (UVLO). When the VCC voltage is higher than the Under Voltage Lock Out (UVLO) level and the operating condition is normal, the system initialization is operated by the internal LDO. The cross conduction problem is critical in the design of the SMPS (Switched-Mode Power Supply), because many switching circuits fail to meet the necessary performance requirements due to this problem.

Cross conduction results in premature transistor failure, excessive output noise, low efficiency and excessive heat [8]. The most common method used to prevent cross conduction is to provide a dead time between the complementary driving pulses, HO and LO, in order to turn off both of the transistors at the same time. The duration of this dead time is designed to be long enough to assure that the conduction states of the power MOSFETs, M<sub>1</sub> and M<sub>2</sub> from Fig. 1, do not overlap under any circumstances. In addition, the minimum duty ratio of the complementary driving pulses needs to be guaranteed for each switching cycle due to the body diode conduction time of the power MOSFETs [9]. Therefore, a typical dead time is several percent of the driving time in order to insure a safe operating margin. This limits the range of the PFM control. In this paper, a new dead time generator based on a mono-stable structure is proposed for robust operation with respect to variations.

Accordingly, the proposed LLC controller IC is based on a frequency feedback control system in order to regulate its output.

Fig. 5. Detailed block diagram of the LLC resonant converter system including RDPC.

Fig. 6. The conceptual diagram of RDPC function.

# III. THE BUILDING BLOCKS

### A. The Resonance Deviation Prevention Circuit

The LLC resonant converter uses a Resonance Deviation Prevention Circuit (RDPC) to achieve the minimum switching frequency and to guarantee operation in the ZVS region.

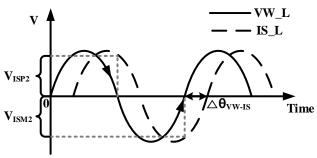

Fig. 5 is a block diagram of the RDPC that is applied to the LLC Resonant Converter. The RDPC can maximize the operating frequency range of the LLC resonant converter. If the inductance and capacitor in the LLC resonant tank are varied, the RDPC controls the operating frequency adaptively. Because the frequency range of the LLC converter is widened, the corresponding voltage ranges of the input and output are also increased. Thus, the LLC converter can be applied to various applications. The operation of the RDPC is explained below. Fig. 6 shows a conceptual diagram of the RDPC. Since the LCC resonant converter should operate in the ZVS region, the phase of the IS\_L voltage lags the VW\_L voltage and the IS\_L voltage.

When the VW\_L voltage crosses 0 V, the RDPC circuit detects the level of the IS\_L voltage. The IS\_L voltage should be positive when the VW\_L voltage changes from positive to negative.

On the other hand, the IS\_L voltage should be negative when the VW\_L voltage changes from negative to positive. In the RDPC circuit, the voltage levels of  $V_{\rm ISP2}$  and  $V_{\rm ISM2}$  are

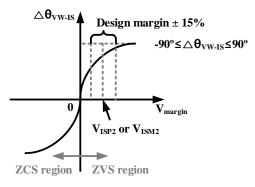

Fig. 7. The phase  $\theta_{VW-IS}$  vs the level of  $V_{ISP2}$  or  $V_{ISM2}$ .

pre-defined so that  $\theta_{VW-IS}$  cannot be less than the pre-defined levels. This guarantees that the LLC resonant converter operates in the ZVS region.

Fig 7 shows the phase difference between VW\_L and IS\_L with respect to the design margin factors for  $V_{ISP2}$  or  $V_{ISM2}$ . When the phase difference  $\theta_{VW\text{-}IS}$  is positive, the LLC resonant converter operates in the ZVS region.

The margin levels of  $V_{ISP2}$  and  $V_{ISM2}$  were pre-defined and verified through a post layout simulation. The LLC resonant converter was operated in the ZVS region with respect to Process, Voltage, Temperature (PVT) variations of  $\pm 15$  %. The resonant frequency ( $f_p$ ) of the LLC resonant converter is determined by L and C in the resonant tank, whose variations can be covered by the design margin in the LLC resonant controller IC.

The RDPC detects the resonant current with the capacitor,  $C_{rd}$ , of the LLC resonant converter at the IS\_L terminal. In addition, it detects the resonant voltage of the transformer at the VW\_L terminal using the voltage division between  $R_{VW1}$  and  $R_{VW2}$ . The voltage of VW\_L is the resonant voltage signal and voltage of IS\_L is the resonant current signal of the LLC converter. If the LLC converter operates in the ZVS region, the characteristic of the resonant tank of the LLC converter is inductive. From this, the slope of the voltage of IS\_L can be determined using the voltage of VW\_L. In other words, if the voltage of VW\_L is positive, the voltage of IS\_L increases; and if the voltage of VW\_L is negative, the voltage of IS\_L decreases.

When HO is turned on, the voltage of IS\_L turns-off HO before it becomes negative. LO turns-on when the voltage of IS\_L is positive. On the other hand, when LO is turned on, the voltage of IS\_L turns-off LO before it becomes positive. LO turns-off when the voltage of IS\_L is positive. After the voltage of IS\_L becomes negative, HO turns-on and it limits the minimum switching frequency.

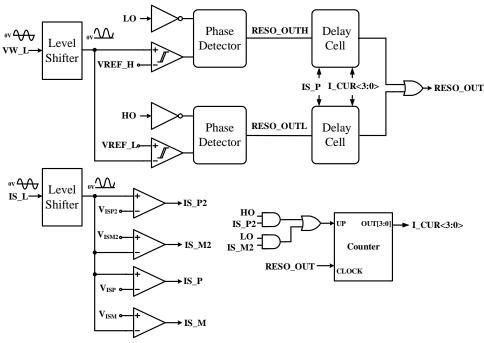

Fig. 8 is a block diagram of the proposed RDPC. It consists of a level shifter, a phase detector, a delay cell and a counter. The negative voltages of the VW\_L signal and IS\_L signal are shifted to positive voltages by the level shifter since they need to be detected by the following blocks. The inputs of the high

Fig. 8. Block diagram of the proposed RDPC.

side phase detector are the VW\_L signal and the HO signal. If HO becomes high and the voltage of VW\_L is negative, the RESO\_OUTH signal becomes high, and the voltage of IS\_L decreases. Similarly, the inputs of the low side phase detector are the voltage of VW L and the LO signal. If LO becomes high and the voltage of VW\_L is positive, the RESO\_OUTL signal becomes high, and the voltage of IS\_L increases. Thus, the high side phase detector and low side phase detector indicate the increment and decrement of the voltage of IS\_L, respectively. The high side delay cell and low side delay cell generate a delay time based on the voltage of IS\_L and the outputs of the high side phase detector and low side phase detector. In addition, their delay times are controlled by the outputs (I\_CUR<3:0>) of the counter. The outputs of the high side delay cell and low side delay cell are merged by the OR gate to generate the RESO\_OUT signal. If RESO\_OUT is high, the HO or LO signal becomes low in order to stop the gate switching before it goes to a lower frequency. The counter is used to control the delay time of the high side delay cell and low side delay cell. If HO is high when the RDPC is active and the voltage of IS\_L is smaller than V<sub>ISM2</sub>, I\_CUR<3:0> is shifted by one step from the LSB to the MSB and one bit is added to the LSB.

On the other hand, if the voltage of IS\_L is larger than  $V_{\rm ISM2}$ , I\_CUR<3:0> keeps its previous value. In addition, when LO becomes high and the voltage of IS\_L is smaller than  $V_{\rm ISP2}$ , I\_CUR<3:0> is shifted by one step from the LSB to the MSB and one bit is added to the LSB. On the other hand, if the voltage of IS\_L is larger than  $V_{\rm ISP2}$ , I\_CUR<3:0> keeps its previous value. The switching frequency of the LLC converter is limited to the minimum switching frequency, step-by-step,

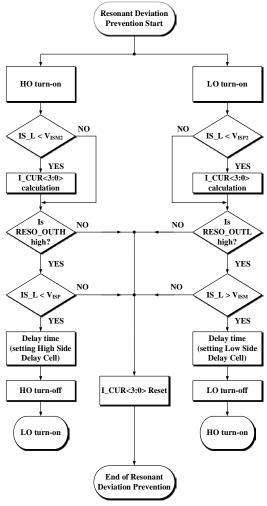

Fig. 9. Flowchart of the proposed RDPC.

Fig. 10. Timing diagram of the proposed RDPC.

based on the operation explained above. As a result, the LLC converter approaches the minimum switching frequency smoothly.

Fig. 9 is a flowchart of the proposed RDPC. If the RDPC is active and HO becomes high, I\_CUR<3:0> is increased or keeps its previous value by comparing the voltages of IS\_L and  $V_{\rm ISM2}$  with the comparator. If RESO\_OUTH is low and the voltage of IS\_L is larger than  $V_{\rm ISP}$ , I\_CUR<3:0> is reset to "0000" and the RDPC operation is terminated. On the other hand, if LO starts to operate, I\_CUR<3:0> is increased or keeps its previous value by comparing the voltages of IS\_L and  $V_{\rm ISP2}$  with the comparator. If RESO\_OUTL is low and the voltage of IS\_L is smaller than  $V_{\rm ISM}$ , I\_CUR<3:0> is reset to "0000" and the RDPC operation is terminated.

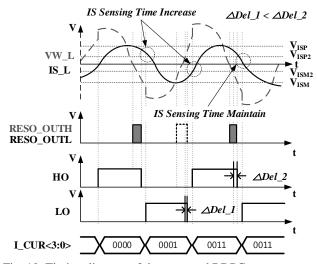

Fig. 10 is a timing diagram of the proposed RDPC. While the HO signal is high, IS\_L decreases after reaching its maximum value. The resonant tank of the LLC converter is located at the boundary between the capacitive and inductive regions. The polarity of VW\_L is positive when IS\_L increases, and the polarity of VW L is negative when IS L decreases.

If the HO signal is high, RESO\_OUTH becomes high when VW\_L is low. If IS\_L is lower than  $V_{\rm ISP}$ , the HO signal becomes low after the delay time of the high side delay cell.

When the LO signal is high and IS\_L is larger than  $V_{\rm ISP2}$ , I\_CUR<3:0> is increased from "0000" to "0001". If IS\_L is larger than  $V_{\rm ISM}$ , the LO signal becomes low after the delay time of the low side delay cell. The delay time of the low side delay cell is determined by an I\_CUR<3:0> of "0001". If the HO signal becomes high and IS\_L is smaller than  $V_{\rm ISM2}$ , I\_CUR<3:0> is changed from "0001" to "0011". Thus, the delay time of the high side delay cell is determined by an I CUR<3:0> of "0011".

## B. The Wide Range Gate Clock Generator

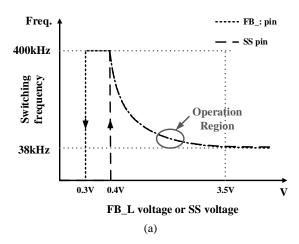

The LLC resonant converter consists of a frequency feedback loop. The clock generator from the conventional LLC

Fig. 11. (a) The switching frequency characteristics. (b) On pulse width characteristics of the proposed wide range gate clock generator.

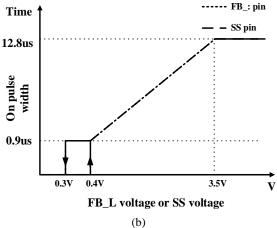

resonant converter uses a linear switching frequency with respect to the feedback voltage. On the other hand, the on time of the gate pulse in the proposed wide range gate clock generator was designed to have a linear relationship with the feedback voltage.

By using the proposed linear on time scheme, the switching frequency of the LLC resonant converter changes quickly until it reaches the target frequency so that power loss can be minimized at the initial start-up operation. The feedback accuracy is also enhanced by changing the switching frequency slowly after reaching the target operation frequency.

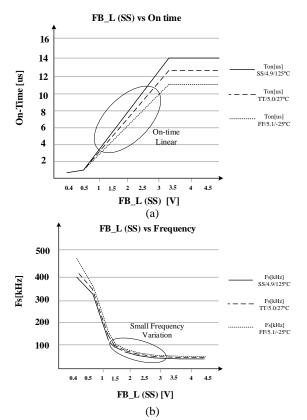

As shown in Fig. 11(a), the switching frequency is determined by the lowest voltage level among the FB\_L and SS voltages. The frequency of the gate clock generator is fixed at 400 kHz until the FB\_L or SS voltage reaches 0.4 V. The gate clock generator stops operating when the FB\_L or SS voltage reaches 0.3 V with a hysteresis of 0.1 V. Fig. 11(b) is the on pulse width graph with respect to the FB\_L or SS voltage. The regulation characteristics are improved by controlling the pulse width linearly. This lowers the frequency variation at the operating frequency of the LLC resonant converter.

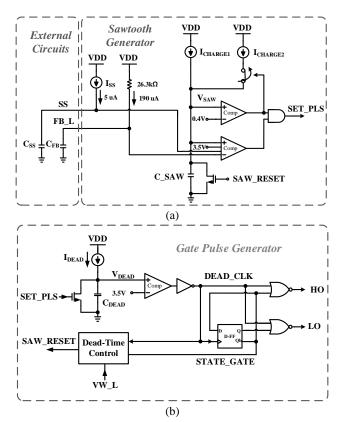

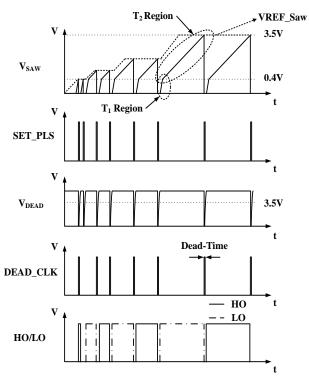

Fig. 12. The block diagram of (a) Sawtooth Generator. (b) Gate Pulse Generator used in the Wide Range Gate Clock Generator.

In addition, the feedback accuracy can be improved by minimizing the frequency variation, which is controlled by the operation of the RDPC.

Fig. 12(a) is a block diagram of the sawtooth generator used in the wide range gate clock generator. The capacitors (Css and CFB) from the external circuits are charged by the current sources in the sawtooth generator. Furthermore, the switching frequency is determined by the lowest voltage among the FB\_L or SS voltages. C\_SAW is charged by the current sources I<sub>CHARGE1</sub> and I<sub>CHARGE2</sub>. If the voltage across C\_SAW is over 0.4 V, it is charged by I<sub>CHARGE1</sub>. A dual slope sawtooth generator is implemented so that the on-pulsewidth is controlled linearly with respect to the voltage of SS and FB\_L. In this design, the frequency range is from 38 kHz to 400 kHz. Another block in the wide range gate clock generator is the gate pulse generator as shown in Fig. 12(b). The voltage from C<sub>DEAD</sub> is discharged when the SET\_PLS signal becomes high. If the voltage of V<sub>DEAD</sub> becomes 0 V, DEAD\_CLK becomes high. If DEAD\_CLK becomes high, HO and LO become low because they are connected to a NOR gate.

SET\_PLS becomes low when the SET\_RESET signal is active. This is generated by the VW\_L and dead-time control block. After that,  $I_{DEAD}$  recharges  $C_{DEAD}$  until  $V_{DEAD}$  goes over 3.5 V. Then DEAD\_CLK becomes lower by the comparator. Fig. 13 is a timing diagram of the wide range gate clock generator. In the  $T_1$  region,  $C\_SAW$  is charged by two current sources,  $I_{CHARGE1}$  and  $I_{CHARGE2}$ .

Fig. 13. The timing diagram of the proposed Wide Range Gate Clock Generator.

At this time, the output frequency is determined by Eq. (4).

$$f_{out.max} = \frac{1}{2T_1} = \frac{I_{CHARGE1} + I_{CHARGE2}}{2 \cdot C \cdot SAW \times (0.4)}$$

(4)

During the  $T_2$  region, C\_SAW is charged by only one current source,  $I_{CHARGE1}$ . The output frequency of the wide range gate clock generator is determined by Eq. (5).

$$f_{out} = f_{out.max} + \frac{I_{CHARGE1}}{2 \cdot C - SAW \times (VREF - Saw - 0.4)}$$

(5)

When  $V_{SAW}$  reaches VREF\_Saw, the SET\_PLS signal goes high. Then, the  $V_{DEAD}$  node is discharged and the DEAD\_CLK signal goes high. The HO and LO signals become low to turn off the corresponding power MOSFETs when DEAD\_CLK is high.

### C. Automatic Dead Time Generator

In the design of the LLC resonant converter, the dead time needs to be carefully determined because the minimum duty cycle of the gate driving output is related to the conduction time of the body diode of the power MOSFET. The minimum dead time is related to the output capacitance of the power MOSFET. Since the LLC resonant converter is inherently a variable frequency topology, dead-time control is occasionally not essential and may influence the available frequency range.

The automatic dead time generator generates the dead time actively with respect to the switching frequency information and the values of Lr and Cr of the resonant tank.

Even if the switching frequency is changed, an optimized dead-time is generated for the proper operation of the LLC resonant converter.

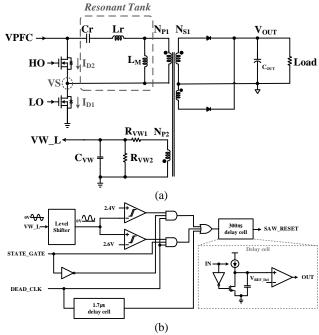

Fig. 14. (a) The external LLC resonant circuits. (b) Detailed block diagram of the proposed Automatic Dead Time Generator.

As the switching frequency reaches the maximum available frequency, hard switching can occur. In order to prevent the LLC resonant converter from hard switching, the automatic dead time generator automatically controls the dead-time from 300 ns to  $2 \mu \text{s}$ .

Fig. 14(a) shows the external LLC resonant circuits. The VW\_L voltage follows the variation of the VS voltage. The VW\_L voltage can be described by Eq. (6) when the HO signal is high.

$$\frac{N_{P1}}{N_{P2}} \times VW _L = VS + Vcr + V_{Lr} - VPFC$$

(6)

Eq. (7) and (8) can be derived from Eq. (6) by differentiating both sides.

$$\frac{dVW_{L}}{dt} = \frac{N_{S1}}{N_{P1}} (\frac{dVS}{dt} + \frac{dV_{CR}}{dt})$$

(7)

$$\frac{dVW_{L}}{dt} = \frac{N_{S1}}{N_{P1}} \left( \frac{I_{CR}}{C_{VS}} + \frac{I_{CR}}{Cr} \right)$$

(8)

Assuming that  $Cr \gg C_{VS}$ , Eq. (8) can be rewritten as Eq. (9).

$$\frac{dVW_{-}L}{dt} \approx \frac{N_{S1}}{N_{P1}} \times \frac{dVS}{dt}$$

(9)

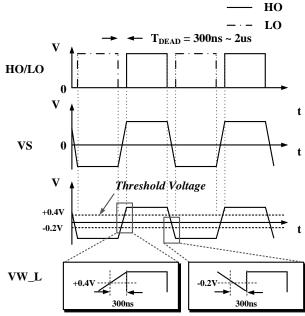

Fig. 14(b) shows a detailed block diagram of the automatic dead time generator. The output signals of wide range gate clock generator, STAGE\_GATE, DEAD\_CLK, and VW\_L are applied to the inputs of the automatic dead time generator. When STATE\_GATE is low, HO is turned on. On the other hand, LO is turned on when STATE\_GATE is high. When STATE\_GATE is low, the VW\_L voltage changes from positive to negative, and STATE\_GATE becomes high when

Fig. 15. The timing diagram of the automatic dead time generator.

the VW\_L voltage changes from negative to positive. The automatic dead time generator block is triggered by the DEAD\_CLK signal. When VW\_L is not detected during 1.7  $\mu$ s, the output of the OR gate becomes high. After the delay time of 300 ns, the SAW\_RESET signal becomes high and the gate of the next block is turned on. Delay times of 1.7  $\mu$ s and 300 ns are generated by the delay cell consisting of a comparator, a current source, and a capacitor.

Fig. 15 is a timing diagram of the automatic dead time generator. During the dead time, the VS signal crosses 0 V.

As shown in Eq. (9), the change rate of the VS signal can be represented by the change rate of VW\_L. When the LO signal becomes low and VW\_L is larger than 0.4 V, the HO signal becomes low after 300 ns. When the HO signal becomes low and VW\_L is smaller than -0.2 V, the LO signal becomes high after 300 ns.

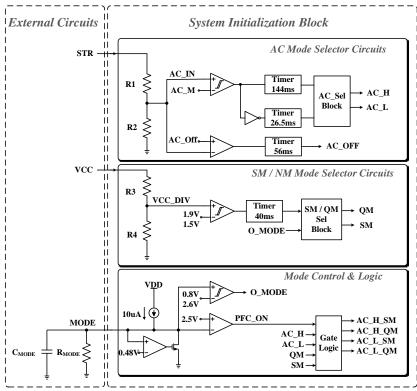

### D. The System Initialization Block

The proposed LLC resonant converter controller IC can support the operation of standby mode regardless of the existence of an external PFC IC before the system starts.

Fig. 16 is a block diagram of the system initialization. When the VCC voltage is over 12 V, the LLC resonant controller IC monitors the MODE voltage that is integrated through  $C_{\text{MODE}}$  and  $R_{\text{MODE}}$  for 40 ms. It also selects the operation mode between the standby mode (SM) and the quiet mode (QM).

AC\_H and AC\_L are selected by comparing the external STR voltage level with the reference using the comparator. The low power standby or quiet modes are selected depending on the  $R_{\text{MODE}}$  resistor value, as summarized in Table I.

Fig. 16. The block diagram of System Initialization.

$\label{eq:table_independent} TABLE\,I$  Mode Selection Depending on  $R_{MODE}$  Resistor Value

| Mode                          | $\mathbf{R}_{	ext{MODE}}$ |

|-------------------------------|---------------------------|

| Anti-Noise with PFC           | $56~\mathrm{k}\Omega$     |

| Low-Power Standby with PFC    | $100~\text{k}\Omega$      |

| Anti-Noise without PFC        | $200~k\Omega$             |

| Low-Power Standby without PFC | $300~k\Omega$             |

The quiet mode is the preferred mode since it reduces the noise of the transformer by slowing down the variations of the switching frequency. The purpose of the low-power standby mode is to achieve a high gain for the LLC converter by rapidly changing the switching frequency.

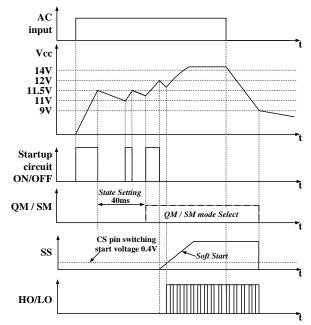

Fig. 17 is a timing diagram of the system initialization and mode selection unit of the proposed LLC resonant converter. When an AC input voltage is applied, the startup circuit operates and the VCC voltage increases. When the VCC voltage reaches 11.5 V, the operation of the startup circuit is stopped and the external voltage is sensed to select the operation mode for 40ms. If the VCC voltage is lower than 11 V, the startup circuit is enabled.

### E. Standby Mode

When there is no load at the secondary side, the minimum necessary blocks operate in a burst way and the proposed LLC resonant converter controller IC enters the standby mode where it consumes minimum power until the load current increases. In the standby mode, the LLC

Fig. 17. The timing diagram of System Initialization block.

resonant converter operates to maintain the internal VDD voltage. By using the SS voltage, the soft start function is enabled and the LLC resonant converter is stabilized.

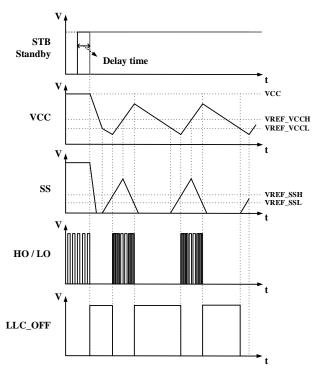

Fig. 18 is a system block diagram in the stand-by mode. The LLC controller IC receives the STB signal using an opto-coupler. The LLC controller IC turns off the PFC and normal circuit operation when the STB signal is high. The LLC converter senses the VCC voltage and operates in the

Fig. 18. The system block diagram in Stand-By mode.

Fig. 19. The timing diagram in Standby Mode.

burst mode.

Fig. 19 is a timing diagram in stand-by mode. When the STB signal becomes high, the HO and LO signals become low, and discharge the SS and VCC voltages.

The VCC voltage is discharged until it reaches VREF\_VCCL. Then, the SS voltage starts to charge until it reaches VREF\_SSL. Then, the HO and LO signals start switching and the VCC voltage is recharged.

When the VCC voltage reaches VREF\_VCCH, the SS voltage starts to be discharged. If the SS voltage is lower than VREF\_SSL, then HO and LO become low and turn off the power MOSFETs. The switching frequency is determined by the SS voltage level and the soft burst mode is implemented by alternating between high and low frequencies.

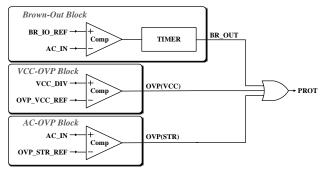

### F. Protection Circuit

As shown in Fig. 20, the LLC resonant controller IC includes a protection circuit for over voltage, brown out, and over load conditions. The brown out block turns off the LLC controller IC if the external AC supply voltage is lower than

Fig. 20. The protection circuit.

Fig. 21. The Over Current Protection circuit.

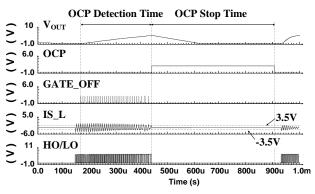

Fig. 22. The timing diagram of the OCP circuit.

the reference voltage (BR LO REF).

The Over Voltage Protection (OVP) turns off the LLC controller IC when the VCC and external AC supply voltages are higher than the reference voltages OVP\_VCC\_REF and OVP\_STR\_REF.

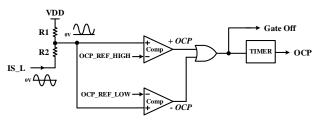

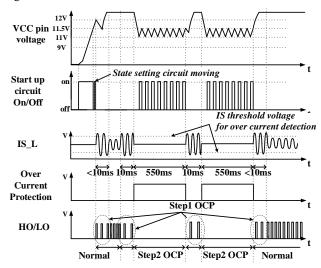

Fig. 21 shows the Over Current Protection (OCP) circuit. The OCP is activated when the IS\_L voltage is higher than the OCP\_REF\_HIGH signal or lower than the OCP\_REF\_LOW signal. There are two steps in the OCP. The first step is to turn off the gate that has sensed the +OCP or – OCP. After that, the next side gate is turned on to operate the LLC converter. If the first step lasts more than 10 ms, the OCP signal turns off the LLC controller IC for 55 ms. The LLC controller IC enables soft-start operation because of the auto recovery of the OCP circuit.

Fig. 22 shows a timing diagram of the OCP operation. The resonant current signal of the external LLC converter is

Fig. 23. The chip microphotograph.

detected by the IS\_L signal. It is used inside the IC through the resistor division and level shifter. When IS\_L is over the threshold of over voltage protection, HO and LO are turned off and another side gate is turned on. When the gates of the power MOSFETs are turned off, the current of the LLC converter does not increase any more. On the other hand, when the next side gate is turned on, the polarity of the current is changed.

This is the first step of the OCP operation. If the first step lasts more than 10 ms, the next OCP step operates and the HO and LO signals are low for 550 ms. The VCC voltage decreases if the HO and LO signals are low and the VCC voltage is lower than 11 V. Then, the startup circuit is enabled. When the VCC voltage is lower than 11.5V, the startup circuit is disabled to keep the IC voltage stable. After 550 ms, the auto recovery function of the OCP circuit is started. When the IS\_L voltage is over the OCP detection level, the next step is started after the first step.

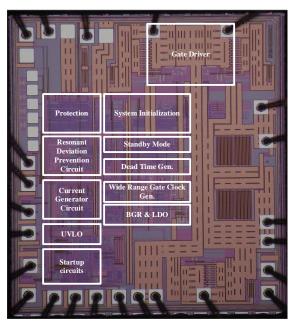

### IV. SIMULATION AND MEASUREMENT RESULTS

The chip was fabricated using a BCD process with 0.35  $\mu$ m technology using one poly layer, four metal layers, and the option of a high-voltage MOSFET. A microphotograph of the chip is shown in Fig. 23. The die area of the controller IC is 2 x 2 mm<sup>2</sup>.

The blocks are placed with consideration of the power consumption and performance of the IC. The gate driver and start up circuits are located around the sides of the chip since they consumes a large amount of current. The length of the current path between the PAD and the circuits is minimized to reduce parasitic resistance and power loss. In the standby mode, current is consumed only when the gate switching is operated.

TABLE II

THE EXPERIMENT CONDITIONS

| Parameters                           | Value                          |  |  |

|--------------------------------------|--------------------------------|--|--|

| PFC Input Voltage (VPFC)             | 100 ~ 385 V                    |  |  |

| Output Current (I <sub>OUT</sub> )   | 0A or 6.75 A or 10A            |  |  |

| Output Voltage (V <sub>OUT</sub> )   | 12.8 V                         |  |  |

| The transformer winding turns        | $N_{P1} N_{P2} : N_{S1}$       |  |  |

| ratio                                | = 34 : 3 : 2                   |  |  |

|                                      | $L_{\rm M} = 400  \mu \rm H,$  |  |  |

| Resonant Tank                        | $Lr = 40 \mu H$ ,              |  |  |

|                                      | Cr = 33  nF                    |  |  |

| Output Capacitor (C <sub>OUT</sub> ) | 100 μF / 50V                   |  |  |

|                                      | Crd: 220 pF                    |  |  |

| IS_L and VW_L detect circuits        | $R_{VW1}:15 \text{ k}\Omega$   |  |  |

|                                      | $R_{VW2}: 1.5 \text{ k}\Omega$ |  |  |

|                                      | C <sub>F1</sub> : 1.1 nF       |  |  |

| FB_L Feedback parameter              | $C_{F2}:10 \text{ nF}$         |  |  |

|                                      | $R_F: 2.2 \; k\Omega$          |  |  |

Fig. 24. The experimental environment.

The gate driver, wide range gate clock generator, dead time generator, current generator circuits, and RDPC are disabled to minimize the current consumption when the gate of the power MOSFET is turned off.

The experimental conditions for the proposed wide range LLC controller circuit are summarized in Table II.

$N_{\rm P}$  and  $N_{\rm S}$  are the transformer winding turns ratios from Fig. 24.  $L_{\rm M}$  is the transformer magnetizing inductance, and  $L_{\rm r}$  is the series leakage inductance with the series capacitance,  $C_{\rm r}.$  Crd is used for dividing the resonant current capacitor.  $R_{\rm VW1}$  and  $R_{\rm VW2}$  are used for dividing the resonant voltage.

Fig. 25. The measured waveform of the RDPC.

Fig. 26. The simulated waveforms of the RDPC.

Fig. 27. The relationship between (a) On-Time (b) Switching Frequency and FB\_L (SS).

Fig. 28. The simulation regulation characteristics (a)  $I_{OUT}$  is 6.75 A (b)  $I_{OUT}$  is 10 A, (c)  $I_{OUT}$  is 0 A.

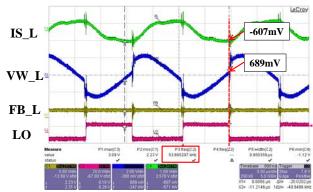

Fig. 25 shows a measured waveform of the RDPC when the VPFC voltage is 127 V and the output current is 5 A. The low side gate driver (LO) is turned off when the VW\_L and IS\_L voltages reach 689 mV and -607 mV, respectively. Under these operating conditions, the switching frequency is limited to 53 kHz.

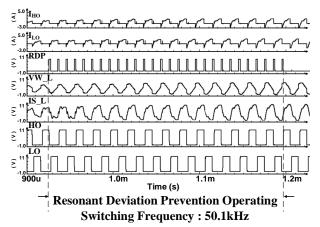

Fig. 26 shows simulated waveforms of the RDPC. As the switching frequency gets lower, the RDPC senses the VW\_L and IS\_L waveforms to limit the switching frequency to 50.3 kHz.

Fig. 27(a) shows the linear relationship between the on-time and the FB\_L or SS voltage. Under the typical conditions (VDD is 5.0 V, the process is TT, and the temperature is 27  $\,^\circ\!\! \mathrm{C}$ ) the on-time can be controlled linearly from 936 ns to 12.86  $\mu s$ . As shown in Fig. 27(b), the switching frequency is from 38 kHz to 400 kHz. Due to the linear on-time, the controllable frequency range is 100 kHz, which is relatively small when compared with conventional approaches.

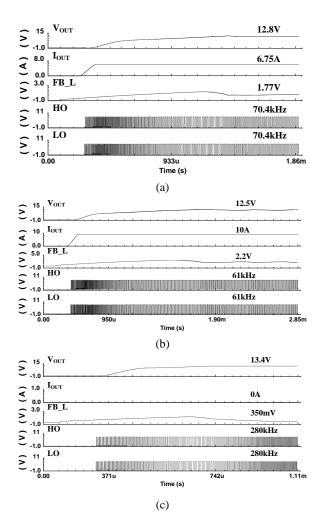

Figs. 28(a)-(c) are the simulated regulation characteristics with respect to the load current ( $I_{OUT}$ ) variations. Fig. 28(a)

Fig. 29. The relationship between (a) output voltage (b) switching frequency and load current of proposed LLC resonant controller IC.

Fig. 30. The output waveforms of the automatic dead time generator in case of (a) dead time =  $2 \mu s$  (b) dead time = 300 ns.

Fig. 31. The simulated waveforms in Standby mode.

Fig. 32. The simulated waveforms for over current protection.

shows that the output voltage (V<sub>OUT</sub>) is regulated to 12.8 V at a typical load current of 6.75 A. The FB\_L voltage is 1.77 V and the switching frequency is 70.4 kHz. Fig. 28(b) shows that the output voltage (V<sub>OUT</sub>) is regulated to 12.5 V with a ripple voltage of 0.5 V and at a full load current of 10 A. To regulate the output voltage, the switching frequency is reduced to 61 kHz so that the gain of the LLC converter increases. Fig. 28(c) shows that the regulated output voltage is 13.4 V at no load current. With no load, the switching frequency rises to 280 kHz to minimize the gain of the LLC converter. The FB\_L voltage drops to 350 mV adjusting the on time and dead times of HO/LO to 930 ns and 900 ns, respectively.

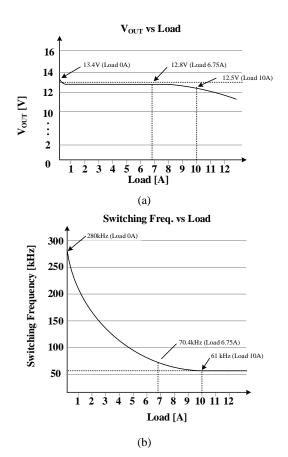

Fig. 29(a) shows that the output voltage ( $V_{OUT}$ ) is decreased as the load current is increased. With no load, the  $V_{OUT}$  voltage is regulated to 13.4 V. With load currents of 6.75 A and 10 A, the  $V_{OUT}$  voltage is regulated to 12.8 V and 12.5 V, respectively. Fig. 29(b) shows that the switching frequency is decreased as the load current is increased.

With no load, V, the switching frequency is 280 kHz. With load currents of 6.75 A and 10 A, the switching frequency is 70.1 kHz and 61 kHz, respectively.

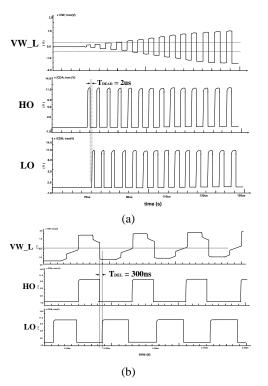

Figs. 30(a)-(b) show the output waveforms of the automatic dead time generator. In Fig. 30(a), when the switching frequency is at its maximum, the duration of the dead time is 2  $\mu$ s. From Fig. 30(b), at the minimum switching frequency, the duration of the dead time is 300 ns.

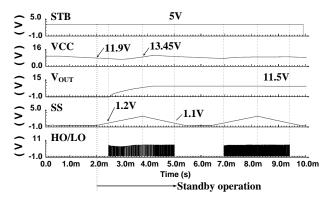

Fig. 31 shows the simulated waveforms in the stand-by

| THE FERT GRAPH CE COMPARISON TO FRICK WORKS      |                     |                     |                     |                     |  |

|--------------------------------------------------|---------------------|---------------------|---------------------|---------------------|--|

|                                                  | [19]                | [20]                | [21]                | This work           |  |

| Operating<br>Voltage                             | 15 V                | 12 V                | 15 V                | 15 V                |  |

| Current<br>Consumption                           | 25 mA               | 13.3 mA             | 8 mA                | 4 mA                |  |

| Resonance<br>Deviation<br>Prevention<br>Function | No                  | No                  | No                  | Integrated          |  |

| Dead-time<br>Adjustment<br>Function              | Integrated          | No                  | No                  | Integrated          |  |

| Frequency Control Range of Clock Generator       | 60 kHz ~<br>235 kHz | 50 kHz ~<br>525 kHz | 50 kHz ~<br>215 kHz | 38 kHz ~<br>400 kHz |  |

| Dead-time                                        | 230 ns ~<br>700 ns  | 290 ns              | 300 ns              | 300 ns ~<br>2 us    |  |

TABLE III

THE PERFORMANCE COMPARISON TO PRIOR WORKS

mode. The HO and LO signals become low to turn off the power MOSFETs when the STB signal reaches 5 V. The SS voltage starts charging when the VCC voltage drops to 12 V. When the SS voltage is over 1.2 V, the HO and LO signals start switching and the switching frequency decreases. When the VCC voltage reaches 13.5 V, the SS voltage is discharged and the switching frequency increases. When the SS voltage is below 1.1 V, the HO and LO signals become low to turn off the power MOSFETs.

Fig. 32 shows the simulated waveform of the Over Current Protection (OCP). When the IS\_L voltage reaches 3.5 V, the GATE\_OFF signal is generated and the HO/LO signals are turned off. After 10 ms, the OCL becomes high and the HO/LO signals are turned off. After 550 ms, the HO/LO signals are recovered automatically and the soft-start operation begins.

Table III shows a performance comparison between this and prior works. The parameters are written in the order of the operating voltage, the current consumption, the use of the resonance deviation prevention function, the use of the dead-time adjustment function, the frequency control range of the clock generator, the dead-time range and the use of the standby mode.

The current consumption of the proposed IC is lower than that of references, [19], [20], and [21]. The speed of the comparator does not need to be fast. Therefore, the current consumption of the comparator is minimized. In addition, the bias currents of the current mirror and operational amplifier are optimized.

### V. CONCLUSIONS

This paper presents a wide range LLC resonant controller IC with a phase-domain resonance deviation prevention circuit for LED backlight units. The chip is fabricated using  $0.35~\mu m$  BCD technology, and the die size is  $2~x~2~mm^2$ . The frequency

of the clock generator ranges from 38 kHz to 400 kHz, and the dead time ranges from 300 ns to 2  $\mu$ s. The current consumption of the LLC resonant controller IC is 4 mA for a 100 kHz operation frequency using a supply voltage of 15 V.

### ACKNOWLEDGMENT

This research was supported by the MSIP(Ministry of Science, ICT and Future Planning), Korea, under the ITRC(Information Technology Research Center) support program (NIPA-2014-(H0301-14-1008)) supervised by the NIPA(National IT Industry Promotion Agency)

### REFERENCES

- [1] L. Y. Pan, S. C. Chang, M. Y. Liao, and Y. T Lin, "The future development of global LCD TV industry," in *Proc. PICMET*, pp. 1818 -1821, 2007.

- [2] F. Xiaoyun, L. Xiaojian, and W. Yan, "Research and analysis of the design development and perspective technology for LED lighting products," in *Proc. IEEE CAID&CD*, pp. 1330-1334, 2009,

- [3] S.-S. Hong, S.-H. Lee, S.-H. Cho, C.-W. Roh, and S.-K. Han "A new cost-effective current-balancing multi-channel LED driver for a large screen LCD backlight units," *Journal of Power Electronics*, Vol. 10, No. 4, pp. 351-356, Jul. 2010.

- [4] B. Yang and F. C. Lee, "LLC resonant converter for front end DC/DC conversion," in *Proc. IEEE APEC*, Vol. 2, pp. 1108-1112, 2002.

- [5] B. Lu, W. Liu, Y. Liang, F. C. Lee, and J. D. Van Wyk, "Optimal design methodology for LLC resonant converter," in *Proc. IEEE APEC*, pp. 533-538, 2006.

- [6] H.-S. Choi, "Design consideration of half-bridge LLC resonant converter," *Journal of Power Electronics*, Vol. 7, No. 1, pp. 13-20, Jan. 2007.

- [7] B. Yang, "Topology investigation of front end DC DC converter for distributed power system," Ph. D. thesis, Virginia Polytechnic Institute, Blacksburg, VA, USA, 2003.

- [8] D. J. Tschirhart and P. K. Jain, "Secondary-side control of a constant frequency series resonant converter using dual-edge PWM," in *Proc. IEEE APEC*, pp. 544-549, 2010.

- [9] J. Garcia, A. J. Calleja, E. L. Corominas, D. Gacio, and J. Ribas, "Electronic driver without electrolynic capacitor for dimming High Brightness LEDs," in *Proc. IEEE IECON*, pp. 3518-3523, 2009.

- [10] W. Liu and J. D. van Wyk, "Design of integrated LLCT module for LLC resonant converter," in *Proc. IEEE APEC*, pp. 362-368, 2005.

- [11] Y. Lembeye, P. Goubier, and J. P. Ferrieux, "Integrated planar L-C-T component: design, characterization and experimental efficiency analysis," *IEEE Trans. Power Electron.*, Vol. 20, No. 3, pp. 593-599, May 2005.

- [12] J. Garcia, M. A. Dalla-Costa, J. Cardesin, J. M. Alonso, M. Rico-Secades, "Dimming of high-brightness LEDs by means of luminous flux thermal estimation," *IEEE Trans. Power Electron.*, Vol. 24, No. 4, pp.1107-1114, Apr. 2009.

- [13] C. C. Chen, C. Y. Wu, Y. M. Chen, and T. F. Wu, "Sequential color LED backlight driving system for LCD panels," *IEEE Trans. Power Electron.*, Vol. 22, No. 3, pp.

- 919-925, May 2007.

- [14] K. Zhou, J. G. Zhang, S. Yuvarajan, and D. F. Weng, "Quasi-active power factor correction circuit for HBLED driver," *IEEE Trans. Power Electron.*, Vol. 23, No. 3, pp. 1410-1415, May 2008.

- [15] R. Beiranvand, B. Rashidian, M. R. Zolghadri, and S. M. H. Alavi, "Optimizing the normalized dead-time and maximum switching frequency of a wide-adjustable-range LLC resonant converter," *IEEE Trans. Power Electron.*, Vol. 26, No. 2, pp. 462-472, Feb. 2011.

- [16] D. Fu, Y. Liu, F. C. Lee, and M. Xu, "Novel driving scheme for synchronous rectifiers in LLC resonant converters," *IEEE Trans. Power Electron.*, Vol. 24, No. 5, pp. 1321-1329, May 2009.

- [17] S.-W. Hong, H.-J. Kim, J. S. Park, Y. G. Pu, J. Cheon, D. H. Han, and K. Y. Lee, "Secondary-side LLC resonant controller IC with dynamic PWM dimming and dual-slope clock generator for LED backlight units," *IEEE Trans. Power Electron.*, Vol. 26, No. 11, pp. 3410-3422, Nov. 2011.

- [18] H. J. Kim, S. Y. Kim, and K. Y. Lee, "A dual-output integrated LLC resonant controller and LED driver IC with PLL-based automatic duty control," *Journal of Power Electronics*, Vol. 12, No. 6, pp. 886-894, Nov. 2012.

- [19] L6699: Enhanced High Voltage Resonant Controller, www.st.com, Jan. 2013.

- [20] NCP1398B/C: High Performance Resonant Mode Controller with Integrated High-Voltage Drivers, www.onsemi.com, Jan. 2013.

- [21] ICE2HS01G: High Performance Resonant Mode Controller, www.infineon.com, May 2011.

YoungJun Park received his B.S degree in Electronics Engineering from the Kumoh National Institute of Technology, Gumi, Korea, in 2013. Since then he has been working toward his M.S. degree in Electronics and Computer Engineering from Sungkyunkwan University, Suwon, Korea. His current research interests include the

design of power management integrated circuits for high efficiency and wireless power transfer systems.

Hongjin Kim received his B.S. degree from the Department of Electronic Engineering, Chungju University, Chungju, Korea, in 2010. He is presently working toward his Ph.D. degree in the College of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea. His current research interests include CMOS RF

transceivers, power management ICs and mixed signal integrated circuits.

Joo-Young Chun received his B.S. degree from the Department of Electronic Engineering, Hankuk University of Foreign Studies, Seoul, Korea, in 2013. He is presently working toward his M.S. degree in the School of Information and Communication Engineering, Sungkyunkwan University,

Suwon, Korea. His current research interests include power management ICs and wireless power transfer systems.

JooYoung Lee was born in Incheon, Korea. He received his B.S. degree from the Department of Electronic Engineering, Incheon National University, Incheon, Korea, in 2014. He is presently working toward his M.S. degree in the School of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea. His current

research interests include power management ICs.

YoungGun Pu received his B.S., M.S., and Ph.D. degrees from the Department of Electronic Engineering, Konkuk University, Seoul, Korea, in 2006, 2008, and 2012, respectively. His current research interests include CMOS fully integrated frequency synthesizers and oscillators, and transceivers for low-power mobile communications.

Kang-Yoon Lee received his B.S., M.S., and Ph.D. degrees in the School of Electrical Engineering, Seoul National University, Seoul, Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was a Manager of the Analog Division and worked on the design of CMOS

frequency synthesizers for CDMA/PCS/PDC, and single-chip CMOS RF chip sets for W-CDMA, WLAN, and PHS. From 2005 to 2011, he was with the Department of Electronics Engineering, Konkuk University, Seoul, Korea, as an Associate Professor. Since 2012, he has been with School of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea, where he is presently an Associate Professor. His current research interests include the implementation of power integrated circuits, CMOS RF transceivers, analog integrated circuits, and analog/digital mixed-mode VLSI system designs.