JPE 16-5-13

http://dx.doi.org/10.6113/JPE.2016.16.5.1743 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Reduced Switch Count Topology of Current Flow Control Apparatus for MTDC Grids

Hatem Yassin Diab<sup>†</sup>, Mostafa Ibrahim Marei<sup>\*</sup>, and Sarath B. Tennakoon<sup>\*\*</sup>

<sup>†</sup>Dept. of Electrical and Control Engineering, Arab Academy for Science, Technology and Maritime Transport (AASTMT), Cairo, Egypt

#### **Abstract**

The increasing demand for high voltage DC grids resulting from the continuous installation of offshore wind farms in the North Sea has led to the concept of multi-terminal direct current (MTDC) grids, which face some challenges. Power (current) flow control is a challenge that must be addressed to realize a reliable operation of MTDC grids. This paper presents a reduced switch count topology of a current flow controller (CFC) for power flow and current limiting applications in MTDC grids. A simple control system based on hysteresis band current control is proposed for the CFC. The theory of operation and control of the CFC are demonstrated. The key features of the proposed controller, including cable current balancing, cable current limiting, and current nulling, are illustrated. An MTDC grid is simulated using MATLAB/SIMULINK software to evaluate the steady state and dynamic performance of the proposed CFC topology. Furthermore, a low power prototype is built for a CFC to experimentally validate its performance using rapid control prototyping. Simulation and experimental studies indicate the fast dynamic response and precise results of the proposed topology. Furthermore, the proposed controller offers a real solution for power flow challenges in MTDC grids.

Key words: CFC, Current control, DC grids, MTDC, Power control, RCP

#### I. Introduction

Unlike in AC grids, power flow in any DC grid is determined mainly by grid cable resistances. A reliable and safe operation, in which cables are guaranteed to carry currents below their thermal limit even under sudden load changes, is difficult to achieve. Cables carrying currents over their limit for long periods may fail. Therefore, power (current) flow controllers are needed in DC grids. Currently, researchers and industry leaders are urged to focus on multi-terminal direct current (MTDC) grids as a solution to establish an interconnection among European grids [1]-[5]. Power flow control is one of the several major challenges that

prevent the realization of MTDC grids [6], [7]. Other challenges include the absence of high voltage DC (HVDC) circuit breakers, protection schemes, and algorithms [8]-[10]; and HVDC DC to DC converters (DC transformers) [11]-[14]. The lack of practical, reliable and accurate current (power) flow control is a critical challenge for industry practitioners and researchers. Current approaches to achieving power flow control in MTDC are based on either modifying the control of the voltage source converters [15]-[24] or adding additional devices to the grid itself [25]-[30]. The insulated gate bipolar transistor (IGBT)-based current flow controller (CFC) concept presented in [29], [30] is adopted because it offers a promising solution to the power flow control problem. The present work presents a reduced switch count topology of the CFC to achieve accurate current flow control in MTDC grids with similar voltage stresses while cutting the cost and footprint in half. The CFC is connected in series to transmission cables to achieve functionalities such as balancing cable currents and current nulling in numerous cables and thereby ease the maintenance process. The main

<sup>\*</sup>Dept. of Electrical Power and Machines, Faculty of Engineering, Ain Shams University, Cairo, Egypt

\*\*Faculty of Computing, Engineering and Sciences, Staffordshire University, Stoke on Trent, United Kingdom

Manuscript received Mar. 22, 2016; accepted Jun. 7, 2016 Recommended for publication by Associate Editor Liqiang Yuan.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: hatem.diab@research.staffs.ac.uk Tel: +202-22685616, Fax: +202-22685892, AASTMT

<sup>\*</sup>Department of Electrical Power and Machines Engineering, Ain Shams University, Egypt

<sup>\*\*</sup>Faculty of Computing, Engineering and Sciences, Staffordshire University, United Kingdom

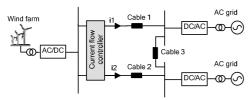

Fig. 1. A three terminal MTDC grid with CFC inserted in series.

advantage of the proposed CFC is its installation in series with the grid cables and isolation from the system ground (Fig. 1). Moreover, the voltage ratings of the capacitor and IGBT switches are relatively low in comparison with the grid voltage. This characteristic, in addition to the proposed reduced topology, leads to low manufacturing cost and footprint.

A simple control system based on the hysteresis band current control (HCC) technique is proposed for the CFC. HCC offers precise control and accurate results without the complexity of implementation or tuning. The complete operation and control of the proposed CFC are presented to balance the currents, set a current to a desired reference point, or null a current in a chosen cable. Simulation results illustrate the precise performance of the proposed CFC system. Moreover, experimental validation is carried out using advanced rapid control prototyping (RCP) by building a three-terminal DC grid with the CFC prototype to evaluate its functionality in different cases.

This paper is organized as follows. The theory of operation of the proposed reduced switch count topology for the CFC is discussed in Section II. The discussion includes possible operating modes with their switching states and mathematical modeling. The proposed control system is detailed in Section III. Computer simulations are carried out using the MATLAB/SIMULINK software package, and the results are demonstrated and analyzed in Section IV. The experimental validation of the proposed CFC system using the RCP technique is presented in Section V. Selected operating modes and functionalities are illustrated as well. Conclusions are provided in Section VI.

#### II. THEORY OF OPERATION

#### A. Operation of Current Flow Controller

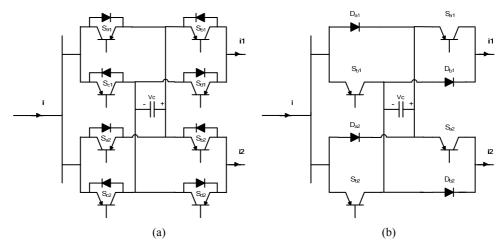

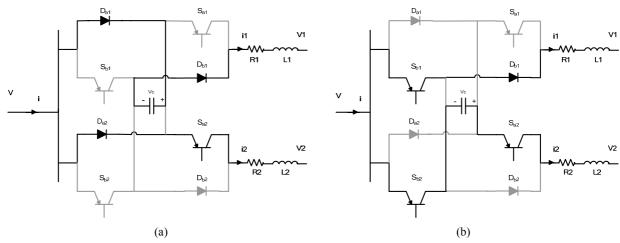

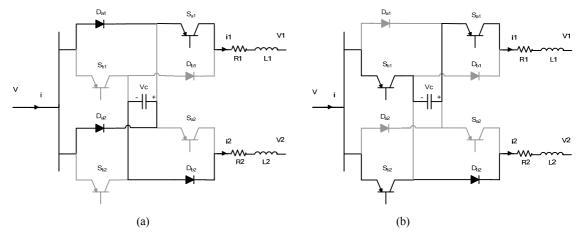

The CFC consists of IGBT switches with parallel freewheeling diodes and capacitors, as shown in Fig. 2(a). Four IGBTs are inserted in series with each cable, and a capacitor is connected between both cables. The goal is to switch the capacitor in series such that it charges from the cable carrying a higher current and discharges from the other cable. This process can be controlled to achieve the desired operation, which could be balancing the currents in both cables, setting a current to a desired value, or nulling a current to zero. The speed and duration of switching the capacitor to charge/discharge from a cable depends on the set reference value, which is determined by the controller. Fig. 2(b) illustrates the proposed reduced switch count topology for the CFC, in which the numbers of switches and diodes are reduced by half. Two modes of operation are available for the CFC. In the first mode, i1 is the higher current, and Sa2 is switched on to allow current i2 to flow in cable 2 while connecting the capacitor in series to cable 1 to charge from it (Fig. 3(a)). This phase is followed by the switching on of Sb1 and Sb2 to allow the current i1 to flow in cable 1 and to connect the capacitor in series in cable 2 for discharging (Fig. 3(b)). In mode 2, when i2 is higher than i1, the operation is identical, except Sa1 is switched on instead of Sa2 (Figs. 4(a) (b)). The switching states of different IGBTs for the two modes of operation of the CFC are summarized in Table I.

#### B. Mathematical Modeling

To dynamically model a CFC using an averaging technique, we consider operation mode 1 illustrated in Fig. 3. As shown in this figure, i1 is higher than i2. The following equations describe the circuit of Fig. 3(a), in which the capacitor is charging from the line carrying the higher current, i1.

$$V = r_1 i_1 + L_1 \frac{di_1}{dt} + v_c + V_1$$

(1)

$$V = r_{2}i_{2} + L_{2}\frac{di_{2}}{dt} + V_{2}$$

$$i_{1} = C\frac{dv_{c}}{dt}$$

(2)

$$i_1 = C \frac{dv_c}{dt} \tag{3}$$

where r<sub>1</sub> and L<sub>1</sub> are the resistance and inductance of the first line, respectively; r<sub>2</sub>and L<sub>2</sub> are the resistance inductance of the second line, respectively; v<sub>c</sub> is the capacitor voltage; V is the voltage at the bus to which CFC is connected; and V1 and V2 are the voltages at the end terminals of the first and second lines, respectively. By defining  $x^T = \begin{bmatrix} i_1 & i_2 & v_c \end{bmatrix}$  as a state vector, where T refers to the transpose operation, equations (1), (2), and (3) can be arranged in a matrix form as

$$\underbrace{\begin{bmatrix} L_1 & 0 & 0 \\ 0 & L_2 & 0 \\ 0 & 0 & C \end{bmatrix}}_{K} \underbrace{\frac{d}{dt} \begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{\hat{X}} = \underbrace{\begin{bmatrix} -r_1 & 0 & -1 \\ 0 & -r_2 & 0 \\ 1 & 0 & 0 \end{bmatrix}}_{A_1} \underbrace{\begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{X} + \underbrace{\begin{bmatrix} 1 & -1 & 0 \\ 1 & 0 & -1 \\ 0 & 0 & 0 \end{bmatrix}}_{B_1} \underbrace{\begin{bmatrix} V \\ V_1 \\ V_2 \end{bmatrix}}_{U}$$

Similarly, the state equations of Fig. 3(b), in which the capacitor is discharging into the line carrying the lower current i2. are written as follows:

$$\underbrace{\begin{bmatrix} L_1 & 0 & 0 \\ 0 & L_2 & 0 \\ 0 & 0 & C \end{bmatrix}}_{K} \underbrace{\frac{d}{dt} \begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{\hat{X}} = \underbrace{\begin{bmatrix} -r_1 & 0 & 0 \\ 0 & -r_2 & 1 \\ 0 & -1 & 0 \end{bmatrix}}_{A_2} \underbrace{\begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{\hat{X}} + \underbrace{\begin{bmatrix} 1 & -1 & 0 \\ 1 & 0 & -1 \\ 0 & 0 & 0 \end{bmatrix}}_{B_2} \underbrace{\begin{bmatrix} V \\ V_1 \\ V_2 \end{bmatrix}}_{\hat{V}}$$

Assume that the duty ratio of the charging mode of the operation is D. Multiplying (4) and (5) by D and (1-D), respectively, and adding the results to obtain the average model for the CFC when i1 >i2 yields the following:

Fig. 2. (a) CFC circuit topology [29]–[30], (b) proposed CFC reduced circuit topology.

Fig. 3. (a) CFC operating in mode 1: charging from cable 1, (b) CFC discharging in cable 2.

Fig. 4. (a) CFC operating in mode 2: charging from cable 2, (b) CFC discharging in cable 1.

$\label{eq:table_interpolation} TABLE\:I$  Switching States for CFC Modes of Operation

|      | Higher  | Switching states |          |          |                 |

|------|---------|------------------|----------|----------|-----------------|

| Mode | Current | $S_{a1}$         | $S_{a2}$ | $S_{b1}$ | S <sub>b2</sub> |

| 1    | $i_I$   | off              | on       | PWM      | PWM             |

| 2    | $i_2$   | on               | off      | PWM      | PWM             |

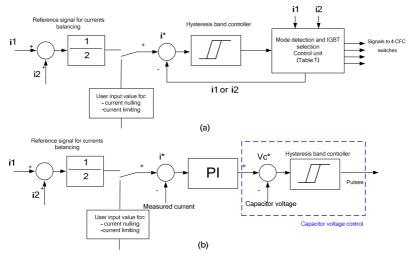

Fig. 5. (a) Proposed HCC control for the CFC, (b) proposed instantaneous voltage controller for CFC.

$$\begin{bmatrix} L_1 & 0 & 0 \\ 0 & L_2 & 0 \\ 0 & 0 & C \end{bmatrix} \underbrace{\frac{d}{dt}}_{\dot{K}} \underbrace{\begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{\dot{X}} = \begin{bmatrix} -r_1 & 0 & -D \\ 0 & -r_2 & 1-D \\ D & -1+D & 0 \end{bmatrix} \underbrace{\begin{bmatrix} i_1 \\ i_2 \\ v_c \end{bmatrix}}_{\dot{Y}_c} + \underbrace{\begin{bmatrix} 1 & -1 & 0 \\ 1 & 0 & -1 \\ 0 & 0 & 0 \end{bmatrix}}_{\dot{B}} \underbrace{\begin{bmatrix} V \\ V_1 \\ V_2 \end{bmatrix}}_{\dot{U}}$$

(6)

where A=DA1+(1-D)A2 and B=DB1+(1-D)B2. At steady state, (6) is written as

$$\begin{bmatrix} -r_1 & 0 & -1 \\ 0 & -r_2 & 0 \\ 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ V_c \end{bmatrix} + \begin{bmatrix} 1 & -1 & 0 \\ 1 & 0 & -1 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} V \\ V_1 \\ V_2 \end{bmatrix} = 0 \tag{7}$$

Solving (9), the DC steady-state value of the capacitor voltage can be expressed as

$$V_{c} = \frac{\frac{\Gamma_{2}}{\Gamma_{1}}D(V-V_{1}) + (V_{2}-V)(1-D)}{\frac{\Gamma_{2}}{\Gamma_{1}}D^{2} + (1-D)^{2}}$$

(8)

Equation (8) expresses the capacitor voltage as a function of network parameters and voltage drops across the cables connected to the CFC; this function represents the loading condition of the grid. The rated voltage of the CFC switches, which is equal to the rated capacitor voltage, can be estimated from (8).

To calculate the capacitor voltage ripple, (3) is integrated over the charging period as follows:

$$\int_0^{DT} i_1 dt = C \int_{V_{cmin}}^{V_{cmax}} v_c$$

(9)

where T refers to the switching period, which is the reciprocal of the switching frequency fs. Disregarding the current ripples compared with the average value, I1, results in the linear charging of the capacitor from the initial minimum voltage Vcmin to the maximum voltage Vcmax. The capacitor voltage ripple  $\Delta V_C$  can be estimated from (9).

$$\Delta V_c = V_{cmax} - V_{cmin} = \frac{D I_1}{c f_s}$$

(10)

Equation (10) shows that increasing the capacitance reduces the capacitor voltage ripple. Equation (7) shows that the parameters of the DC grid and loading condition influence

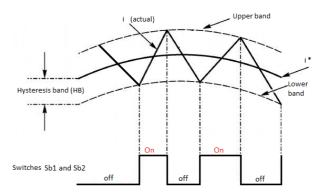

Fig. 6. Hysteresis band current control.

the line current, thus affecting the capacitor voltage ripple. The capacitor voltage ripple depends on the mode of operation as the charging current, which is I1 for mode 1, changes from mode 1 to mode 2. For mode 1, the capacitance can be roughly estimated from (8) and (10) to meet a required percentage voltage ripple,  $\Delta V_{c\,pu} = \Delta V_c/V_c$ , at the extreme deviations of the line currents. Similarly, the capacitance can be calculated for each mode of operation of the CFC. Finally, maximum capacitance is considered to meet the desired voltage ripple for all modes of operation. In the present study, the capacitance of the CFC is selected using trial and error, and, as implied by (10), higher capacitors produce smoother CFC performance and lower operating switching frequency.

#### III. PROPOSED CONTROL OF CFC SWITCHES

Fig. 5(a) illustrates the proposed control system. It is based on the HCC technique to derive the PWM switches of the proposed CFC. In case of current balancing, the average value of both currents is calculated, and the result is set as a reference value for the controller, i\*. The calculated reference value is compared with the measured actual value of the current that must be decreased, i1 or i2, which is set by the selection control unit. The error signal is considered as the

TABLE II

SIMULATION PARAMETERS

|                     | ¥7 1   |

|---------------------|--------|

| Parameter           | Value  |

| Grid voltage rating | 320 kV |

| Capacitor 1         | 1 mF   |

| Cable 1             | 1.5 Ω  |

|                     | 0.8 mH |

| Cable 2             | 2.35 Ω |

|                     | 1.1 mH |

| Cable 3             | 2.42 Ω |

|                     | 1.1 mH |

| Hysteresis band     | 5 A    |

Fig. 7. Balancing currents i1 and i2 (mode 1).

Fig. 8. CFC capacitor voltage.

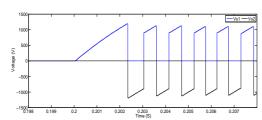

Fig. 9. Series voltages introduced by the CFC to both cables.

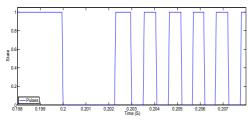

Fig. 10. HCC generated pulses.

input of the HCC (Fig. 5(a)). The on/off states determined by the HCC are assigned to the switches chosen by the IGBT selection control unit on the basis of the detected mode of operation (Table I). The HCC initially deactivates switches Sa to charge the capacitor from the cable carrying the highest current. When the actual current exceeds the reference

current with the predefined hysteresis band (HB), the HCC activates switches Sa to disconnect the capacitor and allow it to discharge in the other cable. As a result, the actual current falls below the reference current based on the HB. The process is then repeated. Fig. 5(b) shows another control circuit that enables the application of capacitor voltage regulation. The error signal is passed through a proportional integral (PI) controller, and its output is considered as the reference capacitor voltage Vc\*, which is compared with the measured value and passed through an HB controller that produces the switching signals. This step is important in cases in which capacitor voltage must be limited to ensure that it does not exceed its rated value during operation. The principle of HCC is also illustrated in Fig. 6, which shows that the effects of varying the width of the HB on the switching frequency are noticeable. Switching frequency and accuracy depend mainly on the set value of the HB. The HB is inversely proportional to the switching frequency and accuracy. HCC offers many advantages, such as simplicity and ease of implementation. Moreover, its tuning and parameter settings are not as complicated as those of PI controllers. Similarly, external reference values can be applied directly to the proposed control system for current nulling and current setting. These two functions are useful in cases in which the current in the cable must be limited to a desired value or lowered to zero to disconnect the cable and facilitate maintenance.

#### IV. SIMULATION RESULTS

A simulation is carried out using the MATLAB/SIMULINK software package, and the results are presented in this section. An MTDC grid, similar to that in Fig. 1, is simulated to evaluate the dynamic and steady-state performance of the proposed control system of the CFC. The main simulation parameters are shown in Table II. As shown in this table, cables 1 and 2 carry currents i1 and i2, respectively. Two case studies are presented to evaluate the different features and operation modes of the proposed CFC.

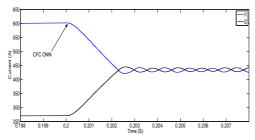

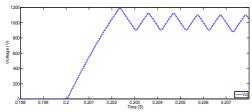

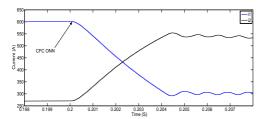

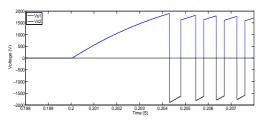

#### A. Case 1: Balancing i1 and i2

This case study demonstrates a current balancing operation using the proposed CFC. Currents i1 and i2 are initially 0.6 and 0.27 kA, respectively. The CFC is set to operate at t = 0.2 s to charge the capacitor from cable 1 and discharge it in cable 2 to achieve the balanced operation. Currents i1 and i2 reach an average of 0.43 kA (Fig. 7), which indicates a fast performance without any overshoot. The capacitor voltage Vc and series voltages Vs introduced by the CFC to both cables are shown in Figs. 8 and 9, respectively. Fig. 9 shows that both series voltages Vs1 and Vs2 are equal but opposite in terms of direction as the capacitor charges from cable 1 and starts immediately discharging in cable 2. The gating signals generated by the HCC are presented in Fig. 10. As shown in

Fig. 11. Setting current i1 to 300 A.

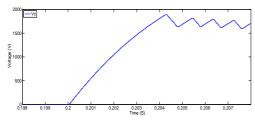

Fig. 12. Capacitor voltage.

Fig. 13. Series voltages introduced by the CFC to both cables.

Fig. 14. HCC output pulses.

this figure, HCC produces an off gating signal from  $t=0.2\,\mathrm{s}$  until the current i1 reaches the lower HB at  $t=0.202\,\mathrm{s}$ . The results demonstrate one of the advantages of the CFC, that is, the capacitor and switches are subjected to an extremely small voltage (approximately 1 kV) relative to the grid voltage of 320 kV. The result is a low production cost and footprint for the CFC.

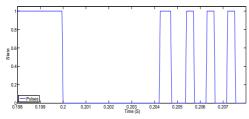

#### B. Case 2: Setting i1 to 0.3 kA

This case study limits the current i1 to 0.3 kA. As explained earlier, the user defines the reference value, which is 0.3 kA, and a similar control process is conducted. Currents i1 and i2 are shown in Fig. 11. The proposed control system of the CFC successfully performs the task, and current i1 is limited. Current i2 is increased to balance the sudden decrease in i1. The capacitor voltage and series cable voltages are shown in Figs. 12 and 13, respectively. The capacitor and series voltages are higher than those in case 1, as the capacitor must charge more in case 2 to achieve the reference

Fig. 15. Experimental RCP setup of the CFC.

## TABLE III EXPERIMENTAL PROTOTYPE PARAMETERS

| Parameter       | Value                 |

|-----------------|-----------------------|

| Terminal 1      | 150 V DC power supply |

| Terminal 2      | Electronic load       |

| Terminal 3      | Electronic load       |

| Capacitor 1     | 1 mF                  |

| N-channel IGBT  | 70 A–600 V            |

| Hysteresis band | 5 mA                  |

point. The capacitor and series voltage are approximately 2 kV, which is relatively low. Fig. 14 presents the gating signals produced by HCC in this case.

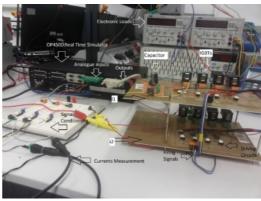

#### V. EXPERIMENTAL VALIDATION

A low power prototype of the CFC is built in the laboratory using low rating IGBT switches (Fig. 15). A three-terminal DC grid is constructed, with one terminal supplying DC and the other two connected to electronic (active) loads. The RCP technique is implemented using an OPAL RT OP4500 real-time simulator to control the CFC circuits in real time with the proposed control system. All cable currents are measured and connected as inputs to the OP4500 that outputs all gating signals to the CFC IGBT switches. The experimental prototype system parameters are shown in Table III.

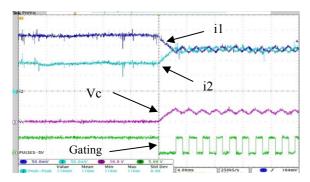

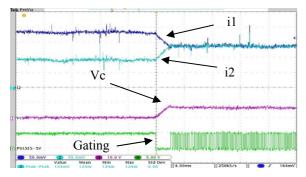

#### A. Case 1: Balancing i1 and i2

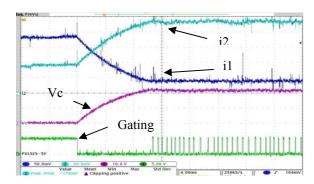

To validate case 1, as explained earlier in the simulation results section, we present a similar case, in which i1 and i2 are balanced from the initial values of 1.8 and 1 A, respectively. The HB is set to 50 mA to demonstrate the operation of HCC (Fig. 6). The results in this case are shown in Fig. 16, which shows a clear gap between currents i1 and i2 after the balancing as they are oscillating around the average value 1.4 A as a result of the high HB set. This HB is then decreased to 5 mA in Fig. 17, which shows that the accuracy increases, and the switching frequency of the pulses increase significantly from 0.5 kHz to 4 kHz. The capacitor voltage Vc is also shown in both figures. Decreasing the HB

Fig. 16. Balancing i1 and i2 with HB=50 mA. X axis: 4 ms/Div and Y axis: 0.5 A/Div, 10 V/Div, 5 V/Div.

Fig. 17. Balancing i1 and i2 with HB = 5 mA. X axis: 4 ms/div and Y axis: 0.5 A/div, 10 V/div, 5 V/div.

Fig. 18. Setting i1 to 400 mA. X axis: 4 ms/div and Y axis: 0.5 A/div, 10 V/div, 5 V/div.

Fig. 19. Nulling current i1. X axis: 4 ms/div. and Y axis: 0.5 A/div, 10 V/div, 5 V/div.

results in a smooth balancing of the currents, but a higher switching frequency is incurred.

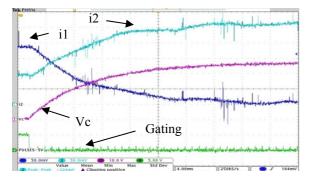

#### B. Case 2: Setting i1 to 0.4 and 0 A

The reference value is set to 0.4 A to validate the results obtained from case 2 of the simulation. i1 is successfully limited to 0.4 A, and i2 increases significantly to cover the decrease in i1 (Fig. 18). The capacitor voltage Vc is higher than that in case 1, as i1 decreases at a higher amount, in which case the capacitor has to charge more. The gating signals in this case are shown in Fig. 18. Another option is to set the reference value to zero to null the current flowing in the cable. The results of this case are shown in Fig 19, in which the capacitor is fully charged to block the current i1 and the gating signal is equal to zero to keep the capacitor connected. The success of the experimental operation demonstrates the validity of the proposed CFC and control strategy.

### VI. DISCUSSION

The simulated and experimental results validate the proposed topology and control strategy. They also show that reducing the HB results in increased switching frequency. A common practice is to set the HB in the range of 3% to 5% of the current magnitude. The performance improves as the ripples decrease; however, the switching losses increase, as expected for any power electronics converter. Hence, a CFC capacitor with high capacitance should be chosen because its application ensures a smooth operation with low voltage and current ripples while minimizing switching frequency and losses.

#### VII. CONCLUSIONS

This paper presents a reduced switch count topology for a CFC to achieve current limiting applications in DC grids, including multi-terminal HVDC systems. A simple control system based on the HCC technique is proposed for the CFC. The detailed operating modes and mathematical modeling are illustrated. Functionalities such as current balancing, current limiting, and current nulling of the proposed HCC-based CFC are discussed and evaluated accordingly. The fast dynamic response and accurate performance of the proposed system are investigated using computer software and experimental validation. As indicated in the results, the proposed CFC incurs low costs and a small footprint and thus serves as a promising solution for power flow control problems in next-generation DC grids.

#### ACKNOWLEDGMENT

The authors would like to thank the Arab Academy for Science, Technology and Maritime Transport, Cairo, Egypt; and the Staffordshire University, Staffordshire, UK, for funding Mr. Hatem Yassin Diab's PhD research project.

#### REFERENCES

- [1] D. Ebehard and E. Voges, "Digital single sideband detection for S. Gordon, "Supergrid to the rescue," *Power Engineer*, Vol. 20, No. 5, pp. 30-33, Oct. 2006.

- [2] D. V. Hertem and M. Ghandhari, "Multi-terminal VSC HVDC for the European supergrid: Obstacles," *Renewable and Sustainable Energy Reviews*, Vol. 14, No. 9, pp. 3156-3163, Dec. 2010.

- [3] F. O. S. G work group.: 'Roadmap to the supergrid technologies', http://www.friendsofthesupergrid.eu/wp-content/uploads/2014/06/WG2\_Supergrid-Technological-Roadmap 20140622 final.pdf, accessed 1 Jun. 2016.

- [4] T. K. Vrana, R. E. Torres-Olguin, B. Liu, and T. M. Haileselassie, "The north sea super grid-a technical perspective," in AC and DC Power Trans., (ABCD 2010), 9th IET International Conference on, pp. 1-5, 2010.

- [5] J. De Decker and A. Woyte. "Review of the various proposals for the European offshore grid," *Renewable Energy*, Vol. 49, pp. 58-62, Jan. 2013.

- [6] D. V. Hertem, M. Ghandhari, and M. Delimar, "Technical limitations towards a SuperGrid – A European prospective," In Energy Conference and Exhibition (EnergyCon), 2010 IEEE International, pp. 302-309, 2010.

- [7] E. Koldby and M. Hyttinen, "Challenges on the road to an offshore HVDC grid," in *Nordic Wind Power Conference*, pp. 1-8, 2009.

- [8] A. Shukla and G. D. Demetriades, "A Survey on hybrid circuit-breaker topologies," *IEEE Trans. Power Del.*, Vol. 30, No. 2, pp. 627-641, Apr. 2015.

- [9] C. D Barker and R. S. Whitehouse, "An alternative approach to HVDC grid protection," in AC and DC Power Trans. (ACDC 2012), 10th IET International Conference on, pp. 1-6, 2012.

- [10] J. Sneath and A. D. Rajapakse, "Fault detection and interruption in an earthed hvdc grid using rocov and hybrid dc breakers," *IEEE Trans. Power Del.*, Vol. 31, No. 3, pp. 1-8, Jun. 2014.

- [11] D. Jovcic, "Bidirectional, high-power DC transformer," *IEEE Transactions Power Delivery*, Vol. 24, No. 4, pp. 2276-2283, Oct. 2009.

- [12] D. Jovcic and B. T. Ooi. "Developing DC transmission networks using DC transformers," *IEEE Trans. Power Del.*, Vol. 25, No. 4, pp. 2535-2543, Oct. 2010.

- [13] C. D. Barker, C. C. Davidson, and D. R. Trainer, and R. S. Whitehouse, "Requirements of DC-DC Converters to facilitate large DC Grids," *Cigre Session 2012*, pp. 1-10, 2012.

- [14] T. Luth, M. Merlin and T. C. Green, F. Hassan, and C. D. Barker, "High-frequency operation of a DC/AC/DC system for HVDC applications," *IEEE Transactions Power Electronics*, Vol. 29, No. 8, pp. 4107-4115, Aug. 2014.

- [15] M. J. Carrizosa, F. D. Navas and G. Damm, and F. Lamnabhi-Lagarriguea, "Optimal power flow in multi-terminal HVDC grids with offshore wind farms and storage devices," *International Journal of Electrical Power & Energy Systems*, Vol. 65, pp. 291-298, Feb. 2015.

- [16] S. Rodrigues, R. T. Pinto and P. Bauer, et al. "Optimal power flow control of VSC-based multiterminal DC network for offshore wind integration in the north sea," *IEEE J. Emerg. Sel. Topics Power Electron.*, Vol. 1, No. 4, pp. 260-268, Dec. 2013.

- [17] K. Rouzbehi, A. Miranian and A. Luna, and P. Rodrigues, "DC voltage control and power sharing in multiterminal DC grids based on optimal DC power flow and

- voltage-droop strategy," *IEEE J. Emerg. Sel. Topics Power Electron.*, Vol. 2, No. 4, pp. 1171-1180, Dec. 2014.

- [18] R. T. Pinto, S. F. Rodrigues and, E. Wiggelinkhuizen, R. Scherrer, P. Bauer, and J. Pierik, "Operation and power flow control of multi-terminal DC networks for grid integration of offshore wind farms using genetic algorithms," *Energies*, Vol. 6, No. 1, pp. 1-26, Dec. 2012.

- [19] T. M. Haileselassie and K. Uhlen, "Impact of DC line voltage drops on power flow of MTDC using droop control," *IEEE Trans. Power Syst.*, Vol. 27, No. 3, pp. 1441-1449, Aug. 2012.

- [20] W. Wang and M. Barnes, "Power flow algorithms for multi-terminal VSC-HVDC with droop control," *IEEE Trans. Power Syst.*, Vol. 29, No. 4, pp. 1721-1730, Jul. 2014

- [21] C. Gavriluta, I. Candela, A. Luna, A. Gomez-Exposito, and P. Rodriguez, "Hierarchical control of HV-MTDC systems with droop-based primary and OPF-based secondary," *IEEE Trans. Smart Grid*, Vol. 6, No. 3, pp. 1502-1510, May 2015.

- [22] C. Dierckxsens, K. Srivastava, M. Reza and S. Cole, J. Beertena, and R. Belmansa, "A distributed DC voltage control method for VSC MTDC systems," *Electric Power Systems Research*, Vol. 82, No. 1, pp. 54-58, Jan. 2012.

- [23] K. Rouzbehi, A. Miranian, A. Luna, and P. Rodriguez, "DC voltage control and power sharing in multiterminal DC grids based on optimal DC power flow and voltage-droop strategy," *IEEE J. Emerg. Sel. Topics Power Electron.*, Vol. 2, No. 4, pp. 1171-1180, Dec. 2014.

- [24] K. Rouzbehi, A. Miranian, J. I. Candela, A. Luna, P. Rodriguez, "A generalized voltage droop strategy for control of multiterminal DC grids," *IEEE Trans. Ind. Appl.*, Vol. 51, No. 1, pp. 607-618, Jan. 2015.

- [25] Q. Mu, J. Liang, Y. Li, and X. Zhou, "Power flow control devices in DC grids," *Power and Energy Society General Meeting*, 2012 IEEE. 2012.

- [26] E. Veilleux and B. T. Ooi, "Multiterminal HVDC with thyristor power-flow controller," *IEEE Trans. Power Del.*, Vol. 27, No. 3, pp. 1205-1212, Jul. 2013.

- [27] S. Balasubramaniam, J. Liang and C. E. Ugalde-Loo, "An IGBT based series power flow controller for multi-terminal HVDC transmission," *Power Engineering Conference* (UPEC), 2014 49th International Universities, 2014.

- [28] T. Zhang, L. Chuanyue, and J. Liang, "A thyristor based series power flow control device for multi-terminal HVDC transmission," *Power Engineering Conference (UPEC)*, 2014 49th International Universities, 2014.

- [29] C. D. Barker and R. S. Whitehouse, "A current flow controller for use in HVDC grids," AC and DC Power Transmission (ACDC 2012), 10th IET International Conference on., 2012.

- [30] F. Hassan, R. King and R. Whitehouse, and C. Barker, "Double modulation control (DMC) for dual full bridge current flow controller (2FB-CFC)," Power Electronics and Applications (EPE'15 ECCE-Europe), 2015 17th European Conference on, 2015.

Hatem Yassin Diab received his B.Sc. (Hons.) and M.Sc. degrees from the Arab Academy for Science and Technology, Cairo, Egypt, in 2009 and 2012, respectively. He is currently working on his Ph.D. degree at Staffordshire University, Stoke-on-Trent, U.K. From 2009 to 2013,

he worked as an Assistant Lecturer in the Department of Electrical and Control Engineering, College of Engineering and Technology, Arab Academy for Science and Technology, Cairo, Egypt. His research interests include power systems, control systems, automation, renewable energy technologies, HVDC, DC grids and application of power electronics in power systems.

Mostafa Ibrahim Marei received his B.Sc. (Hons.) and M.Sc. degrees in Electrical Engineering from Ain Shams University, Cairo, Egypt, in 1997 and 2000, respectively, and his Ph.D. degree in Electrical Engineering from the University of Waterloo, Waterloo, ON, Canada, in 2004. From 2004 to 2006, he was a Postdoctoral Fellow with the University

of Waterloo. Currently, he is a Professor with the Department of Electrical Power and Machines, Ain Shams University. His research interests include power electronics, distributed and renewable generation, microgrids, power quality, custom power, electrical drives, and artificial intelligent applications in power systems. Dr. Marei holds the State Incentive Award in Engineering Sciences, Academy of Scientific Research and Technology, Egypt. His biography is listed in Marquis Who's Who in the World.

Sarath B. Tennakoon received his B.Sc. degree in Electrical Engineering from the University of Moratuwa, Moratuwa, Sri Lanka; his M.Sc. degree in Electrical Engineering from the University of Aston, Birmingham, U.K.; and his Ph.D. degree in Electrical Engineering and Electronics from the University of Central Lancashire,

Lancashire, U.K. He is a Professor of power electronic systems and the Director of the Centre for Energy Efficient Systems, Staffordshire University, Stoke-on-Trent, U.K. His research interests include DC grids and HVDC, power system protection, and power electronics and harmonics.