**JPE 16-6-4**

http://dx.doi.org/10.6113/JPE.2016.16.6.2024 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Wide Input Range, 95.4% Power Efficiency DC-DC Buck Converter with a Phase-Locked Loop in 0.18 μm BCD

Hongjin Kim<sup>†</sup>, Young-Jun Park<sup>\*</sup>, Ju-Hyun Park<sup>\*</sup>, Ho-Cheol Ryu<sup>\*</sup>, Young-Gun Pu<sup>\*</sup>, Minjae Lee<sup>\*\*</sup>, Keumcheol Hwang<sup>\*</sup>, Younggoo Yang<sup>\*</sup>, and Kang-Yoon Lee<sup>\*</sup>

<sup>†,\*</sup>College of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea \*\*School of Information and Communications, Gwangju Institute of Science and Technology (GIST), Gwangju, Korea

### Abstract

This paper presents a DC-DC buck converter with a Phase-Locked Loop (PLL) that can compensates for power efficiency degradation over a wide input range. Its switching frequency is kept at 2 MHz and the delay difference between the High side driver and the Low side driver can be minimized with respect to Process, Voltage and Temperature (PVT) variations by adopting the PLL. The operation mode of the proposed DC-DC buck converter is automatically changed to Pulse Width Modulation (PWM) or PWM frequency modes according to the load condition (heavy load or light load) while supporting a maximum load current of up to 1.2 A. The PWM frequency mode is used to extend the CCM region under the light load condition for the PWM operation. As a result, high efficiency can be achieved under the light load condition by the PWM frequency mode and the delay compensation with the PLL. The proposed DC-DC buck converter is fabricated with a 0.18 µm BCD process, and the die area is 3.96 mm². It is implemented to have over a 90 % efficiency at an output voltage of 5 V when the input range is between 8 V and 20 V. As a result, the variation in the power efficiency is less than 1 % and the maximum efficiency of the proposed DC-DC buck converter with the PLL is 95.4 %.

Key words: DC-DC buck converter, Frequency mode control, High efficiency, PLL, PWM, Wide input range

# I. INTRODUCTION

In recent years, portable products have been trending towards reductions in size and weight, and they incorporate power management systems for efficient operation. The use of DC-DC buck converters has increased in various fields since advanced technology is being applied to a wider range of applications. As a result, high-efficiency DC-DC buck converters with a wide input voltage range and a wide load current range are needed [1], [2].

However, the power efficiency can be varied by switching

Manuscript received Jan. 24, 2016; accepted Jul. 10, 2016 Recommended for publication by Associate Editor Sung-Jin Choi. frequency variations and delay mismatches between the High side driver and the Low side driver due to PVT variations.

In this paper, a DC-DC buck converter with a Phase-Locked Loop (PLL) has been proposed to overcome power efficiency degradation over a wide input voltage range and a wide load current. The proposed DC-DC buck converter with a PLL operates either in the PWM or the PWM frequency mode according to the given load conditions. The proposed PLL generates a constant switching frequency which is robust to PVT variations [1]. In addition, the delay mismatch issue between the High side driver and the Low side driver according to PVT variations is automatically compensated by the PLL.

# II. ARCHITECTURE OF THE DC-DC BUCK CONVERTER WITH A PLL

A. The DC-DC Buck Converter

<sup>&</sup>lt;sup>†</sup>Corresponding Author: klee@skku.edu

Tel: +82-31-299-4954, Fax: +82-31-299-4629, Sungkyunkwan Univ.

<sup>\*</sup>College of Information and Communication Eng., Sungkyunkwan University, Korea

<sup>\*\*</sup>School of Information and Communications, Gwangju Institute of Science and Technology (GIST), Korea

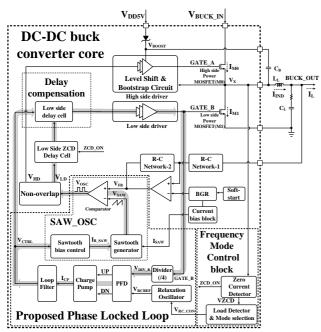

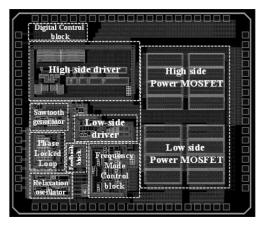

Fig. 1. The block diagram of the proposed DC-DC buck converter with the PLL.

Fig. 1 shows a block diagram of the proposed DC-DC buck converter using a PLL. The proposed DC-DC buck converter consists of a PLL, a Band-Gap Reference (BGR), an error amplifier, a frequency mode control block, High / Low side drivers, a non-overlap and a delay compensation block.

The PLL of the proposed DC-DC buck converter generates a constant switching frequency and a constant delay regardless of the effect of the external environment and PVT variations. It is designed to automatically select the PWM or the PWM frequency mode by sensing the  $V_{\rm X}$  node from the frequency mode control block according to heavy load or light load current conditions. Therefore, the proposed DC-DC buck converter operates under PWM from 300 mA to 1.2A and enters into the PWM frequency mode under 300 mA.

The input voltage,  $V_{BUCK\_IN}$ , is from 8 V to 20 V. In order to use all of the voltage ranges, the  $V_{GS}$  voltage of the High side Power MOSFET (M0) should be constant, depending on the process. The GATE\_A voltage guarantees the constancy of the  $V_{GS}$  voltage of the High side Power MOSFET (M0) when the MOSFET is operating in the saturation region. As for the High side driver, a level shifter is used to generate a higher voltage level. The  $V_{BOOST}$  voltage that is generated by the  $V_{X}$  node voltage and the Zener diode from the bootstrap circuit guarantees that the  $V_{GS}$  voltage of the High side Power MOSFET (M0) can operate in the saturation region.

The operation of the Low side driver is different depending on whether there is a heavy load or a light load. Under a heavy load, the duty is determined by the load current, and it controls the Power MOSFET. Under a light load, the reverse current is generated at the  $V_{\rm X}$  node. The reverse current that is generated is sensed by the Zero Current Detector (ZCD), and during the

on-duty state of the Low side driver, GATE\_B turns on and off to prevent a reverse current.

### B. Phase-Locked Loop

A general DC-DC buck converter has a switching frequency variation and a delay mismatch issue due to the external environment or PVT variations. These problems cause an overall reduction in the efficiency, and can result in a malfunction of the DC-DC buck converter [3].

The total loss can be described as a summation of the switching loss, conduction loss, dead-time loss, diode reverse recovery loss, and other losses of the DC-DC buck converter as shown in Eq. (1) [4], [5].

$$P_{\text{Total\_Loss}} = P_{\text{SW}} + P_{\text{Cond}} + P_{\text{Other}}$$

(1)

where, P<sub>Total\_Loss</sub>, P<sub>SW</sub>, P<sub>Cond</sub>, and P<sub>Other</sub> are the DC-DC buck converter total loss, switching loss, conduction loss, and other losses (dead-time loss, diode reverse recovery loss, gate driver loss, and etc.), respectively [4], [5].

If the switching frequency or delay is changed, the switching loss will be increased as described in Eq. (2). When the conduction loss is increased, the efficiency is reduced by Eq. (3) [4], [5].

$$P_{SW} = \frac{V_{DS} \times I_{DS}}{2} \times (T_{RISE} + T_{FALL}) \times f_{S}$$

(2)

$$P_{Cond} = \begin{pmatrix} (I_{rms,HS}^2 \times D \times R_{HS}) \\ + (I_{rms,LS}^2 \times (1 - D) \times R_{LS}) \end{pmatrix}$$

(3)

where,  $V_{DS}$ ,  $I_{DS}$ ,  $T_{RISE}$ ,  $T_{FALL}$ ,  $f_{S}$ ,  $I_{rms,HS}$ ,  $I_{rms,LS}$ ,  $R_{HS}$ ,  $R_{LS}$ , and D are the source-drain voltage, source-drain current, switching rising time, switching falling time, switching frequency,

$$\sqrt{I_{rms,HS}^2 + \frac{\Delta I_L^2}{3}}$$

,  $\sqrt{I_{rms,LS}^2 + \frac{\Delta I_L^2}{3}}$ , the High side Power MOSFET resistance, the Low side Power MOSFET resistance, and the duty cycle of the switching clock, respectively [4-5]. Therefore,

duty cycle of the switching clock, respectively [4-5]. Therefore, variations of the switching frequency and delay mismatch in the conduction loss, switching loss, dead-time loss, diode reverse recovery loss, and other losses are increased and the efficiency of the DC-DC buck converter is reduced.

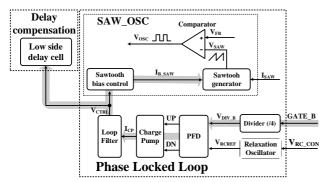

Fig. 2 shows a block diagram of the proposed PLL. It consists of a relaxation oscillator, Phase Frequency Detector (PFD), Charge Pump (CP), Loop Filter (LF), SAW\_OSC circuit, and Divider (/4). The SAW\_OSC circuit is composed of a comparator, Sawtooth bias control, and Sawtooth generator. The SAW\_OSC circuit operates as the Voltage Controlled Oscillator (VCO) of a conventional PLL.

To control the duty cycle of  $V_{OSC}$  in the PWM operation, the SAW\_OSC needs a Sawtooth generator that is different from the ring oscillator. The duty of the PWM is determined using comparator to compare  $V_{FB}$  with  $V_{SAW}$  to make the output of  $V_{OSC}$ . The loop bandwidth of the proposed PLL was determined by considering the stability characteristics of the PLL and the parameters, such as the loop filter capacitor, the resistor, the Charge Pump current ( $I_{CP}$ ), and the SAW\_OSC gain.

Fig. 2. The block diagram of the proposed PLL.

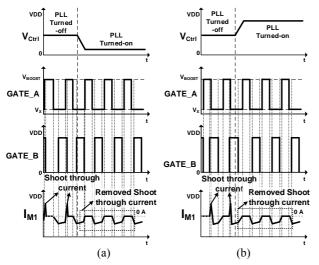

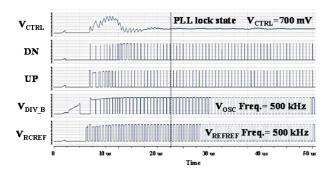

Fig. 3. The waveforms of the proposed PLL when (a)  $f_{RCREF} < f_{DIV\;B}$  (b)  $f_{RCREF} > f_{DIV\;B}.$

Fig. 3(a) and (b) show waveforms of the proposed PLL when the frequency for  $V_{DIV\_B}$  ( $f_{DIV\_B}$ ) is lower than and higher than the frequency of  $V_{RCREF}$  ( $f_{RCREF}$ ), respectively.

As shown in Fig. 3(a), if  $f_{DIV\_B}$  is higher than  $f_{RCREF}$ , the DN signal is generated, and its duration is determined by the difference in the phase and frequency. Therefore,  $V_{CTRL}$  decreases according to the DN signal. On the other hand, if  $f_{DIV\_B}$  is lower than  $f_{RCREF}$ , it generates the UP signal, as shown in Fig. 3(b). In addition,  $V_{CTRL}$  increases due to the UP signal.

The frequency of the Sawtooth generator is determined by Eq. (4). In order to generate the frequency from the PLL loop, the constant parameters  $C_{SAW}$ ,  $V_{REF\_H}$ ,  $I_{SAW}$  and  $I_{B\_SAW}$ , which are determined by the  $V_{CTRL}$  voltage, are needed [6].

If the input voltage  $V_{CTRL}$  increases, the  $I_{B\_SAW}$  current of the Sawtooth bias control block increases, and the frequency of  $V_{SAW}$  generated by the Sawtooth generator also increases. In contrast, if the  $V_{CTRL}$  voltage decreases, the  $I_{B\_SAW}$  current decreases. Thus, the frequency of  $V_{SAW}$  also decreases.

$$f_{SAW} = \frac{(I_{SAW} + I_{B\_SAW})}{C_{SAW} \times V_{REF\_H}} (Hz)$$

(4)

where, f<sub>SAW</sub>, I<sub>SAW</sub>, I<sub>B SAW</sub>, C<sub>SAW</sub>, and V<sub>REF H</sub> are the frequency

of the Sawtooth generator, Sawtooth generator default bias current, Sawtooth generator compensation bias current, Sawtooth generator capacitor, and comparator reference voltage.

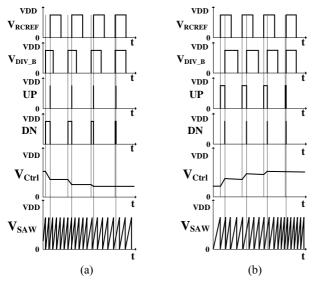

When the dead-time is increased, the reliability of the DC-DC buck converter is improved. The duration of the dead-time is related to the efficiency. If the duty of the dead-time is increased, the efficiency is decreased. On the other hand, if the duty of the dead-time is decreased, the efficiency can be improved. However, the shoot through current may flow since the duration of the dead-time is too short.

Conventional structures only use a Non-overlap circuit without delay compensation, which can cause reliability problems due to PVT variations or the external environment. It is difficult to get an optimized dead-time with conventional structures

Therefore, the proposed DC-DC buck converter senses the frequency and delay information related to the GATE\_B signal to generate dead-time. After that, the proposed DC-DC buck converter continuously compensates for variations of the dead-time through the PLL and Delay compensation.

A delay mismatch can affect the Non-overlap period for the outputs of the Low side driver and the High side driver which consist of the level shifter and bootstrap circuit. Therefore, the proposed delay mismatch compensation method controls the Low side delay cell to optimize the delay since the High side driver has a larger delay than the Low side driver.

Fig. 4(a) shows waveforms with respect to the delay mismatch between GATE\_A and GATE\_B when GATE\_B is slower than GATE\_A. The dead-time between GATE\_A and GATE\_B decreases since the delay of GATE\_B increases. A shoot through current occurs because of the reduced dead time, and this shoot through current issue can be solved by lowering the  $V_{\text{CTRL}}$  voltage of the PLL.

On the other hand, Fig. 4(b) shows waveforms with respect to the delay mismatch between GATE\_A and GATE\_B when GATE\_B is faster than GATE\_A. The dead-time between GATE\_A and GATE\_B decreases since the delay of GATE\_B decreases. In this case, the shoot through current also occurs in the same way as the case of Fig. 4(a) and this issue can be solved by increasing the  $V_{CTRL}$  voltage of the PLL.

As can be seen from the two cases explained in Fig. 4(a) and (b), when the PLL is turned off, the shoot through current occurs by variations of the dead-time. This shoot through current issue can be solved by compensating the dead-time variation between GATE\_A and GATE\_B by turning on the PLL.

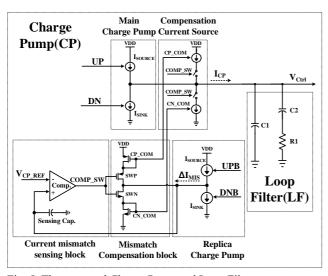

Generally, the current mismatch of the charge pump in the PLL can cause a Spur or Noise of the frequency generated by the PLL. Therefore, the proposed DC-DC buck converter

Fig. 4. The waveforms with respect to delay mismatch between GATE\_A and GATE\_B (a) when GATE\_B is slower than GATE\_A, and (b) when GATE\_B is faster than GATE\_A.

Fig. 5. The proposed Charge Pump and Loop Filter.

which adopts a PLL can have fluctuations in the switching frequency due to the current mismatch of the charge pump.

Fig. 5 shows the proposed CP and LF to solve this problem. When the CP is implemented, the current mismatch between the UP current ( $I_{SOURCE}$ ) and the DN current ( $I_{SINK}$ ) needs to be compensated. If there is a mismatch between the UP current and the DN current, there will be fluctuations in  $V_{CTRL}$  by the phase difference.

In order to solve this problem, the proposed CP uses a replica charge pump to minimize the current mismatch. This generates constant UP and DN currents from the main charge pump.

The mismatch occurs from the replica charge pump and is compensated by recharging to the compensation current source through the mismatch compensation block. By comparing  $I_{SOURCE}$  and  $I_{SINK}$ , the CP charges the current with the amount of  $\Delta I_{MIS}$  as shown in Eq. (5) from the current

Fig. 6. The block diagram of the proposed Relaxation Oscillator.

mirror [8]. As a result, the current mismatch is minimized.

$$\Delta I_{MIS} = I_{SOURCE} - I_{SINK}$$

(5)

where,  $I_{SOURCE}$  is the charge pump charging current, and  $I_{SINK}$  is the charge pump discharging current.

### C. Relaxation Oscillator

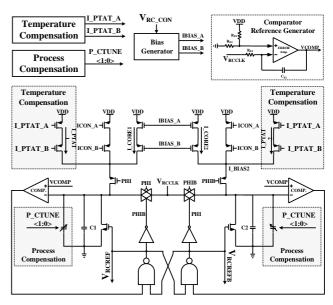

Fig. 6 shows a block diagram of the proposed relaxation oscillator. The proposed relaxation oscillator compensates for frequency variations due to process and temperature variations. At first, the input current is changed by the temperature compensation circuit according to temperature variations. This compensates the switching frequency. Secondly, the capacitor is adjusted by the process compensation circuit according to the process variation. In addition, it compensates the switching frequency.

The proposed relaxation oscillator adopts a resistor with a positive temperature coefficient (PTC).

The external factors and temperature have a minimum effect on the supply voltage and the capacitor. However, the current changes depending on the temperature as a result of the transistor characteristics. In order to compensate for this effect, a proportional to absolute temperature (PTAT) circuit and a gain-boosting circuit are adopted [9].

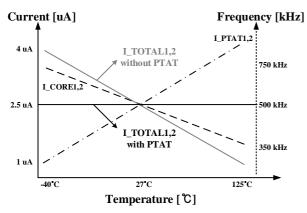

The temperature compensation circuit is designed to increase I\_PTAT1 and I\_PTAT2, according to the temperature variation. Since I\_TOTAL1 and I\_TOTAL2 are added as values of I\_CORE1, I\_PTAT1, I\_CORE2, and I\_PTAT2, the frequency can be compensated.

The relaxation oscillator frequency is decided by  $I_{REX}$  (I\_TO the TAL1, 2) and  $C_{REX}$  (C1, C2). If the frequency of the relaxation oscillator is set to high,  $C_{REX}$  decreases, but  $I_{REX}$  (I\_TOTAL1, 2) increases, which increases the current consumption. Moreover, if a high frequency is used, variations in the frequency according to PVT variations

Fig. 7. Operating principle of the proposed Temperature Compensation circuit using PTAT.

increases relative to the low frequency.

The frequency of the relaxation oscillator is proposed to oscillate at 500 kHz, which is one fourth of the switching frequency of the DC-DC buck converter. By setting the frequency of the relaxation oscillator to 500 kHz, the frequency variation is reduced in relative terms.

Fig. 7 shows the operating principle of the proposed temperature compensation circuit using PTAT. In Fig. 7, if PTAT is not applied, the frequency varies from 350 kHz to 750 kHz. In order to control the current of the relaxation oscillator, the PTAT of the BGR senses the temperature. If it is relatively low, the current flow into the core increases, and  $V_{\rm PTAT}$  decreases.

### D. Frequency Mode Control Block

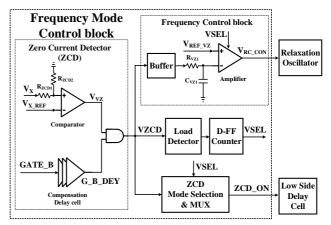

In order to achieve better results, a frequency mode control block is proposed, as shown in Fig. 8. The frequency mode control block consists of the ZCD, frequency control block, load detector, D-FF counter, ZCD mode selection and MUX [10].

Under a load current below 300 mA, the ZCD senses the  $V_X$  node so that the VSEL is changed from low to high. As a result, it can be changed to the PWM frequency mode. The frequency of the relaxation oscillator becomes faster since  $V_{RC\_CON}$  is increased. Through this high frequency, the inductor ripple can be reduced and the CCM region can be increased. As a result, the proposed PWM frequency mode increases the CCM region under a certain light load condition. When the load becomes lighter and when it enters the DCM region, the ZCD is enabled through the internal ZCD block.

Fig. 9 (a) and 9(b) show waveforms of the proposed variable switching frequency when the frequency control is turned off and on, respectively. In Fig. 9(a), the ZCD is turned off to show the difference between the PWM and the PWM frequency mode depending on the load variation. Another method that has been proposed to reduce reverse current is to change the switching frequency more quickly by controlling  $V_{RC\_CON}$ , which is the control voltage of the relaxation oscillator. In general, a low frequency affects the inductor

Fig. 8. The block diagram of the proposed Frequency Mode Control block.

Fig. 9. The waveforms of the proposed variable switching frequency when the frequency control is (a) turned off (b) and turned on.

ripple to become higher, and the reverse current of the inductor decreases.

In Fig. 9 (a), when the load condition is changed from a heavy load to a light load, the DC-DC converter is operated in the DCM region since a fixed frequency is used and inductor ripples occurs as before. In Fig. 9 (b), the DC-DC is operated in the PWM frequency mode. Under the same load conditions, the switching frequency can be increased after a certain time and the inductor ripple can be reduced so that the CCM region is increased.

When the VSEL signal shown in Fig. 9 (b) becomes high under a light load, the  $V_{RC\_CON}$  signal begins to increase and later, it settles down to a constant voltage. When the load current is also changed from a light load to a heavy load, the

Fig. 10. The chip layout pattern of the proposed DC-DC buck converter with PLL.

Fig. 11. The simulation results of the proposed PLL.

VSEL is changed to 'Low', and the switching frequency is changed from 750 kHz to 500 kHz when the voltage level of the relaxation  $V_{RC\_CON}$  is low. By the PWM frequency mode, the CCM region is extended compared to the PWM mode with a fixed frequency. Therefore, a high efficiency can be achieved by reducing the reverse current loss under light load conditions below 300 mA.

# III. EXPERIMENTAL RESULTS

The proposed DC-DC buck converter with a PLL was fabricated in 0.18  $\mu$ m BCD 1 poly 4 metal process with MIM capacitors and high sheet resistance poly resistors. Fig. 10 shows the chip layout pattern of the proposed DC-DC buck converter with a PLL, which has an area of 3.96 mm<sup>2</sup>.

Fig. 11 shows the PLL operation of the proposed DC-DC buck converter. After an initial 23  $\mu$ s, the PEN becomes 'High', and the proposed DC-DC buck converter begins to operate.

The UP signal is generated since  $V_{DIV\_B}$  is lower than  $V_{RCREF}$ , and about 30  $\mu s$  after PEN,  $V_{CTRL}$  settles to 700 mV. The  $V_{DIV\_B}$  frequency is 500 kHz after settling.

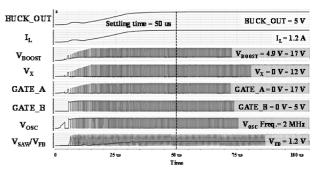

Fig. 12 shows the results of a simulation of the proposed DC-DC buck converter with a PLL. After an initial 23  $\mu$ s, when the PEN signal becomes high, the DC-DC buck converter starts to operate. When the input voltage (V<sub>BUCK\_IN</sub>) is 12 V and the load current is 1.2 A, V<sub>CTRL</sub> settles to 700 mV, and the frequency for GATE\_A and GATE\_B that is decided

Fig. 12. The simulation results of the proposed DC-DC buck converter with PLL.

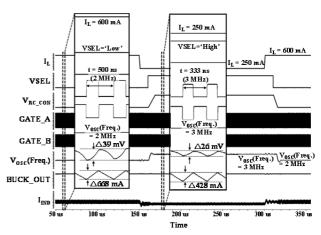

Fig. 13. The simulation results of the proposed DC-DC buck converter at PWM mode and PWM frequency operation with respect to the load current.

by the PLL is 2 MHz.  $V_{BOOST}$ , the input voltage for GATE\_A, is 4.9 V  $\sim$  16.9 V, and GATE\_B is 0 V  $\sim$  5 V. The BUCK\_OUT voltage is 5 V and the settling time of the DC-DC buck converter is about 50  $\mu$ s.

Fig. 13 shows waveforms of the proposed DC-DC buck converter under the PWM and PWM modes with respect to the load current. When the load current ( $I_L$ ) is 600 mA, the switching frequency of the DC-DC buck converter is 2 MHz and the VSEL signal is changed to Low. The ripple of the inductor current ( $I_{IND}$ ) is 668 mA and the voltage ripple of BUCK OUT is 39 mV, from Fig. 13.

On the other hand, when the load current ( $I_L$ ) is 250 mA, the switching frequency of the DC-DC buck converter is 3 MHz, and the VSEL signal is changed to High.

From Fig. 13, the ripple of the inductor current ( $I_{\rm IND}$ ) is 428 mA, and the voltage ripple of BUCK\_OUT is 26 mV. In the PWM frequency mode, the switching frequency of the DC-DC buck converter becomes faster than the PWM mode, which reduces the inductor current ( $I_{\rm IND}$ ) ripple.

Fig. 14 shows the test board of the proposed DC-DC buck converter with a PLL.

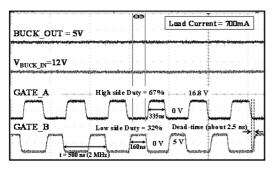

Fig. 15 shows measured waveform of the proposed DC-DC buck converter with a PLL for a load current of 700 mA. When the load current becomes 700 mA, the duty ratios for GATE\_A, GATE B, and the dead-time are 67 % (335 ns), 32 % (160 ns),

Fig. 14. The test board of the proposed DC-DC buck converter with PLL.

Fig. 15. The measured waveforms of the proposed DC-DC buck converter with PLL for a load current of 700 mA.

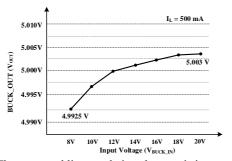

Fig. 16. The measured line regulation characteristics.

and 1 % (about 5 ns), respectively. The duty ratios of GATE\_A and GATE\_B change, and the constant dead-time period occurs according to the load current.

Fig. 16 shows the measured line regulation characteristics. The total line regulation characteristic of the DC-DC buck converter is 0.875 mV/V when changing the input voltage  $(V_{BUCK\_IN})$  from 8 V to 20 V. This means that the output voltage varies from 4.9925 V to 5.003 V.

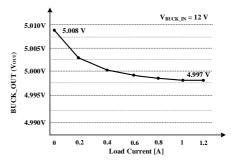

Fig. 17 shows the measured load regulation characteristics. The load regulation characteristics are measured as 11 mV/A when the load current changes from 0 A to 1.2 A, and the output varies from 4.997~V to 5.008~V.

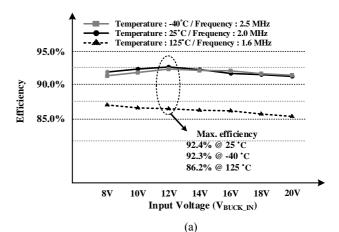

Figs. 18(a) and 18(b) show the power efficiency measured at a load current of 1.2 A with respect to a variable input voltage when the PLL compensation is turned off and on, respectively. When the PLL compensation is turned off, the switching frequency changes considerably from 1.6 MHz to 2.5 MHz with respect to temperature variations, as shown in Fig. 18(a).

Fig. 17. The measured load regulation characteristics.

Fig. 18. Power efficiency measured for the proposed DC-DC buck converter when the PLL Compensation is (a) turned off, and (b) turned on.

On the other hand, when the PLL compensation is turned on, the switching frequency is constant at 2 MHz, as shown in Fig. 18(b). Therefore, the efficiency is almost the same (within a 1 % error) for all of the cases at 25 °C, -40 °C and, 125 °C, as shown in Fig. 18(b).

This causes a frequency problem and a delay mismatch issue that decreases the efficiency of the DC-DC buck converter. As shown in Fig. 18(a) and 18(b), when the PLL is turned off and the input voltage is 12 V, the power efficiency difference is 6.3 %; and when the PLL is turned on and the input voltage is 12 V, the power efficiency difference is 0.9 %.

According to Eq. (1), (2) and (3), when the PLL

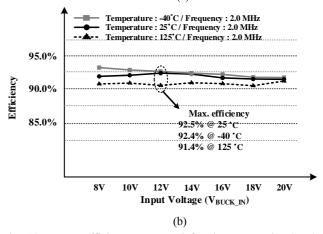

Fig. 19. Power efficiency of the proposed DC-DC buck converter with respect to the various load currents when the PLL compensation is (a) turned off, and (b) turned on.

compensation is turned off and the temperature is 25°C, the calculated conduction loss and the switching loss are 115.79 mW and 36.8 mW, respectively. However, the conduction loss and switching loss are 155 mW and 206 mW at 125 °C. The efficiency is decreased by the changed frequency and the delay mismatch at 125 °C. When the dead-time decreases or disappears, the diode reverse recovery loss and switching loss increase degrading the power efficiency.

Figs. 19(a) and (b) show the power efficiency measured at an input voltage of 12 V with respect to a variable load current when the PLL compensation is turned off and on, respectively. When the PLL compensation is off, the frequency changes considerably from 1.6 MHz to 2.5 MHz with respect to temperature variations, as shown in Fig. 19(a).

As shown in Fig. 19(a), when the PLL is turned off and the load current is 0.5 A, the power efficiency difference is 7.7 %; and when the PLL is turned on and the load current is 0.5 A, the power efficiency difference is 1 %. On the other hand, when the PLL compensation is turned on, the switching frequency becomes constant at 2 MHz due to the PLL

TABLE I

THE MEASUREMENTS FOR THE PROPOSED DC-DC BUCK

CONVERTER WITH PLL

| Parameter                         | Value                                                   |        |          |  |  |  |

|-----------------------------------|---------------------------------------------------------|--------|----------|--|--|--|

| $I_{\rm L}$                       | 0.15 A                                                  | 0.5 A  | 1.2 A    |  |  |  |

| BUCK_OUT                          | 5 V                                                     | 5 V    | 5 V      |  |  |  |

| Output Power                      | 750 mW                                                  | 2.5 W  | 6 W      |  |  |  |

| I <sub>IN</sub>                   | 66.7 mA                                                 | 214 mA | 537.4mA  |  |  |  |

| V <sub>BUCK_IN</sub>              | 12 V                                                    | 12 V   | 12 V     |  |  |  |

| Input Power                       | 833.8 mW                                                | 2.62 W | 6.4938 W |  |  |  |

| Sub-block<br>Power<br>consumption | 37 mW                                                   | 40 mW  | 45 mW    |  |  |  |

| Quiescent<br>Current              | 4.5mA (@ No Load)                                       |        |          |  |  |  |

| Power<br>MOSFET Ron               | 50 mohm<br>(W: 120 mm / L: 1.3 um, Load current: 0.5 A) |        |          |  |  |  |

| Total loss                        | 83.8 mW                                                 | 120 mW | 493.8 mW |  |  |  |

| Efficiency                        | 89.9 %                                                  | 95.4 % | 92.5 %   |  |  |  |

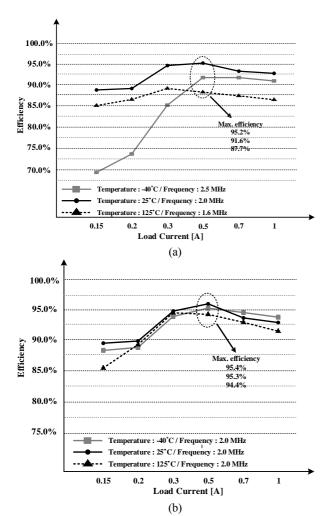

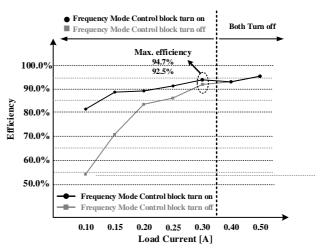

Fig. 20. Power efficiency measured for the proposed DC-DC buck converter with PLL when the Frequency Mode Control block is turned on or off.

operation, as shown in Fig. 19(b).

As shown in Fig. 19(a), the power efficiency is decreased by the change of the switching frequency and delay mismatch at 125 °C and -40 °C. When the dead-time decreases or disappears, the diode reverse recovery loss and switching loss increase degrading the power efficiency.

Table I shows the measured details according to the load current ( $I_L$ ) of the proposed DC-DC buck converter with a PLL. When the load current is 1.2 A, the output power is 6 W, and the input power, including the sub-block power consumption and loss, is 6.4938 W. Thus, the efficiency is 92.5 %

Fig. 20 shows the power efficiency measured at an input voltage of 12 V with respect to a variable load current when the frequency mode control block is turned on and off,

| TABLE II                              |

|---------------------------------------|

| A SUMMARY OF THE MEASURED PERFORMANCE |

| Reference               | [11]        | [12]              | [13]               | This<br>Work      |

|-------------------------|-------------|-------------------|--------------------|-------------------|

| Technology              | 1 μm<br>SOI | 0.35<br>μm<br>BCD | 0.18<br>μm<br>CMOS | 0.18<br>μm<br>BCD |

| Input Voltage range (V) | 20          | 2.9-4.5           | 2.7-5.5            | 8-20              |

| Switching freq. (MHz)   | 1           | 1                 | 2.5                | 2                 |

| Output DC voltage (V)   | 5           | 4.9               | 0 – 5              | 5                 |

| Max. Load current (A)   | 1.2         | 0.3               | 2                  | 1.2               |

| Value of Indictor (μH)  | 4.7         | 10                | 1                  | 2.2               |

| Duty Ratio (%)          | N/A         | N/A               | N/A                | 25~6<br>2         |

| Max. PCE (%)            | 91          | 90.5              | 91                 | 95.4              |

| Die Area (mm²)          | 6           | 2.94              | 4.13               | 3.96              |

respectively. When the frequency mode control block is turned on, the proposed DC-DC buck converter has an efficiency of over 80 % under a light load through the operation of the PWM frequency mode.

As shown in Table II, the proposed DC-DC buck converter is designed to generate an output of 5 V under a wide input voltage range of 8 V to 20 V compared to the reference [11]-[13].

In particular, a load current range of 0 A to 1.2 A is even wider when compared to reference [11].

A smaller inductor value is used, compare with references [11], [12], by adopting a high switching frequency. In addition, the maximum Power Conversion Efficiency (PCE) is 95.4 %, which is superior to that in references [11]-[13].

# IV. CONCLUSION

In this paper, a DC-DC buck converter using a PLL is proposed to generate a constant switching frequency and to compensate for the delay mismatch between the High side and Low side drivers. It also controls the operation mode automatically from the PWM mode to the PWM frequency mode by sensing the load current in order to achieve a high efficiency. The PWM frequency mode is used to extend the CCM region under a light load for the PWM operation. As a result, a high efficiency can be achieved under the light load condition by the PWM frequency mode and delay compensation with a PLL.

Therefore, the proposed DC-DC buck converter has an efficiency of over 80% under light loads (under 300 mA) through the operation of the PWM frequency mode.

The proposed chip was fabricated with a  $0.18~\mu m$  BCD process, and the area is  $3.96~mm^2$ . The maximum power efficiency of the proposed DC-DC buck converter with a PLL is 95.4~%.

### ACKNOWLEDGMENT

This work was supported by Institute for Information & communications Technology Promotion(IITP) grant funded by the Korea government(MSIP) (No.B0717-16-0057).

This work was supported by IDEC(IPC, EDA Tool, MPW).

### REFERENCES

- [1] H. J. Kim, H.-G. Park, J.-H. Jang, Y.-J. Park, Y. G. Pu, and K.-Y. Lee, "High power efficiency, 8 V~20 V input range dc-dc buck converter with phase-locked loop," in *Proc.* 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), pp. 1772-1777, 2015.

- [2] B. Sahu, and G. A. Rincon-Mora, "A low voltage, dynamic, noninverting synchronous buck-boost converter for portable applications," *IEEE Trans. Power Electron.*, Vol. 19, No. 2, pp. 443-442, Mar. 2004.

- [3] Z. Xu, F. Xu, and F. Wang, "Junction temperature measurement of IGBTs using short-circuit current as a temperature-sensitive electrical parameter for converter prototype evaluation," *IEEE Trans. Ind. Electron.*, Vol. 62, No. 6, pp. 3419-3429, Jun. 2015.

- [4] Texas Instruments, "Power loss calculation with common source inductance consideration for synchronous buck converters," SLPA009A, June 2011 [Revised July 2011].

- [5] J. Klein, "Synchronous buck MOSFET loss calculations with excel model," Fairchild Corp., San Jose, CA, Tech. Rep. AN-6005, Nov. 21. 2014.

- [6] S. W. Hong, H. J. Kim, J.-S. Park, Y. G. Pu, J. Cheon, D.-H. Han, and K.-Y. Lee, "Secondary-side LLC resonant controller IC with dynamic PWM dimming and dual-slope clock generator for LED backlight units," *IEEE Trans. Power Electron.*, Vol. 26, No. 11, pp. 3410-3422, Nov. 2011.

- [7] S. L. Gierkink, "Low-spur, low-phase-noise clock multiplier based on a combination of PLL and recirculating DLL with dual-pulse ring oscillator and self-correcting charge pump," *IEEE J. Solid-State Circuits*, Vol. 43, No. 12, pp. 2967-2976, Dec. 2008.

- [8] H. Huh, Y. Koo, K.-Y. Lee, Y. Ok, S. Lee, D. Kwon, J. Lee, J. Park, K. Lee, D.-K. Jeong, and W. Kim, "Comparison frequency doubling and charge pump matching techniques for dual-band fractional- frequency synthesizer," *IEEE J. Solid-State Circuits*, Vol. 40, No. 11, pp. 2228-2235, Nov. 2005.

- [9] Q. Zhou, L. Li, and G. Chen, "An RC oscillator with temperature compensation for accurate delay control in electronic detonators," in *Proc. Electron Devices and Solid-State Circuits(EDSSC)*, pp. 274-277, 2009.

- [10] C. F. Lee and P. K. T. Mok, "On-chip current sensing technique for CMOS monolithic switch-mode power converters," in *Proc. IEEE Int. Symp. Circuits and Systems* (*ISCAS*), Vol. 5, pp. 265-268, 2002.

- [11] Z. Sun, L. Siek, R. P. Singh, and M. Je, "A fixed-frequency hysteretic controlled buck dc-dc converter with improved load regulation," in *Proc. IEEE Int. Symp. Circuits and Systems (ISCAS)*, pp. 954-957, 2014.

- [12] S.-W. Hong, and G.-H. Cho, "Inverting buck-boost dc-dc converter for mobile AMOLED display with real-time self-tuned minimum power-loss tracking scheme," in *Proc. IEEE Custom Integrated Circuits Conf. (CICC)*, pp. 1-4, 2014

- [13] P. Malcovati, M. Belloni, F. Gozzini, C. Bazzani, and A.

Baschirotto, "A 0.18µm CMOS 91%-efficiency 0.1-to-2A scalable buck-boost dc-dc converter for LED drivers," *Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, pp. 280-282, Feb. 2012.

Hongjin Kim received his B.S. degree from the Department of Electronic Engineering of Chungju University, Chungju, Korea, in 2010. He is presently working towards his Ph.D. degree in the College of Information and Communication Engineering of Sungkyunkwan University, Suwon, Korea. His current research interests include CMOS power management ICs and mixed signal

RF transceivers, integrated circuits.

Young-Jun Park received his B.S. degree in Electronics Engineering from Kumoh National Institute of Technology, Gumi, Korea, in 2013. He is presently working towards his combined M.S. and Ph.D. degree in Electronics and Computer Engineering from Sungkyunkwan University, Suwon, Korea. His current research interests include

the design of power management integrated circuits for high efficiency and wireless power transfer systems.

Ju-Hyun Park received his B.S. degree from the Department of Electronic Engineering of the Hankuk University of Foreign Studies (HUFS), Seoul, Korea, in 2013. He is presently working towards his M.S. degree in the School of Information and Communication Engineering of Sungkyunkwan University, Suwon, Korea.

His current research interests include power management ICs and CMOS RF transceivers.

Ho-Cheol Ryu received his B.S. degree from the Department of Electronic Engineering of Sungkyunkwan University, Suwon, Korea, in 2015, where he is presently working towards his combined M.S. and Ph.D. degree in the School of Information and Communication Engineering. His current research interests include CMOS RF transceivers and

phase-locked loops.

communications.

Minjae Lee (S'03–M'08) received his B.S. and M.S. degrees in Electrical Engineering, from Seoul National University, Seoul, Korea, in 1998 and 2000, respectively. He received his Ph.D. degree in Electrical Engineering from the University of California, Los Angeles, CA, USA, in 2008.

In 2000, he was a consultant with GCT Semiconductor, Inc., San Jose, CA, USA, and Silicon Image Inc., Sunnyvale, CA, USA, designing analog circuits for wireless communication, and digital signal processing blocks for Gigabit Ethernet. In 2001, he joined Silicon Image Inc., developing serial ATA products. In August 2008, he joined Agilent Technologies, Santa Clara, CA, USA, where he was involved in the development of next-generation high-speed ADCs and DACs. Since 2012, he has been with the School of Information and Communications, Gwangju Institute of Science and Technology, Gwangju, Korea, where he is presently working as an Assistant Professor. Dr. Lee was a recipient of a 2007 Best Student Paper Award at the VLSI Circuits Symposium in Kyoto, Japan.

**Keumcheol Hwang** received his B.S. degree in Electronics Engineering from Pusan National University, Busan, Korea, in 2001; and his M.S. and Ph.D. degrees in Electrical and Electronic Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea in 2003 and 2006, respectively. From 2006 to

2008, he was a Senior Research Engineer at Samsung Thales, Yongin, Korea, where he was involved in the development of various antennas including multiband fractal antennas for communication systems, Cassegrain reflector antennas and slotted waveguide arrays for tracking radars. He was an Associate Professor in the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, Korea, from 2008 to 2014. In 2015, he joined the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, Korea, where he is presently working as an Associate Professor. His current research interests include advanced electromagnetic scattering and radiation theory and its application, the design of multi-band/broadband antennas and radar antennas, and optimization algorithms for electromagnetic applications. Prof. Hwang is a Life Member of KIEES, a Senior Member of IEEE and a Member of IEICE.

Younggoo Yang (S'99-M'02) was born in Hamyang, Korea, in 1969. He received his Ph.D. degree in Electrical and Electronic Engineering from the Pohang University of Science and Technology (Postech), Pohang, Korea, in 2002. From 2002 to 2005, he was with Skyworks Solutions Inc., Newbury Park, CA, USA, where he designed power

amplifiers for various cellular handsets. Since March 2005, he has been with the School of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea, where he is presently working as an Associate Professor. His current research interests include power amplifier design, RF transmitters, RFIC design, integrated circuit design for RFID/USN systems, and the modeling of high power amplifiers and devices.

**Kang-Yoon Lee** received his B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering of Seoul National University, Seoul, Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was a Manager of the Analog Division and worked on the design

of CMOS frequency synthesizers for CDMA/PCS/PDC and

single-chip CMOS RF chip sets for W-CDMA, WLAN, and PHS. From 2005 to 2011, he was with the Department of Electronics Engineering, Konkuk University, Seoul, Korea, as an Associate Professor. Since 2012, he has been with School of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea, where he is presently working as an Associate Professor. His current research interests include the implementation of power integrated circuits, CMOS RF transceivers, analog integrated circuits, and analog/digital mixed-mode VLSI system design.