JPE 17-1-12

# An Improved Switching Topology for Single Phase Multilevel Inverter with Capacitor Voltage Balancing Technique

Soundar Rajan Ponnusamy<sup>†</sup>, Manoharan Subramaniam<sup>\*</sup>, Gerald Christopher Raj Irudayaraj<sup>\*\*</sup>, and Kaliamoorthy Mylsamy<sup>\*\*\*</sup>

<sup>†,\*\*</sup>Dept. of Electrical & Electronics Engineering, PSNA College of Engineering & Technology, Dindigul, India \*Dept. of Electrical & Electronics Engineering, Karpagam College of Engineering, Coimbatore, India \*\*\*Dept. of Electrical & Electronics Engineering, Dr. Mahalingam College of Engineering & Technology, India

#### Abstract

This paper presents a new cascaded asymmetrical single phase multilevel converter with a reduced number of isolated DC sources and power semiconductor switches. The proposed inverter has only two H-bridges connected in cascade, one switching at a high frequency and the other switching at a low frequency. The Low Switching Frequency Inverter (LSFI) generates seven levels whereas the High Switching Frequency Inverter (HSFI) generates only two levels. This paper also presents a solution to the capacitor balancing issues of the LSFI. The proposed inverter has lot of advantages such as reductions in the number of DC sources, switching losses, power electronic devices, size and cost. The proposed inverter with a capacitor voltage balancing algorithm is simulated using MATLAB/SIMULINK. The switching logic of the proposed inverter with a capacitor voltage balancing algorithm is developed using a FPGA SPATRAN 3A DSP board. A laboratory prototype is built to validate the simulation results.

Key words: Harmonics, H-bridge, Multilevel inverter, PWM

## I. INTRODUCTION

Multilevel converters are mainly utilized to synthesis stair-case voltage waveforms. The required multi-staircase output voltage is obtained by combining several dc voltage sources [1]-[3]. Batteries, solar cells, fuel cells and ultra-capacitors are the most common independent sources used. One of the important applications of multilevel converters focuses on medium and high-power conversions. Nowadays, there are three commercial topologies for multilevel voltage-source inverters: neutral point clamped (NPC), cascaded H-bridge (CHB), and flying capacitors (FCs)

[4]-[7]. Among these inverter topologies, the cascaded multilevel inverter provides the highest output voltage and number of power levels (13.8 kV, 30 MVA), and the highest reliability due to its modular topology [8]-[9].

There are a large number of cascaded multilevel inverters proposed in the literature [11]-[17]. CHB inverters require additional isolated DC sources, in order to increase the number of levels. However, each additional isolated DC source increases the complexity of the control strategy, especially in grid connected renewable energy systems [13]. The literature has proposed a solution for CHB inverters with a minimum number of DC sources and power electronic devices [13]. However, the inverter proposed in [13] has a drawback in terms of the capacitor voltage balancing in its lower inverter. In order to solve the capacitor voltage balancing issue in the lower inverter, an additional DC-DC converter with the multi output proposed in [14] has been used. However, this increases the complexity of the control strategy and the size of the total system. Furthermore, the inverters proposed in [13], [15] use a bidirectional switch, which introduces spikes into the output

Manuscript received Jun. 7, 2016; accepted Nov. 2, 2016

Recommended for publication by Associate Editor Liqiang Yuan.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: soundar\_psr@rediffmail.com

Tel: +918056365222, PSNA College of Engineering and Technology \*Dept. of Electrical and Electronics Engineering, Karpagam College of Engineering, India

<sup>\*\*</sup>Dept. of Electrical and Electronics Engineering, PSNA College of Engineering and Technology, India.

<sup>\*\*\*</sup>Dept. of Electrical & Electronics Engineering, Dr. Mahalingam College of Engineering & Technology, India

voltage [16], [17]. These spikes can only be eliminated by using a hefty snubber. This hefty snubber increases the losses in the system and hence reduces the efficiency.

This paper proposes a novel single phase cascaded multilevel inverter with minimum number of isolated DC sources and power electronic devices. Furthermore, the proposed inverter does not require any additional converter circuits to achieve capacitor voltage balancing and it is free from voltage spikes during commutation.

Section II describes the circuit topology and modes of operation of the proposed multilevel inverter. In Section III, the capacitor voltage balancing technique of the proposed inverter is discussed. Sections IV and V presents the simulation and experimental results. Section VI concludes the paper.

## II. PROPOSED CIRCUIT TOPOLOGY

A cascaded multilevel inverter is made up of a series connected single full bridge inverter, which has its own isolated dc bus. This multilevel inverter can generate a nearly sinusoidal waveform voltage from several separate dc sources, such as fuel cells, batteries, solar cells, ultra capacitors, etc. This converter does not need any transformers, clamping diodes or flying capacitors. Each level can generate five different voltage outputs  $+2V_{dc}$ ,  $+V_{dc}$ , 0,  $-2V_{dc}$  and  $-V_{dc}$  by connecting the dc sources to the ac output side through different combinations of the four switches. The output voltage of a multilevel inverter is the sum of all of the individual inverter outputs. Each of the H-bridge's switches at the fundamental frequency, and each of the H-bridge units produce a quasi-square waveform by phase-shifting the switching time of its positive and negative phase legs. Further, each of the switching device always conducts for 180° (or half a cycle) regardless of the pulse width of the quasi-square wave so that this switching method results in equalization of the current stress in all of the active devices. This inverter topology is suitable for high voltage and high power inversion because of its ability of synthesize waveforms with a better harmonic spectrum and a lower switching frequency. Considering its simplicity and advantages, the cascaded H-bridge topology is selected for the presented work. A multilevel inverter has four advantages over the conventional bipolar inverter. Initially, the voltage stress on each of the switches is decreased due to the series connection of the switches. Therefore, the rated voltage and the total power of the inverter can be safely increased. Second, the rate in the change of the voltage (dv/dt) is decreased due to the lower voltage swing of each switching cycle. Then, the harmonic distortion is reduced due to the increased number of output levels. Finally, reductions in the acoustic noise and electromagnetic interference (EMI) are obtained. Fig 1 shows the circuit topology of the proposed cascaded H-bridge multilevel inverter. The proposed inverter has only two

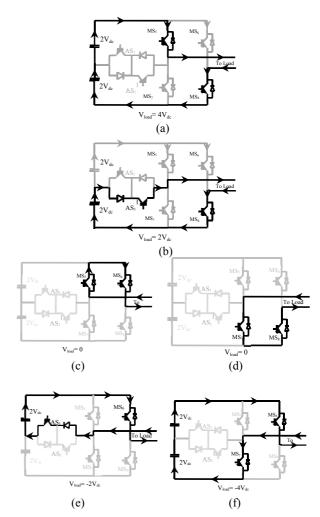

Fig. 1. Proposed H bridge multilevel inverter.

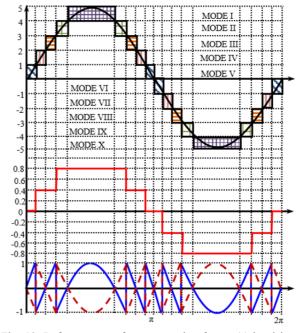

Fig. 2. Modes of operation of five level inverter.

|                   | SWITCH          | ING STA         | TES OF          | 5 LEVE          | L H BRI         | DGE INV       | VERTER    |

|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------|-----------|

| V <sub>low</sub>  | MS <sub>5</sub> | MS <sub>6</sub> | MS <sub>7</sub> | MS <sub>8</sub> | AS <sub>1</sub> | $AS_1^{\top}$ | Reference |

| $4V_{dc}$         | ON              | OFF             | OFF             | ON              | OFF             | OFF           | Fig. 2(a) |

| $2V_{dc}$         | OFF             | OFF             | OFF             | ON              | OFF             | ON            | Fig. 2(b) |

| 0                 | ON              | ON              | OFF             | OFF             | OFF             | OFF           | Fig. 2(c) |

| 0                 | OFF             | OFF             | ON              | ON              | OFF             | OFF           | Fig. 2(d) |

| -2V <sub>dc</sub> | OFF             | ON              | OFF             | OFF             | ON              | OFF           | Fig. 2(e) |

| -4V <sub>dc</sub> | OFF             | ON              | ON              | OFF             | OFF             | OFF           | Fig. 2(f) |

TABLE I

Switching States of 5 Level H Bridge Inverter

H-bridges connected in cascaded (high switching frequency inverter and low switching frequency inverter). As a result, it requires only two isolated DC sources. It is very important to note that the magnitude of the two isolated DC sources should be in the ratio of 1:2 like those in [18]-[20].

The LSFI is capable of generating seven levels whereas the HSFI is capable of generating a two level output. In total the load receives a fifteen level voltage waveform. Figure 2 shows the various modes of operation of the LSFI.

Table I shows the switching states of a LSFI with only one bidirectional switch (with two capacitors), which is capable of generating five levels. When the number of bidirectional switches is increased to two, the number of capacitors increases to three and the number of levels increases to seven. However, this introduces a capacitor voltage balancing problem. This is detailed in section III.

### A. Capacitor Voltage Balancing Issues

Since the H-bridge contains a series of capacitors (the number of capacitors depends on the number of required levels), balancing them is an important issue in the proposed inverter. This section describes how capacitor imbalances occur during the switching operation of the proposed inverter and possible solutions to overcome these issues.

1) Capacitor voltage balancing in a lower 5 level inverter:

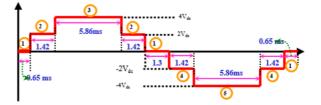

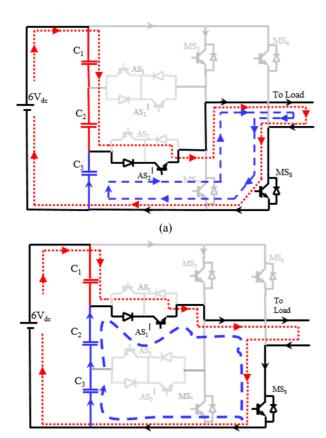

The expected five level output voltage waveform of a lower H-bridge inverter with five switching states is shown in Fig. 3. The modes of charging and discharging of the two capacitors ( $C_1$  and  $C_2$ ) are shown in Fig. 4 (the red dotted line shows the charging state of the capacitor, and the blue dashed line shows the discharging state of the capacitor). The charging and discharging of the two capacitors for five different switching states along with the time interval are detailed in Table II.

From Table II it is clear that the DC link capacitors are charging and discharging only during switching states 2 and 4. The time durations of switching states 2 and 4 in a cycle are 2.84 milliseconds each (refer to Fig. 3 and Table II).

2) Capacitor Voltage Balancing in a Lower 7 Level Inverter:

Fig. 3. Switching states of H bridge with two DC link capacitors.

Fig. 4. Charging and discharging of Capacitors  $C_1$  and  $C_2$  (a) During switching states 2 (b) During switching state 4.

TABLE II CAPACITOR CHARGING STATUS DURING EACH SWITCHING STATES FOR TWO DC LINK CAPACITORS

| FOR TWO DC LINK CAPACITORS |                 |                 |                 |                 |                 |                              |                          |                          |                  |

|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------------------|--------------------------|--------------------------|------------------|

| Switching<br>State         | MS <sub>5</sub> | MS <sub>6</sub> | MS <sub>7</sub> | MS <sub>8</sub> | AS <sub>1</sub> | AS <sub>1</sub> <sup>1</sup> | Status of C <sub>1</sub> | Status of C <sub>2</sub> | Time<br>Duration |

| 1                          | ON ON           |                 | OFF O           |                 | OFF             | OFF                          | NC                       | NC                       | 2.6 ms           |

|                            | OFF             | OFF             | ON              | ON              | OFF             | OFF                          | NC                       | NC                       | 2.0 115          |

| 2                          | OFF             | OFF             | OFF             | ON              | OFF             | ON                           | Charging                 | Discharging              | 2.84 ms          |

| 3                          | ON              | OFF             | OFF             | ON              | OFF             | OFF                          | NC                       | NC                       | 5.86 ms          |

| 4                          | OFF             | ON              | OFF             | OFF             | ON              | OFF                          | Discharging              | Charging                 | 2.84 ms          |

| 5                          | OFF             | ON              | ON              | OFF             | OFF             | OFF                          | NC                       | NC                       | 5.86 ms          |

| NC-                        | No ch           | ange            | (or) N          | ot Cha          | Total           | Time                         | 20 ms                    |                          |                  |

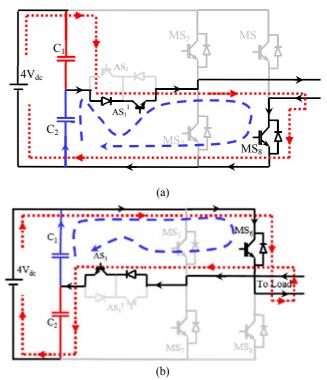

The expected seven level output voltage waveform of the lower H-bridge inverter with seven switching states is as

Fig. 5. Switching states of H bridge with three DC link capacitors.

(b) Fig. 6. Charging and discharging of capacitors C1, C2 and C3 (a) during switching state 2 (b) during switching state 3.

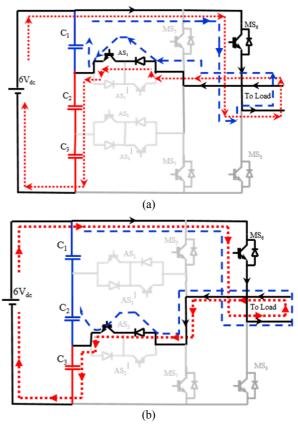

shown in Fig. 5. The modes of charging and discharging of the three capacitors ( $C_1$ ,  $C_2$  and  $C_3$ ) are shown in Fig. 6 and Fig. 7 (the red dotted line shows the charging state of the capacitor, and the blue dashed line shows the discharging state of the capacitor). The charging and discharging of the three capacitors for seven different switching states along with the time interval are detailed in Table III.

During switching state 2, the capacitors  $C_1$  and  $C_2$  are in the charging state (red dotted line) and the capacitor  $C_3$  is in the discharging state (blue dashed line), as shown in Fig. 6(a). The duration of the charging and discharging are given in table III. Similarly, during switching state 3, the capacitor  $C_1$ charges whereas the capacitors  $C_2$  and  $C_3$  discharge, as shown in Fig. 6(b). The duration of the charging and discharging of

Fig. 7. Charging and discharging of capacitors  $C_1$ ,  $C_2$  and  $C_3$  (a) during switching state 5 (b) during switching state 6.

TABLE III CAPACITOR CHARGING STATUS DURING EACH SWITCHING STATES FOR THREE DC LINK CAPACITORS

| Switching<br>State | MS <sub>5</sub> | 5 MS6  | MS <sub>7</sub> | MS <sub>8</sub> | AS <sub>1</sub> | AS1 | AS <sub>2</sub> | AS <sub>2</sub> <sup>1</sup> | Status of<br>capacitors |                       |                       | Time<br>Duration |

|--------------------|-----------------|--------|-----------------|-----------------|-----------------|-----|-----------------|------------------------------|-------------------------|-----------------------|-----------------------|------------------|

| State              |                 |        |                 |                 |                 |     |                 |                              | $\mathbf{C}_{1}$        | <b>C</b> <sub>2</sub> | <b>C</b> <sub>3</sub> | Duration         |

| 1                  | ON              | ON     | OFF             | OFF             | OFF             | OFF | OFF             | OFF                          | NC                      | NC                    | NC                    | 1.04             |

| 1                  | OFF             | OFF    | ON              | ON              | OFF             | OFF | OFF             | OFF                          | NC                      | NC                    | NC                    | 1.84 ms          |

| 2                  | OFF             | OFF    | OFF             | ON              | OFF             | OFF | OFF             | ON                           | Î                       | 1                     | Ļ                     | 1.92 ms          |

| 3                  | OFF             | OFF    | OFF             | ON              | OFF             | ON  | OFF             | OFF                          | 1                       | Ļ                     | V                     | 2.26 ms          |

| 4                  | ON              | OFF    | OFF             | ON              | OFF             | OFF | OFF             | OFF                          | NC                      | NC                    | NC                    | 4.9 ms           |

| 5                  | OFF             | ON     | OFF             | OFF             | ON              | OFF | OFF             | OFF                          | ļ                       | 1                     | 1                     | 1.92 ms          |

| 6                  | OFF             | ON     | OFF             | OFF             | OFF             | OFF | ON              | OFF                          | ļ                       | ļ                     | 1                     | 2.26 ms          |

| 7                  | OFF             | ON     | ON              | OFF             | OFF             | OFF | OFF             | OFF                          | NC                      | NC                    | NC                    | 4.9 ms           |

| NC = N             | <b>↑</b> Ch     | arging | "↓              | Disc            | hargii          | ng  |                 | Tota                         | l                       | 20 ms                 |                       |                  |

the capacitors are detailed in Table III.

During switching state 5, the capacitor  $C_1$  discharges whereas the capacitors  $C_2$  and  $C_3$  are in the charging mode, as shown in Fig. 7(a). Similarly, during switching state 6,  $C_1$  and  $C_2$ discharge whereas  $C_3$  charges, as shown in Fig. 7(b). The duration of the charging for all three capacitors is detailed in Table III. From Table III, it can be seen that the total charging and discharging time of the capacitors  $C_1$  and  $C_3$  is 4.18 milliseconds, whereas the total charging time of the capacitor  $C_2$  is 3.84 milliseconds and the discharging time of capacitor  $C_2$  is 4.52 milliseconds. Thus, over a cycle (for 50 Hz, 20 milliseconds), the net voltage in the capacitor  $C_2$  decreases, whereas the charge on  $C_1$  and  $C_3$  is balanced. Hence, a capacitor balancing algorithm is needed in the case of a seven-level inverter.

# III. BALANCING CAPACITOR VOLTAGE USING A MULTILEVEL INVERTER

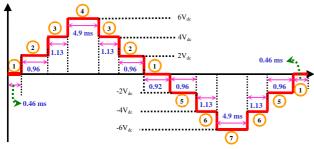

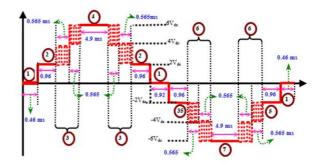

In order to solve the capacitor voltage balancing issues in seven-level inverters, it is necessary to reduce the discharging time of the capacitor  $C_2$ , so that the net voltage in the capacitor over a cycle is positive. This should be done during switching states 3 and 6 where the  $C_2$  voltage decreases. Hence, a modified switching topology is proposed to increase the voltage across  $C_2$ . Fig. 8 shows the proposed modified switching topology. It can be noticed in Fig. 8 that the proposed inverter voltage can be switched between two levels during switching states 3 and 5.

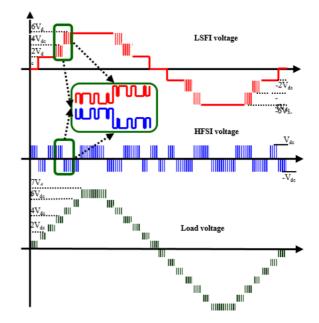

During switching state 3, the inverter voltage is switched between  $2V_{dc}$  and  $4V_{dc}$  for the first half of the duration and between  $4V_{dc}$  and  $6V_{dc}$  for the second half of the duration. This reduces the duration of switching state 3 in the  $4V_{dc}$ level where the capacitor C<sub>2</sub> discharges. By doing this, during most of the time in switching state 3, the proposed inverter voltage is in either the  $2V_{dc}$  level or the  $6V_{dc}$  level, which increases the charging time of C<sub>2</sub>. Fig. 9 shows the waveforms of the HSFI voltage, LSFI voltage and load voltage of the modified switching topology.

The load voltage waveform is derived by instantaneously adding the LSFI and HSFI voltages. It can be further observed in Fig. 9 (the zoomed section) that during switching state 3 of the lower inverter, the HSFI should switch in a manner that is opposite that of the LSFI. This is very important for making the load voltage switch between  $4V_{dc}$ and  $5V_{dc}$ , and between  $5V_{dc}$  and  $6V_{dc}$ . TABLE IV gives the switching states of the proposed inverter when it is driven by the modified switching topology.

The total reference waveform is generated as shown in Fig. 10 and defined in (1):

$$U_{ref} = A\sin(\omega t) \tag{1}$$

The reference waveform for the high switching frequency inverter is generated using the following expressions:

$$U_{ref,s} = \frac{U_{ref}}{5} \tag{2}$$

$$Z_1 = \begin{cases} 1 & \text{if } U_{ref} > 0 \\ 0 & \text{if } U_{ref} < 0 \end{cases}$$

(3)

Fig. 8. Proposed modified switching topology.

Fig. 9. Voltage waveforms of modified switching topology.

Fig. 10. Reference waveform generation for an 11 level inverter (high frequency inverter bridge).

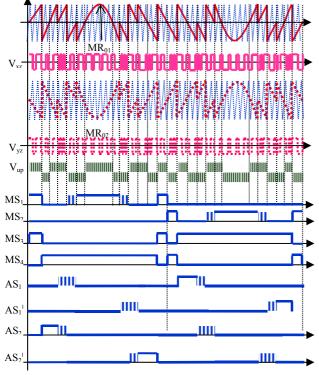

Fig. 11. Modified modulation strategy of the proposed inverter.

$$V_{LSFI \text{ expected}} = \left( round \left( \frac{\left| U_{ref,s} \right|}{0.4} \right) * 0.4 * Z_1 \right) + \left( round \left( \frac{\left| U_{ref,s} \right|}{-0.4} \right) * 0.4 * Z_1 \right) \right)$$

$$V_{HSFI,ref} = 5 * \left( U_{ref,s} - V_{LSFI, expected} \right)$$

(5)

Equation (3) is a simple zero crossing detector, equation (4) gives the expected output of the lower switching frequency inverter bridge, and equation (5) is a mathematical representation of the high switching frequency inverter reference waveform. The outputs of equations (4) and (5) for an 11 level inverter are shown in Fig. 10 (b) and Fig. 10 (c). The above equations can be used for high switching frequency inverter levels by simply changing the value of A. For example, A = 7 for 15 levels, A = 9 for 19 levels, A = 11 for 23 levels just to mention a few.

Fig. 11 illustrates the generation of switching signals for the HSFI and LSFI. The signal  $MR_{01}$  is a modified reference signal which is used to generate switching signals for the switches  $MS_1$  and  $MS_4$ , and a modified reference signal  $MR_{02}$ is used to generate switching signals for the switches  $MS_3$ and  $MS_4$ . The highlighted portions in Table IV indicate that both of the inverters (HSFI and LSFI) are switched at high frequencies but in opposite manners i.e. when the HSFI voltage oscillates between zero and  $-V_{dc0}$ , the LSFI voltage should be

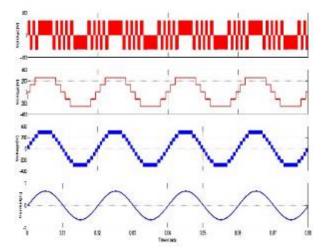

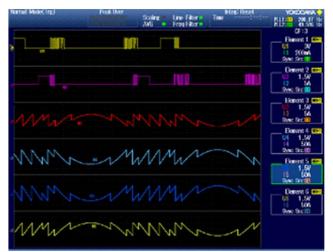

Fig. 12. (a) Voltage across the HSFI  $V_{up}$  (b) Voltage across the LSFI  $V_{low}$  (c) Voltage across the load (11 Levels) (d) Load Current waveform for modulation index  $M_a$ =1.

Fig. 13. (a) Voltage across the HSFI  $V_{up}$  (b) Voltage across the LSFI  $V_{low}$  (c) Voltage across the load (15 Levels) (d) Load Current waveform for modulation index  $M_a$ =1.

oscillating between  $4V_{dc0}$  and  $6V_{dc0}$  so that the net voltage across the load is between  $4V_{dc0}$  and  $5V_{dc0}$ . Further when the proposed inverter is driven from the modified switching topology,  $C_2$  will be charging more than  $C_1$  and  $C_3$ . Hence, the voltage across  $C_2$  has to be sensed, and based on its instantaneous value, either the generalized simplified switching algorithm or the modified modulation strategy has to be used.

### **IV. SIMULATION RESULTS**

To validate the proposed inverter topology, simulations were carried out for the proposed inverter in Matlab/Simulink. The generalized PWM modulation technique is implemented in simulations of up to 15 levels and it can be extended to any number of required levels. The conditions for the simulation and experiment are same. Simulation results obtained for 11 level and 15 level inverters are shown in Fig. 12 and Fig. 13. The above results are obtained by considering that all of the

## An Improved Switching Topology for ...

TABLE IV

Switching States of Modified Modulation Strategy for Fifteen Level Inverter

|        |        |        |        |                 |        |                 |        |                 |        |                 |        |      |                                                                                         | Output load volta                     | ge                                                        |  |

|--------|--------|--------|--------|-----------------|--------|-----------------|--------|-----------------|--------|-----------------|--------|------|-----------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------|--|

|        | HSFI   | Switch | es     | LSFI Switches   |        |                 |        |                 |        |                 |        | Mode | $V_{dc1} = V_{dc2} = V_{dc3} = 2V_{dc0} \ i.e \left[\frac{V_{dcn}}{V_{dc0}} = 2\right]$ |                                       |                                                           |  |

| $MS_1$ | $MS_2$ | $MS_3$ | $MS_4$ | MS <sub>5</sub> | $MS_6$ | MS <sub>7</sub> | $MS_8$ | AS <sub>1</sub> | $AS_1$ | AS <sub>2</sub> | $AS_2$ |      | V <sub>up</sub>                                                                         | V <sub>low</sub>                      | $\mathbf{V}_{total} = \mathbf{V}_{up} + \mathbf{V}_{low}$ |  |

| ON     | OFF    | OFF    | ON     | ON              | OFF    | OFF             | ON     | OFF             | OFF    | OFF             | OFF    | I    | $0 \leftrightarrow V_{dc0}$                                                             | $6V_{dc0}$                            | $6V_{dc0} \leftrightarrow 7V_{dc0}$                       |  |

| OFF    | ON     | ON     | OFF    | ON              | OFF    | OFF             | ON     | OFF             | OFF    | OFF             | OFF    | п    | $-V_{dc0} \leftrightarrow 0$                                                            | $6V_{dc0}$                            | $5V_{dc0} \leftrightarrow 6V_{dc0}$                       |  |

| ON     | OFF    | OFF    | ON     | ON/OFF          | OFF    | OFF             | ON     | ON/OFF          | ON     | OFF             | OFF    | ш    | $0 \leftrightarrow V_{dc0}$                                                             | $4V_{dc0} \leftrightarrow 6V_{dc0}$   | $4V_{dc0} \leftrightarrow 5V_{dc0}$                       |  |

| OFF    | ON     | ON     | OFF    | OFF             | OFF    | OFF             | ON     | OFF             | ON/OFF | OFF             | ON/OFF | IV   | $-V_{dc0} \leftrightarrow 0$                                                            | $2V_{dc0} \leftrightarrow 4V_{dc0}$   | $3V_{dc0} \leftrightarrow 4V_{dc0}$                       |  |

| ON     | OFF    | OFF    | ON     | OFF             | OFF    | OFF             | ON     | OFF             | OFF    | OFF             | ON     | v    | $0 \leftrightarrow V_{dc0}$                                                             | $2V_{dc0}$                            | $2V_{dc0} \leftrightarrow 3V_{dc0}$                       |  |

| OFF    | ON     | ON     | OFF    | OFF             | OFF    | OFF             | ON     | OFF             | OFF    | OFF             | ON     | VI   | $0 \leftrightarrow -V_{dc0}$                                                            | $2V_{dc0}$                            | $V_{dc0} \leftrightarrow 2V_{dc0}$                        |  |

| ON     | OFF    | OFF    | ON     | ON              | ON     | OFF             | OFF    | OFF             | OFF    | OFF             | OFF    | VП   | $V_{dc0} \leftrightarrow 0$                                                             | 0                                     | $0 \leftrightarrow V_{dc0}$                               |  |

| OFF    | ON     | ON     | OFF    | OFF             | OFF    | ON              | ON     | OFF             | OFF    | OFF             | OFF    | VIII | $0 \leftrightarrow -V_{dc0}$                                                            | 0                                     | $0 \leftrightarrow -V_{dc0}$                              |  |

| ON     | OFF    | OFF    | ON     | OFF             | ON     | OFF             | OFF    | ON              | OFF    | OFF             | OFF    | IX   | $V_{dc0} \leftrightarrow 0$                                                             | $-2V_{dc0}$                           | $-V_{dc0} \leftrightarrow -2V_{dc0}$                      |  |

| OFF    | ON     | ON     | OFF    | OFF             | ON     | OFF             | OFF    | ON              | OFF    | OFF             | OFF    | X    | $0 \leftrightarrow -V_{dc0}$                                                            | $-2V_{dc0}$                           | $-2V_{dc0} \leftrightarrow -3V_{dc0}$                     |  |

| ON     | OFF    | OFF    | ON     | OFF             | ON     | OFF             | OFF    | ON/OFF          | OFF    | ON/OFF          | OFF    | XI   | $-V_{dc0} \leftrightarrow 0$                                                            | $-2V_{dc0} \leftrightarrow -4V_{dc0}$ | $-3V_{dc0} \leftrightarrow -4V_{dc0}$                     |  |

| OFF    | ON     | ON     | OFF    | OFF             | ON     | ON/OFF          | OFF    | OFF             | OFF    | ON/OFF          | OFF    | хп   | $0 \leftrightarrow V_{dc0}$                                                             | $-4V_{dc0} \leftrightarrow -6V_{dc0}$ | $-4V_{dc0} \leftrightarrow -5V_{dc0}$                     |  |

| ON     | OFF    | OFF    | ON     | OFF             | ON     | ON              | OFF    | OFF             | OFF    | OFF             | OFF    | хш   | $V_{dc0} \leftrightarrow 0$                                                             | $-6V_{dc0}$                           | $-5V_{dc0} \leftrightarrow -6V_{dc0}$                     |  |

| OFF    | ON     | ON     | OFF    | OFF             | ON     | ON              | OFF    | OFF             | OFF    | OFF             | OFF    | XIV  | $0 \leftrightarrow -V_{dc0}$                                                            | $-6V_{dc0}$                           | $-6V_{dc0} \leftrightarrow -7V_{dc0}$                     |  |

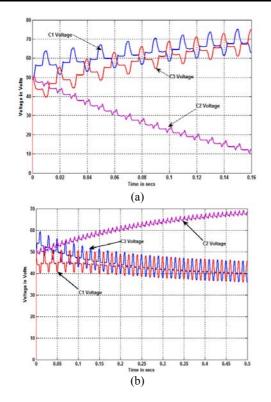

Fig. 14. (a) Voltage across the capacitors of LSFI Bridge when driven from generalized PWM modulation, (b) Voltage across the capacitors of LSFI Bridge when driven from modified modulation strategy, (c) Voltage across the capacitors of LSFI Bridge when driven from combined modulation strategy.

capacitors of the H bridge inverter have an individual isolated DC source. However, in order to feed the proposed H bridge inverter with a single isolated DC source, a combination of the generalized PWM switching strategy and the modified modulation strategy proposed in section III is used. Fig. 14 (a) shows the capacitor voltages of the proposed inverter

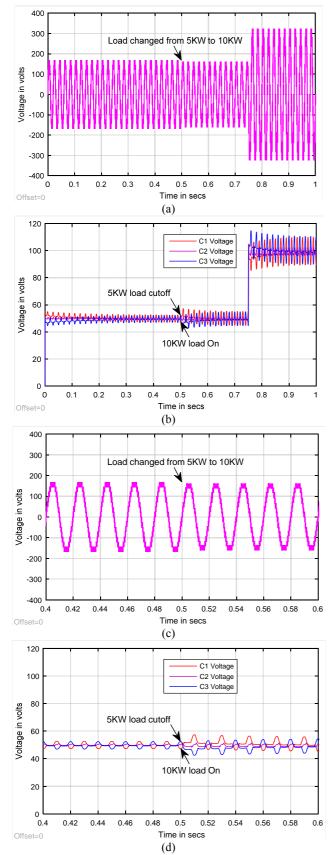

Fig 15. (a) Load voltage, (b) Capacitor voltages, (c) Zoomed load voltage and (d) Zoomed capacitor voltage, when the load changes from 5 KW to 10 KW at 0.5 secs.

when it is driven by the generalized PWM switching strategy. It can be observed from Fig. 13 that the capacitor voltage of C2 continuously discharges whereas those of C1 and C3 charge continuously.

Fig. 14 (b) shows the voltage across the capacitors of the proposed H-bridge when it is driven by the modified modulation strategy. It can be observed from Fig. 14 (b) that the voltage across the capacitor  $C_2$  increases when compared to the voltages across  $C_1$  and  $C_3$ . Similarly Fig. 14 (c) illustrates the voltages across the capacitors of the proposed H-bridge when it is driven by the combined generalized and modified switching strategy, where the capacitor voltages are close to each other.

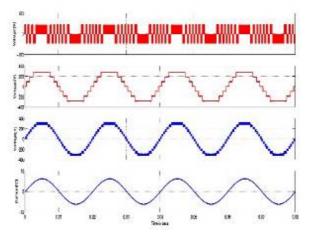

The charging and discharging of the capacitor voltage depend on the load current. Hence, to validate the proposed switching scheme in the presence of the load variations, simulation studies and experimental validations are carried out for step changes in the load.

In the simulation, two loads are considered (one with 5 KW and the other with 10 KW). At 0.5 seconds a 5 KW load is switched off and a 10 KW load is switched on. The results of the simulation are presented below.

From figure 15 (b) it is evident that even when there is a sudden load change the capacitor voltage takes a slight deviation and returns to its original state. A zoomed version of the above results is presented in figure 15 (c) and figure 15 (d).

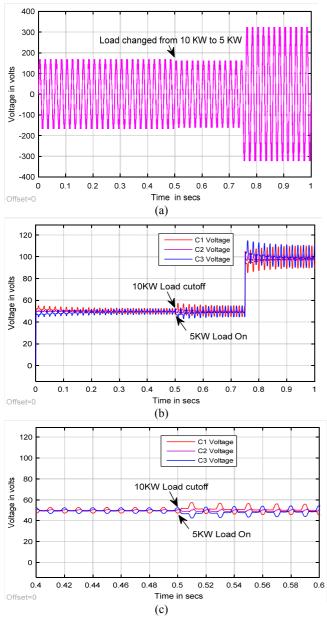

The above procedure is repeated for a drop in the load (i.e. from 10 KW to 5 KW). Figure 16 (a) shows a load voltage waveform when the load is reduced from 10 KW to 5 KW. During the same instants, the capacitor voltages were observed and shown in figure 16 (b). A zoomed version is shown in figure 16 (c).

### V. EXPERIMENTAL RESULTS

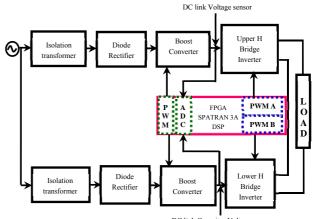

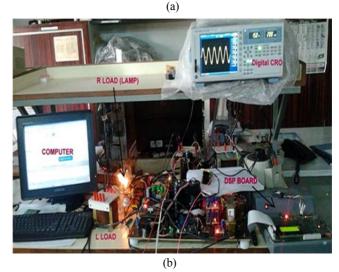

Fig. 17 shows a schematic diagram and a photograph of the laboratory developed hardware setup of the proposed inverter for 15 levels. The HSFI and LSFI are made up of MKI 80-06T6K series IGBTs.

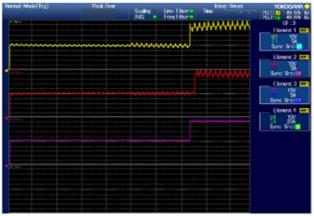

The auxiliary switch used in the LSFI is a FIO50-12BD bidirectional device. The gate driving signals were developed using a FPGA SPATRAN 3A DSP (Digital Signal Processor). The program for the FPGA SPATRAN 3A DSP was composed with code composer studio and Matlab/Simulink. The figures starting from 18 onwards show experimental results of a 7-level and 15-level inverter with a modulation index of 1 and a switching frequency of 10 KHz.

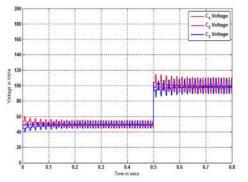

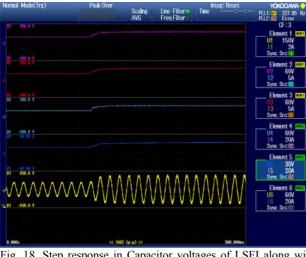

In order to validate the proposed multilevel inverter driven by the proposed algorithm, a step change in the reference values of the lower DC link capacitors was given at 0.5 seconds (i.e. a change from 50 Volts to 100 Volts). Similarly a step change in the upper boost converter was given at 0.5 seconds (i.e. from 25 Volts to 50 Volts) in order to keep the ratio between

Fig 16. (a) Load voltage, (b) Capacitor voltages, (c) Zoomed capacitor voltage, when the load is suddenly reduced at 0.5 secs from 10KW to 5KW.

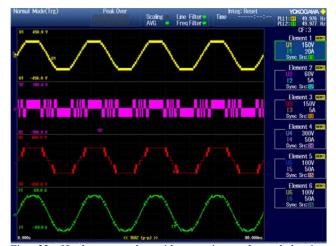

the LSFI and HSFI DC link voltages as two. Fig. 18 shows experimental waveforms of the upper and lower capacitor voltages due to a step change in their reference values (i.e. the upper capacitor voltage is changed from 25 Volts to 50 Volts, and the lower capacitor voltages are changed from 50 Volts to 100 Volts). Fig. 19 shows the corresponding changes in the HSFI and LSFI voltages along with the load voltage.

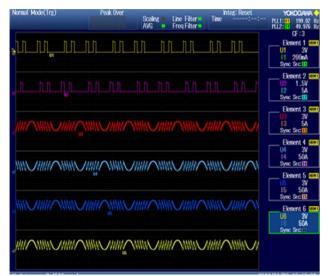

Fig. 20 shows the switching pulses generated for the HSFI and LSFI without the capacitor voltage balancing algorithm. Meanwhile, Fig. 21 shows the switching pulses generated for the HSFI and LSFI with the capacitor voltage balancing algorithm. It can be observed from these two figures that the auxiliary switches switch at a high frequency when the

TABLE V Simulation Parameters

| Series RLC load 1                           |               |

|---------------------------------------------|---------------|

| Active power P (W)                          | 50e2          |

| Inductive reactive power QL (positive var)  | 100           |

| Capacitive reactive power Qc (negative var) | 0             |

| Series RLC load 2                           |               |

| Active power P (W)                          | 100e2         |

| Inductive reactive power QL (positive var)  | 100           |

| Capacitive reactive power Qc (negative var) | 0             |

| C1, C2, C3 Capacitors                       | 2200 µF       |

| Snubber resistance Rs (Ohms)                | 1e5           |

| Solver - stiff/TR-BDF2                      | ode23tb       |

| Туре                                        | Variable-step |

| Max, Min, Initial step size                 | Auto          |

| Relative tolerance                          | 1e-4          |

| Absolute tolerance                          | Auto          |

DC link Capacitor Voltage sensor

Fig. 17. (a) Schematic diagram for the hardware Setup of the proposed inverter (15 Levels), (b) hardware Setup of the proposed inverter.

Fig. 18. Step response in Capacitor voltages of LSFI along with load voltage for a 7-level inverter without filter.

Fig. 19. Step response in capacitor voltages of HSFI and LSFI along with HSFI, LSFI and load voltage waveform.

Fig. 20. Switching pulses and reference waveforms (a) Auxiliary switch 1 (b) Auxiliary switch 2 (c, d, e and f) Reference waveforms of the HSFI [Without capacitor voltage balancing].

Fig. 21. Switching pulses and reference waveforms (a) Auxiliary switch 1 (b) Auxiliary switch 2 (c, d, e and f) Reference waveforms of the HSFI [With capacitor voltage balancing].

Fig. 22. Hardware results with capacitor voltage balancing algorithm (a) Voltage across the load (15 Levels) (b)Voltage across the HSFI  $V_{up}$  (c) Voltage across the LSFI  $V_{low}$  (d) Load Current waveform for modulation index  $M_a$ =1.

Fig 23. Experimental Capacitor Voltages when load changes from 5 KW to 10 KW.

TABLE VI Experimental Parameters

| 5 KW                |

|---------------------|

| 10 KW               |

| 2200 μF             |

| MKI 80-06T6K series |

| FIO50-12BD          |

| FPGA SPATRAN 3A DSP |

|                     |

capacitor voltage balancing algorithm is used. Fig. 22 shows the output voltage of the proposed inverter when driven by the capacitor voltage balancing algorithm. It also shows the HSFI and LSFI waveforms along with the load current waveform. It can be observed that the LSFI waveform is switched at a high frequency for a small duration.

The simulation procedure for the load variations was also attained in the prototype model and the results were observed. Figure 23 shows the hardware results of the capacitor voltages when the load is suddenly increased from 5 KW to 10 KW.

### VI. CONCLUSIONS

Multilevel inverters offer enhanced output waveforms with a minimum of THD. This paper proposes a novel single phase cascaded multilevel inverter with a minimum number of isolated DC sources and power electronics devices. Further a novel voltage balancing technique is developed to balance the LSFI capacitor voltages. The performance of the proposed inverter is tested in a simulation platform using MATLAB/SIMULINK. To validate the simulation, a laboratory prototype is built and controlled using a FPGA SPARTAN 3A DSP board. The developed inverter does not require any additional multi output DC-DC converters for balancing the capacitor voltages since the algorithm does the balancing. The simulation and experimental results are a perfect match. The proposed inverter offers several advantages such as a minimum number of isolated DC sources and power electronic devices, reductions in the switching losses, size and cost, and increased efficiency. Thus, the proposed inverter can be used for medium and high power applications.

#### REFERENCES

- A. Matsa, I. Ahmed, and M. A. Chaudhari, "Optimized space vector pulse-width modulation technique for a five-level cascaded H-bridge inverter," *Journal of Power Electronics*, Vol. 14, No. 5, pp. 937-945, Sep. 2014.

- [2] N. S. Choi, J. G. Cho, and G. H. Cho, "A general circuit topology of multilevel inverter," in 22<sup>nd</sup> Annual IEEE

Power Electronics Specialists Conference (PESC), pp. 96-103, Jun. 1991.

- [3] S. Ogasawara and H. Akagi, "Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters," in *IEEE Industry Applications Society Annual Meeting*, pp. 965-970, Oct. 1993.

- [4] M. Kaliamoorthy and V. Rajasekaran, "A novel MPPT scheme for solar powered boost inverter using evolutionary programming," in *International Conference on Recent Advancements in Electrical, Electronics and Control Engineering* (ICONRAEeCE), Dec. 2011.

- [5] B. R. Lin, H. K. Chiang, and S. L. Wang, "Interleaved ZVS DC/DC converter with balanced input capacitor voltages for High-voltage applications," *Journal of Power Electronics*, Vol. 14, No. 4, pp. 661-670, Jul. 2014.

- [6] R. W. Menzies, P. Steimer, and J. K. Steinke, "Five-level GTO inverters for large induction motor drives," *IEEE Trans. Ind. Appl.*, Vol. 30, No. 4, pp. 938-944, Jul./Aug. 1994.

- [7] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter industry applications," *IEEE Trans. Ind. Appl.*, Vol. IA-17, No. 5, pp. 518-523, Sep. 1981.

- [8] M. Kaliamoorthy, S. Himavathi, and A. Muthuramalingam, "DSP based implementation of high performance flux estimators for speed sensorless induction motor drives using TMS320F2812," in *India International Conference* on Power Electronics (IICPE), Dec. 2006.

- [9] M. Kaliamoorthy, V. Rajasekaran, and I. G. C. Raj, "Single-phase fifteen-level grid-connected inverter for photovoltaic system with evolutionary programming based MPPT algorithm," *Solar Energy*, Vol. 105, pp. 314-329, Jul. 2014.

- [10] M. Kaliamoorthy, V. Rajasekaran, I. G. C. Raj, and L. H. T. Raj, "Experimental validation of a cascaded single phase H-bridge inverter with a simplified switching algorithm," *Journal of Power Electronics*, Vol. 14, No. 3, pp. 507-518, May 2014.

- [11] E. Babaei, S. Laali, and Z. Bayat, "A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches," *IEEE Trans. Ind. Electron.*, Vol. 62, No. 2, pp. 922-929, Feb. 2015.

- [12] E. Babaei, S. Laali, and S. Alilu, "Cascaded multilevel inverter with series connection of novel H-Bridge basic units," *IEEE Trans. Ind. Electron.*, Vol. 61, No. 12, pp. 6664-6671, Dec. 2014.

- [13] M. Kaliamoorthy, V. Rajasekaran, I. G. C. Raj, and L. H. T. Raj, "Generalised hybrid switching topology for a single-phase modular multilevel inverter," *IET Power Electronics*, Vol. 7, No. 10, pp. 2472-2485, Oct. 2014.

- [14] A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg, "Multi-output DC–DC converters based on diode-clamped converters configuration: topology and control strategy," *IET Power Electronics*, Vol. 3, No. 2, pp. 197-208, Mar. 2010.

- [15] J. N. Reddy, M. K. Moorthy, and D. V. A. Kumar. "Control of grid connected PV cell distributed generation systems," in *IEEE Region 10 Conference (TENCON)*, pp. 1-6, Nov. 2008.

- [16] M. Venturini, "A new sine wave in, sine wave out, conversion technique eliminates reactive elements," in *Proceedings of POWERCON*, pp. E3:1-E3:15, 1980.

- [17] P. W. Wheeler and D. A. Grant, "A low loss matrix converter for AC variable-speed drives," in 5<sup>th</sup> European

Conference on Power Electronics and Applications, pp. 27-32, Sep. 1993.

- [18] N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 6, pp. 2111-2123, Jun. 2010.

- [19] S.-J. Park, F.-S. Kang, M. H. Lee, and C.-U. Kim, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Trans. Power Electron.*, Vol. 18, No. 3, pp. 831-843, May 2003.

- [20] N. A. Rahim, J. Selvaraj, and C. Krismadinata, "Five-level inverter with dual reference modulation technique for grid-connected PV system," *Renewable Energy*, Vol. 35, No. 3, pp. 712-720, Mar. 2010.

**Soundar Rajan Ponnusamy** was born on July 15, 1982. He received his B..E., . degree in Electrical and Electronics Engineering from Madurai Kamaraj University, Madurai, India, in 2003; and his M.Tech., High Voltage Engineering from SASTRA University, , India, in 2005. He is presently working towards his and pursuing Ph.D., in

Power Electronics and Drives at Anna University, Chennai, India. He is working as an Assistant Professor in the Department of Electrical and Electronics Engineering at the PSNA College of Engineering and Technology, Dindigul, India. His current research interest includes power electronics and drives, multilevel inverters, AC drives and their applications.

**Manoharan Subramaniam** received his B.E., in Electrical and Electronics Engineering from the Government College of Technology, Coimbatore, India, in 1997; his M.E degree in Electrical Machines from the PSG College of Technology, Coimbatore, India, in 2004; and his Ph.D. degree in Electrical Machines and Drives from Anna

University, Chennai, India, in 2010. He is presently working as a Professor and as the Head of the Department of Electronics and Instrumentation Engineering at the Karpagam College of Engineering, Coimbatore, India. His current research interests include electrical machines, power electronics, control systems and renewable energy.

Gerald Christopher Raj Irudayaraj was born on January 7, 1977. He received his B.E., in Electrical and Electronics Engineering from Madurai Kamaraj University, Madurai, Tamil Nadu, India, in 1999; and his M.E and Ph.D. degrees in Power Electronics and Drives from Anna University, Chennai, India, in 2006 and 2013,

respectively. He is presently working as an Associate Professor in the Department of Electrical and Electronics Engineering at the PSNA College of Engineering and Technology, Dindigul, India. His current research interests include power electronics and drives, current source inverters, AC drives and their applications.

Kaliamoorthy Mylsamy received his B E in Electrical and Electronics Engineering at Madras University, Chennai, India, in 1999, M.Tech degree in Electrical Drives and Control from Pondicherry University, Puducherry, India, in 2006; and his Ph.D. degree from Anna University, Chennai, India, in 2015. He was a gold medalist for the

academic years 2004-2006. He has one decade of teaching experience for undergraduate and post graduate students of electrical and electronics engineering. He is presently working as an Associate Professor in the Department of Electrical and Electronics Engineering, Dr. Mahalingam College of Engineering and Technology, Coimbatore, India. His current research interests include alternative energy sources, fuel cells, energy conversion, multilevel inverters, the analysis and control of power electronics devices, power quality and active harmonic analysis.