JPE 17-5-24

https://doi.org/10.6113/JPE.2017.17.5.1372 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Automotive High Side Switch Driver IC for Current Sensing Accuracy Improvement with Reverse Battery Protection

Jaehyun Park\* and Shihong Park†

\*,†Department of Electrical and Electronics Engineering, Dankook University, Yongin, Korea

#### **Abstract**

This paper presents a high-side switch driver IC capable of improving the current sensing accuracy and providing reverse battery protection. Power semiconductor switches used to replace relay switches are encumbered by two disadvantages: they are prone to current sensing errors and they require additional external protection circuits for reverse battery protection. The proposed IC integrates a gate driver and current sensing blocks, thus compensating for these two disadvantages with a single IC. A p-sub-based 90-V 0.13- $\mu$ m bipolar-CMOS-DMOS (BCD) process is used for the design and fabrication of the proposed IC. The current sensing accuracy (error  $\leq \pm 5\%$  in the range of 0.1 A-6.5 A) and the reverse battery protection features of the proposed IC were experimentally tested and verified.

**Key words:** Automotive current sensing, Automotive power switch driver, Current sensing accuracy, High side gate driver, Reverse battery protection

# I. INTRODUCTION

In recent years, automotive switches have undergone transitions from the conventional relay switches to power semiconductor switches owing to their high stability and reliability and low mechanical noise [1].

A power semiconductor switch offers the advantages of SenseFET-based current sensing without requiring additional external sensing circuits. However, the current automotive power semiconductor SenseFETs are flawed because of a large current sensing error range of  $\pm 20\%$ . Efforts are underway to reduce the error rates by using additional calibration circuits. However, the wide range of error of the SenseFETs hampers such error reduction attempts [2]-[5]. Moreover, parasitic diodes are structurally generated within a power semiconductor, unlike the relay switch circuits that are mechanically cut off in the turn-off state. Not only do such parasitic diodes cause output current turn-off delays, they also induce high currents in the reverse direction to the load

and driver IC in the reverse battery mode. These factors are detrimental to the reliability and stability of the power semiconductor switches. Currently, an additional protection circuit is used to protect the automotive power semiconductor modules from such negative factors [6]-[11]. These drawbacks bring about undesirable consequences such as lower current sensing accuracy, increased complexity, inferior performance, and price rise, and impede the conversion transition from relay switches into power semiconductor switches.

In an attempt to eliminate such hampering factors, this paper proposes an automotive power semiconductor switch driver IC. The proposed driver IC integrates the drive block and the current sensing block into a single IC, and is expected to contribute to improving the current sensing accuracy and enabling reverse battery protection. In addition, instead of expensive SenseFETs, a low-cost general MOSFET is used as the power MOSFET. The proposed IC is fabricated via a 90-V 0.13-µm bipolar-CMOS-DMOS (BCD) process, and its characteristics are experimentally verified.

#### II. CONVENTIONAL CIRCUITS

A. Current Sensing Methods

Manuscript received Feb. 2, 2017; accepted May 21, 2017 Recommended for publication by Associate Editor Sang-Won Yoon.

<sup>†</sup>Corresponding Author: shihong@dankook.ac.kr

Tel: +82-031-8005-3652, Fax: +82-031-8005-4149, Dankook University

\*Dept. of Electron. and Electrical Eng., Dankook University, Korea

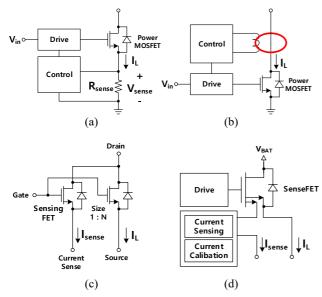

Fig. 1. Current sensing circuits (a) using sense resistor, (b) using Hall-effect sensor, (c) SenseFET, (d) current sensing circuit using SenseFET.

Fig. 1 depicts three current sensing methods widely used in automotive switches. Fig. 1(a) shows a current sensing method that uses the voltage generated by releasing the load current to the sensing resistor. However, when operated under high-current conditions, it is rarely used due to the efficiency drop and the alterations in the dynamic properties of the load due to the series resistance. Fig. 1(b) shows a current sensing method using a Hall-effect sensor, characterized by high precision and linearity. Other advantages are high reaction speed and the ability to operate even when the drive circuit is insulated. Although it has such attractive properties, it is more cost-intensive than other methods. Fig. 1(c) and (d) show a structure of SenseFET and a current sensing method using a SenseFET. In this method, a 1/N-scaled SenseFET is built in parallel with the power MOSFET, and it senses currents having steady ratios with respect to the output current. This method is widely used in many fields owing to its ability to sense current without additional external devices or efficiency loss [2]-[5], [12]-[14].

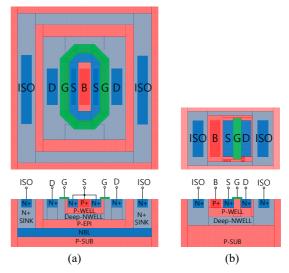

However, when applied to automotive semiconductor switches, the current sensing based on the SenseFET technique has an error range of ±20% [3]-[5], which can be attributed to the structural characteristics of the DMOS used as the power semiconductor switch. DMOS requires a low turn-on resistance to drive a high-current device under high breakdown voltages, resulting in a structure with a narrow channel and thick epi-layers. Moreover, it is relatively large and complicated as compared with the CMOS structure as shown in Fig. 2. Such a structure is not suitable for a SenseFET-type parallel structure, in terms of matching properties. Consequently, a DMOS-based SenseFET is prone to large deviations of the current sensing ratio of SenseFET depending on the magnitude of current, the

Fig. 2. FET-n type structure (p-sub based) (a) LDMOS, (b) CMOS.

temperature, and the process. Therefore, if a system requires a high current sensing accuracy, it uses a method that constructs the sensing circuit by adding a calibration circuit to a DMOS-structured SenseFET [12], [13], [20].

However, owing to the suboptimal matching properties of the SenseFETs, its yield is not high enough for mass production, resulting in uncompetitive prices in comparison with the general power MOSFET applications.

Unlike the DMOS structure encumbered by these disadvantages, the low-voltage CMOS employed in analog circuits has excellent matching properties, resulting in a narrow circuit sensing error range for parallel structures such as SenseFETs [15], [16].

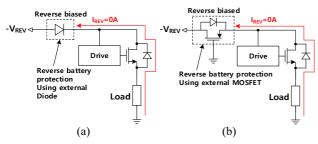

# B. Reverse Battery Protection

The application of a power semiconductor switch to an automotive module will most likely lead to failure of the driver module and load in the reverse battery mode because of the body diode of the power MOSFET. As reliability and stability are absolute priorities for automotive modules, the modules are constructed with additional reverse battery protection circuits as illustrated in Fig. 3. When driving a load of a few hundred milliamperes, the reverse battery protection circuit can be easily integrated into the drive block. However, in the case of loads with magnitudes of several amperes, the reverse battery protection device gets bigger accordingly, which makes it difficult to integrate it as an embedded element. This problem can be addressed by using an additional external device to implement the protection circuit [6]-[11], [19].

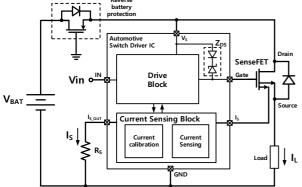

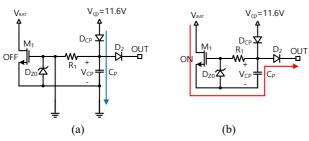

Fig. 4 shows the structural diagram of an automotive power semiconductor switch module applicable to driving loads of several amperes or more. It is composed of a DMOS-structured SenseFET for current sensing and an additional external resistance and diode or MOSFET for

Fig. 3. Reverse battery protection circuits (a) using diode, (b) using power MOSFET.

Fig. 4. Conventional automotive power switch module structure with reverse battery protection [3], [7].

reverse battery protection. This type of circuit structure is prone to current sensing errors and requires an external device for reverse battery protection.

#### III. PROPOSED CIRCUITS

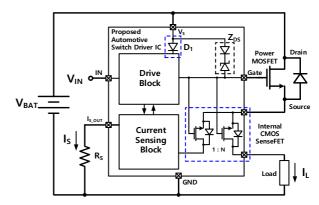

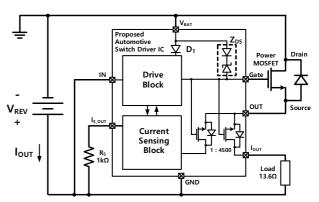

Fig. 5 shows a structural diagram of the proposed automotive power semiconductor switch module. The proposed switch driver IC comprises a SenseFET using a reverse-connected n-type MOSFET for current sensing. Additionally, the proposed module completely blocks the reverse current flow to the load in the reverse battery mode using the body diode while operating the SenseFET current sensor. The inner diode D1 completely blocks the reverse battery current, which flows into the drive and current sensing blocks.

The n-type MOSFET used in the proposed switch module is a low-voltage CMOS device. Not only does it have a simple structure compared to the DMOS, and a high device conformity, it is also characterized by a very low resistance per unit area, compared to the high-voltage DMOS [15], [16]. This enables the minimization of the power losses occurring in the n-type MOSFET added in series with a small resistance. In addition, the low-voltage CMOS provides much lower current sensing error ranges due to its superior and proven matching characteristics over the high-voltage DMOS. Moreover, greater power loss reduction and cost saving can be expected because it does not need an additional external

Fig. 5. Proposed automotive power switch module structure.

diode or a p-type MOSFET, which would be otherwise necessary for reverse battery protection.

### A. Switch On/Off and Reverse Battery Mechanisms

The gate driver of the proposed circuit is a modified self-boost charge pump structure [17]. This driver block is used to operate the power MOSFET and the internal low-voltage CMOS, simultaneously. At the state of  $V_{IN}$  = LOW (switch-off mode), the driver circuit is configured to keep the power MOSFET and internal low-voltage n-type MOSFET in the turn-off state by maintaining  $V_{GS} = 0$  V. In general, the voltage for automotive batteries  $(V_{BAT})$  ranges between 12 V and 13.5 V; however, more than 50 V could be generated during the peak load dump transients. In the turn-off state, most of this voltage is applied to the power MOSFET in Fig. 5. Therefore, the power MOSFETs having a high breakdown voltage are should be selected. However, the body diode in the internal CMOS is intrinsically forward-biased inside the internal CMOS and does not apply voltage in excess of the forward voltage drop  $V_D$  (= 0.7 V). For this reason, even a low-voltage CMOS with a low breakdown voltage can be used without incurring device failure. If this structure is applied, the magnitude of the voltage that is applied in the turn-off state is as follows:

$$V_{GSPowerMOSFET} = 0 \text{ V} \tag{1}$$

$$V_{DS PowerMO SFFT} = V_{RAT} - V_{D} \quad (\approx 0.7 \text{ V})$$

(2)

$$V_{DS,CMOS} = V_D \quad (\approx 0.7 \text{ V}) \tag{3}$$

At the state of  $V_{IN}$  = HIGH (switch-on mode), the driver circuit is configured to keep the state of  $V_{GS}$  = 9.5 V while operating so that the power MOSFET and internal low-voltage n-type MOSFET can be kept in the turn-on state. The magnitude of voltage applied to the output terminal is as follows:

$$V_{GSPowerMOSEET} = 9.5 \text{ V} \tag{4}$$

$$V_{DS,PowerMOSFET} = I_L \times R_{DS(ON) PowerMOSFET}$$

(5)

$$V_{DS,CMOS} = I_L \times R_{DS(ON) CMOS} \tag{6}$$

Fig. 6. Reverse battery condition.

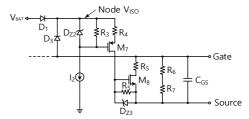

Fig. 7. Drive circuit.

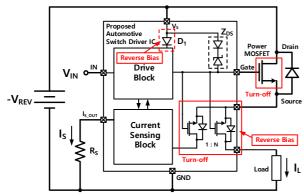

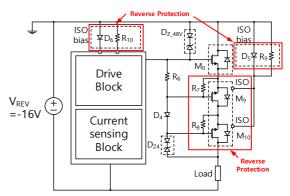

In the reverse battery mode shown in Fig. 6, the drive block operates such that the power MOSFET and internal low-voltage n-type MOSFET are maintained in the turn-off state. During this time, the backward current is completely blocked by the internal CMOS body diode and the diode  $D_1$  that operates backward in the reverse battery mode. Since the reverse battery voltage is applied to both sides of the internal low-voltage n-type MOSFET, it needs to be designed to have higher breakdown voltage than the standard reverse battery voltage for automotive modules. The proposed circuit was designed to have a breakdown voltage of -17.5 V.

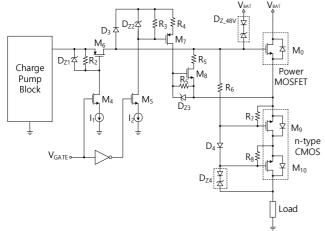

#### B. Driver Block of Circuit Design

Fig. 7 shows the driver block circuit used in the proposed circuit. The charge pump block of the driver block was designed to have the structure shown in Fig. 13, which enables simultaneous operation of the output power MOSFET and the internal low-voltage n-type MOSFET. This driver block is designed to facilitate quick turn-off and prevent device failure through output clamping when in an inductive-load operation mode. It also performs the actions required to maintain the power MOSFET and internal low-voltage n-type MOSFET in the turn-off state during reverse battery operation.

Negative voltage application and reverse battery operation in the p-sub-based BCD process turn various parasitic devices on,

Fig. 8. ON state of drive circuit.

Fig. 9. Turn-off state of drive circuit.

triggering device failure or unstable circuit operation. It is therefore of vital importance to identify the parasitic devices operating in such conditions and control them. Some devices in Fig. 7 operate such that voltages higher than the power supply voltage are applied in the turn-on state and voltages lower than the ground voltage are applied in the turn-off state. Since these conditions are favorable for the operation of various parasitic devices, these devices were taken into consideration while designing the proposed circuit. Such design details are explained according to the following operation conditions of the power MOSFET and internal low-voltage n-type MOSFET.

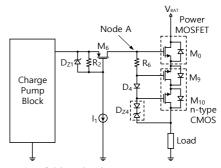

1) Turn-on State Operation: In Fig. 7, the condition of  $V_{GATE}$  =HIGH induces the following states— $M_4$ : turn-on,  $M_5$ : turn-off,  $M_6$ : turn-on,  $M_7$ : turn-off, and  $M_8$ : turn-off—resulting in the operation shown in Fig. 8. Then, the charge pump block supplies a voltage of  $V_{BAT} + 9.5$  V to Node A via  $M_6$ , which is connected to the gates of the power MOSFET and the low-voltage n-type MOSFET ( $M_9$  and  $M_{10}$ ), and maintains the turn-on state. Zener Diodes  $D_{Z1}$  and  $D_{Z4}$  are used to protect the breakdown gate voltages of  $M_6$ ,  $M_9$ , and  $M_{10}$ .

2) Turn-off State Operation: In Fig. 7, the condition of  $V_{GATE}$  = LOW induces the following states— $M_4$ : turn-off,  $M_5$ : turn-on,  $M_6$ : turn-off,  $M_7$ : turn-on, and  $M_8$ : turn-on—resulting in the operation shown in Fig. 9. Fig. 9 now displays the power MOSFET and the low-voltage n-type MOSFET, but the gate and source terminal only.  $V_{ISO}$ , which is equal to or higher than  $V_{BAT}$ , is used as the reference power supply, and the states of  $M_7$ : turn-on and  $M_8$ : turn-on are maintained in the turn-off mode. Now,  $M_8$ ,  $R_5$ ,  $R_6$ , and  $R_7$  discharge the electric charges charged up at  $C_{GS}$  and turn the power MOSFET off.

$$V_{ISO} = V_{BAT} - V_{DI} \quad (V_{GATE} \le V_{BAT} - V_{DI})$$

(7)

$$V_{ISO} = V_{GATE} - V_{D3} \quad (V_{GATE} \ge V_{BAT} - V_{DI})$$

(8)

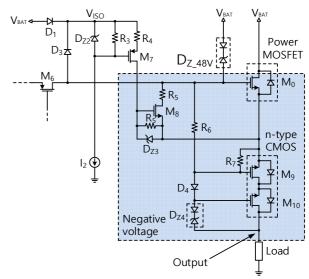

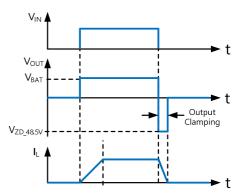

3) Inductive Load Operation: In the drive circuit shown in Fig. 5, the output voltage falls below the ground level during the turn-off operation due to the property of continuous current in the inductor. When this occurs, the Zener clamping circuit limits the voltage across the device to prevent device failure from excessive negative voltage.

Fig. 10 represents the condition in which the electric charge at  $C_{GS}$  discharges via  $M_8$ ,  $R_5$ ,  $R_6$ , and  $R_7$ . The output voltage drops, while maintaining the output current, as the discharging stops at the state of  $V_{GS}$  corresponding to the output current. If the output voltage drops to the state of  $V_{Output} = V_{BAT} - 48.5 \text{ V}$ , the Zener diode is turned on and it protects internal devices by initiating clamping action. Fig. 11 is the input-dependent output graph based on the input during the inductive load operation for fast turn-off. The time-dependent inductor current gradient depending on  $V_{BAT}$  is expressed by the following equations.

$$I_L = \frac{V_{BAT} \times t}{L}$$

(ON, build up) (9)

$$I_L = \frac{(V_{BAT} - 48.5 \text{V}) \times t}{L} \quad \text{(OFF, clamping)} \quad (10)$$

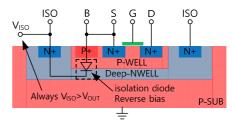

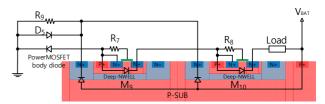

The circuits within the blue square in Fig. 10 showing inductive load operation are operating under a negative voltage  $(V_{BAT} - 48.5 \text{ V})$ . This voltage condition causes device failure without proper isolation. It is therefore essential that all devices within the blue square in Fig. 10 have breakdown voltages exceeding this negative voltage; it is also important that they should be isolated from one another. Therefore, junction isolation is implemented in the proposed design. In this method, isolation is ensured using the reverse-bias properties of the PN junction. In the p-sub-based process, it is important to set the voltage bias of the n-well, the device site, at the highest potential to keep the PN junction in reverse bias. Fig. 12 shows the isolated n-type CMOS structure used in the proposed design. Here, if the ISO terminal is connected to the highest potential, devices connected to the p-sub are isolated from one another even if negative voltages are applied to the internal devices. In the proposed block,  $V_{ISO}$  is connected to ISO pin, which has a voltage equal to  $V_{BAT}$  or the highest voltage as defined by Eqs. (7) and (8).

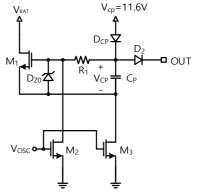

4) Charge Pump Operation: Fig. 13 shows the internal structure of the charge pump block used in the driver block. It has the structure of a self-boost charge pump modified to match the design of the proposed driver block [17]. The state of  $V_{OSC}$  = HIGH in Fig. 13 triggers the state of  $M_1$  to turn-off,  $M_2$  to turn-on, and  $M_3$  to turn-on, and the  $V_{CP} - V_{Dcp}$  voltages are charged at  $C_P$  from  $V_{CP}$  via  $D_{CP}$ , as shown in Fig. 14(a). The state of  $V_{OSC}$  = LOW triggers the state of  $M_1$  to turn-on,  $M_2$  to turn-off, and  $M_3$  to turn-off, thus charging the  $C_{GS}$  of the power MOSFET and the low-voltage n-type MOSFET connected to the OUT terminal by turning on  $M_1$  with the voltage charged to

Fig. 10. Inductive load output clamping.

Fig. 11. Inductive load output clamping graph.

Fig. 12. Junction isolation bias.

Fig. 13. Self-boost charge pump circuit.

Fig. 14. (a) Charge mode, (b) boost mode.

C<sub>P</sub>, as illustrated in Fig. 14(b). The values of the output voltages can be calculated from Eq. (11).

$$V_{OUT} = V_{BAT} + V_{CP} - V_{Dcp} - V_{D2}$$

(11)

5) Reverse Battery Protection Operation: the proposed driver IC has the function of completely blocking the reverse current in the reverse battery mode without using any external device. Since the protection of the reverse battery for automotive semiconductors is designed based on the reference value of -16 V, the breakdown voltage requirement was met by connecting two low-voltage CMOSs in series.

In the case of a p-sub-based IC in reverse battery mode, as shown in Fig. 6, the p-sub node is at a voltage of  $V_{BAT}$  and the n-well bias for isolation drops to the ground level. In this condition, the diodes are forward-biased and devices fail due to over-current unless there is an additional circuit to prevent this from happening in the reverse battery mode. Moreover, without an appropriate n-well bias, the internal device installed for reverse battery protection cannot operate properly. Fig. 15 shows a circuit providing bias to ensure normal operation of devices even in the reverse battery mode. In normal operation, a circuit composed of D<sub>5</sub>, D<sub>6</sub>, R<sub>10</sub>, and R<sub>9</sub> is used to keep the PN junction reverse-biased with the ISO potential biased at the highest voltage. Fig. 16 depicts the operations of  $M_9$  and  $M_{10}$  in reverse battery mode using a vertical structure. Separate operation of each device within the ISO (n-well) in reverse battery mode was ensured using ISO (n-well) and p-sub diodes. M<sub>9</sub> and M<sub>10</sub> are induced to operate exclusively with backward diodes by maintaining  $V_{GS} = 0$  V using  $R_7$  and  $R_8$ , whereby the body diodes of M<sub>9</sub> and M<sub>10</sub> operate to block the backward current.

# C. Current Sensing Block Circuit Design

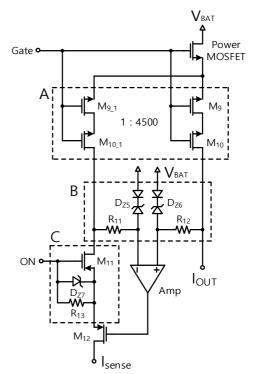

Fig. 17 presents the current sensing circuit structure used in this study. In this structure, the current  $I_{SENSE}$  is output by equalizing the  $V_{DS}$  voltages of the low-voltage n-type SenseFETs  $M_{9\_1}$  and  $M_{10\_1}$  and the output terminals  $M_9$  and  $M_{10}$ , using a feedback amplifier and  $M_{12}$ . The output current is configured to have a ratio of 1:4500. While driving an inductive load, the driver block protects the devices through Zener clamping operation, whereby a negative voltage is applied to the amplifier input terminal connected to Part A and the source terminal of  $M_{12}$  in Fig. 17. In this process, the absence of a separate protection circuit results in the failure of the current

Fig. 15. ISO (n-well) bias circuit for reverse battery protection.

Fig. 16. ISO (n-well) bias structure for reverse battery protection.

Fig. 17. Current sense circuit.

sensing block. Therefore, protection circuits such as B and C in Fig. 17 are applied in the proposed design to protect the amplifier and  $M_{12}$ . Part B protects the amplifier input terminal, and  $D_{Z5}$  and  $D_{Z6}$  operate based on  $V_{BAT}$  whenever the input voltage drops so that all voltages generated by Zener clamping are applied to  $R_{11}$  and  $R_{12}$ . Part C protects  $M_{12}$  and the current sensing block circuit by maintaining the state of  $M_{11}$  at turn-off during Zener clamping operation, whereby all negative

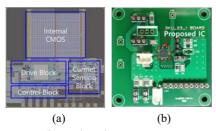

Fig. 18. (a) Layout, (b) test board.

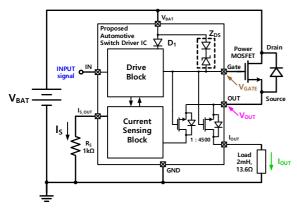

Fig. 19. Inductive load test circuit.

voltages generated by Zener clamping are applied to the  $M_{11}$  drain terminal. Therefore, the device for  $M_{11}$  requires breakdown voltages exceeding the voltage generated during Zener clamping operation. In the proposed circuit, a p-type DMOS with a breakdown voltage of 60 V provided via the above-mentioned process was used.

# IV. MEASUREMENT RESULTS

Fig. 18 presents the layout and test board of the proposed IC. The areas of the die and the internal SenseFET are 2500  $\times$  2500  $\mu m^2$  and 1200  $\times$  1060  $\mu m^2$ , respectively. The IC was packaged using a 32-pin 4  $\times$  4 quad-flat no-leads (QFN) package. The properties of the proposed IC were tested and validated through an inductive load operation test, reverse battery protection test, and current sensing test.

## A. Inductive Load Operation Test Results

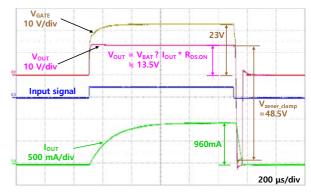

Fig. 19 shows the inductive load test circuit. IRF3710ZpbF was used for the power MOSFET and the test circuit was constructed using a 2-mH 13.6- $\Omega$  load [18]. Fig. 20 shows the output waveforms resulting from inductive load operation when  $V_{BAT} = 13.5$  V. The turn-on/off operation, charge pump operation voltage, and Zener clamping operation of the drive block were confirmed by testing using a 1-ms-wide input. Table I outlines the operation test measurement results.

# B. Reverse Battery Protection Test Results

Fig. 21 shows a reverse battery test circuit with negative battery connection using the same device and load conditions.

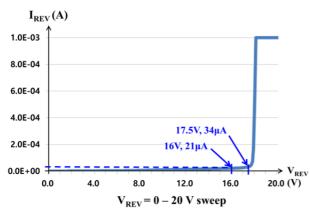

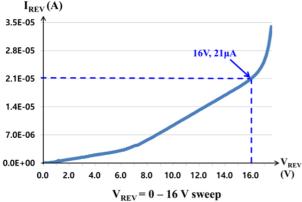

Fig. 22 shows the graphs presenting the results of the reverse

Fig. 20. Inductive load test results.

TABLE I

INDUCTIVE LOAD DRIVE TEST RESULTS

| Parameter           | Values            | Test condition                    |

|---------------------|-------------------|-----------------------------------|

| Turn-on delay       | 25 μs             | Turn-on time to 90% of $V_{OUT}$  |

| Turn-off delay      | 15 μs             | Turn-off time to 10% of $V_{OUT}$ |

| Charge pump output  | $V_{BAT}$ + 9.5 V | Turn-on condition                 |

| Zener clamp voltage | 48.5 V            | Freewheeling<br>Condition         |

Fig. 21. Reverse battery test circuit.

current measurements taken while varying the voltage  $V_{REV}$  in the range of 0 V to 20 V. A reverse current of 22  $\mu$ A was confirmed at  $V_{REV}$  = 16 V, the reference voltage for automotive reverse battery protection. This verified that the reverse current was blocked in the reverse battery mode with load and IC. The maximum breakdown voltage was 17.5 V.

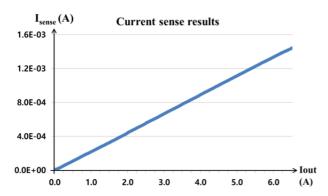

## C. Current Sensing Test Results

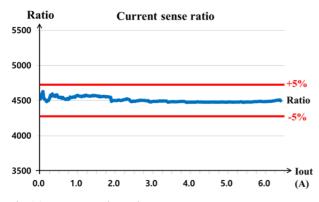

Fig. 19 shows the current sensing test circuit. A Keithley 4200A-SCS semiconductor parameter analyzer was used to measure the output current  $I_{SENSE}$ , thereby increasing  $I_{OUT}$  by a 25-mA step. Table II outlines the main measurement values. In the test, the  $I_{OUT}$ -dependent  $I_{SENSE}$  values were found to increase linearly up to 6.5 A, as shown in Fig. 23. Fig. 24 depicts the current sensing ratio ( $I_{OUT}$  /  $I_{SENSE}$ ). The error range for the

Fig. 22. Reverse battery test results.

Fig. 23. Current sensing test results.

Fig. 24. Current sensing ratio.

TABLE II

CURRENT SENSING TEST RESULTS

| I <sub>OUT</sub> (A) | $I_{SENSE}$ ( $\mu$ A) | Sense ratio( $I_{SENSE}/I_{OUT}$ ) |

|----------------------|------------------------|------------------------------------|

| 0.1                  | 22.12                  | 4521                               |

| 0.5                  | 109.68                 | 4559                               |

| 1                    | 219.68                 | 4552                               |

| 2                    | 445.69                 | 4487                               |

| 4                    | 894.18                 | 4473                               |

| 6.5                  | 1445.11                | 4498                               |

TABLE III CHARACTERISTICS OF PROPOSED DRIVER IC

| Parameter                    | Values              |

|------------------------------|---------------------|

| Operating range              | 8–28 V              |

| Turn-on delay                | 25 μs               |

| Turn-off delay               | 15 μs               |

| Internal CMOS $R_{DS(ON)}$   | $34~\text{m}\Omega$ |

| Maximum load current         | 6.5 A               |

| Current sense ratio          | 4500                |

| Current sense ratio accuracy | ±5%                 |

| Clamping voltage             | 48.5 V              |

| Reverse battery Protection   | -16 V               |

measurement results is  $\pm 5\%$ .

The performance of the proposed IC is outlined in Table III, and the factors showing improvement or difference from the conventional results are compared in Table IV.

The reference papers and products in Table IV are all related to the power MOSFET switch for automotive applications. References [3]-[5] supports current sensing but does not have a reverse battery protection. While, references [9], [11] have a built-in reverse battery protection function but does not have current sensing function. In contrast, the proposed IC in this paper supports an improved current sensing function with a reverse battery protection.

The cases presented in [3]-[5] have smaller  $R_{DS(ON)}$  compared to the proposed IC; however, if a device for reverse battery protection is added in these cases, additional  $R_{DS(ON)}$  will occur, resulting in levels similar to that of the proposed IC. Moreover, they are characterized by large current sensing errors due to the irregular current sensing circuits using DMOS-structured SenseFETs.

In the case presented in [9], although the reverse battery protection function is embedded, its level (-15 V) does not meet the standard for automotive module reverse battery protection.

Reference [11] presents a structure that uses two power DMOS arrays for reverse battery protection. This model was found to generate reverse currents that were larger than that in

TABLE IV

COMPARISON OF CHARACTERISTICS

| Parameter                             | This<br>work | [3]  | [4]  | [5]  | [9] | [11]       |  |

|---------------------------------------|--------------|------|------|------|-----|------------|--|

| $R_{DS(ON)}(\mathrm{m}\Omega)$        | 14<br>+ 34   | 30   | 15   | 16   | _   | 170        |  |

| Minimum<br>sensing<br>current<br>(mA) | 100          | 500  | 500  | 500  | No  | No         |  |

| Current sense ratio                   | 4500         | 2150 | 3500 | 3500 | No  | No         |  |

| Sense ratio accuracy (%)              | ±5           | ±20  | ±15  | ±20  | No  | No         |  |

| Fast turn-off function                | Yes          | Yes  | Yes  | Yes  | No  | No         |  |

| Reverse<br>protection<br>for load (V) | -16          | No   | No   | No   | -15 | -71        |  |

| Reverse<br>current<br>under -16V      | -21<br>μA    | No   | No   | No   | _   | -750<br>μA |  |

the circuit proposed in this study because of the leakage currents intrinsic to the DMOS structure. Moreover, current sensing circuits constructed according to this model will most likely incur large deviations.

All other ICs compared in Table IV were fabricated through n-sub-based processes, but the proposed IC is different from them in that it was designed using a p-sub-based process which is most popular one in worldwide foundry.

#### V. CONCLUSIONS

This paper has described a high-side switch driver IC capable of current sensing accuracy improvement and reverse battery protection. When applied to automotive power semiconductor switches, the proposed structure could not only improve the accuracy of the protection and diagnostic circuits, it could also eliminate some of the external additional protection devices currently being used for reverse battery protection. In additions, it is cost-effective because the power MOSFET could use a low-cost general-purpose MOSFET instead of the expensive SenseFET.

The IC used in this study has been fabricated through a p-sub-based 90-V 0.13-µm BCD process and its characteristics have been tested and verified. It operates without any parasitic phenomena, in spite of being designed using widely distributed p-sub-based BCD processes instead of using special n-sub processes by each manufacturer in order to reduce the influences of parasitic devices under negative voltages.

The current sensing accuracy has been found to have improved, with error rates of  $\pm 5\%$  or lower in the output

current range of 0.1 A - 6.5 A and a reverse current of -21  $\mu$ A has been confirmed at a reverse battery voltage of -16 V. From these results, it has been confirm that the current sensing error improvement and reverse battery protection could be integrated into a single IC using p-sub-based processes.

#### ACKNOWLEDGMENT

The present research was conducted by the research fund of Dankook University in 2014.

#### REFERENCES

- [1] B. Lequesne, "Automotive electrification: The nonhybrid story," *IEEE Trans, Transport, Electrific*, Vol. 1, No. 1, pp. 40-53, Jun. 2015.

- [2] A. Patel and M. Ferdowsi, "Current sensing for automotive electronics – A survey," *IEEE Trans. Veh. Technol.*, Vol. 58, No. 8, pp. 4108-4119, Oct. 2009.

- [3] Infineon, "BTS5030-1EJA" Datasheet.

- [4] International Rectifier, "IR3311" Datasheet.

- [5] STMicroelectronics, "VN7016AJ-E" Datasheet.

- [6] V. Choudhary and M. Jacob, "Smart diode and 4-switch buck-boost provide ultra high efficiency, compact solution for 12-V automotive battery rail," Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2016, PCIM Europe 2016, International Exhibition and Conference for, pp.2019-2026, 2016.

- [7] F. Scrimizzi, G. Longo, and G. Gambino "Automotive-grade P-channel power MOSFETs for Static, dynamic and repetitive reverse polarity protection," Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2016, PCIM Europe 2016, International Exhibition and Conference for, 10-12, pp.1987-1991, 2016

- [8] E. Biagi, L. Fanucci, L. D. Piro, M. Schipani, R. Serventi, P. D'Abramo, "Universal output stage with reverse polarity protection for automotive applications," *Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM,* 2014 International Symposium on, pp. 929-934, 2014.

- [9] N. Costantino, R. Serventi, F. Tinfena, P. D'Abramo, P. Chassard, P. Tisserand, S. Saponara, and L. Fanucci, "Design and test of an HV-CMOS intelligent power switch with integrated protection and self-diagnostic for harsh automotive applications," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 7, pp. 2715-2727, Jul. 2011.

- [10] K. Sakamoto, Y. Nunogawa, K. Satonaka, T. Kouda, and S. Horiuchi, "An intelligent power IC with reverse battery protection for fast-switching high side solenoid drive," *IEEE Trans. Electron Devices*, Vol. 46, No. 8, pp. 1775-1781, Nov. 1999.

- [11] K. Sakamoto, Y. Nunogawa, K. Satonaka, and S. Horiuchi, "A three-terminal intelligent power MOSFET with built-in reverse battery protection for automotive applications," *IEEE Trans. Electron Devices*, Vol. 46, No. 11, pp. 2228-2234, Nov. 1999.

- [12] Infineon, "Profet + Current Sense" Smart High Side Switches Rev1.1, Application Note.

- [13] NXP Semiconductors, "Current Sensing Power MOSFETs" AN10322, Application Note.

- [14] Y. Xiao, J. Cao, J.D. Chen, and K. Spring, "Current sensing trench power MOSFET for automotive applications," Applied Power Electronics Conference and Exposition,

- 2005, APEC 2005. Twentieth Annual IEEE, pp. 766-770, 2005.

- [15] I.-Y. Park, Y.-K. Choi, K.-Y. Ko, S.-C. Shim, B.-K. Jun, N.-C. Moon, N.-J. Kim, and K.-D. Yoo, "BCD (Bipolar-CMOS-DMOS) technology trends for power management IC," *Power Electronics and ECCE Asia (ICPE & ECCE)*, 2011 IEEE 8th International Conference on, pp. 318-325, 2011.

- [16] I.-Y. Park, Y.-K. Choi, K.-Y. Ko, C.-J. Yoon, B.-K. Jun, M.-Y. Kim, H.-C. Lim, N.-J. Kim, and K.-D. Yoo, "BD180: A New 0.18 µm BCD (Bipolar-CMOS-DMOS) Technology from 7 V to 60 V," Power Semiconductor Devices and IC's, 2008, ISPSD '08, 20th International Symposium on, pp. 64-67, 2008.

- [17] S. Park and T. M. Jahns, "A self-boost charge pump topology for a gate drive high-side power supply," *IEEE Trans. Power Electron.*, Vol. 20, No. 2, pp. 300-307, Mar. 2005.

- [18] International Rectifier, "IRF3710ZPbF" Datasheet.

- [19] V. Macary, T. Sicard, and R. Petrutiu, "A novel LDMOS structure with high negative voltage capability for reverse battery protection in automotive IC's," *Bipolar/BiCMOS Circuits and Technology Meeting*, pp. 90-93, 2001.

- [20] Infineon, "Improved SENSE Calibration and Benefits Guide" V1.0, Application Note.

Jaehyun Park was born in Korea. He received his B.S., M.S. degree in Electrical and Electronics Engineering from Dankook University, Yongin, Korea, in 2012, 2014 respectively. From 2014, he is currently pursuing the Ph.D. degree at Dankook University. His main research interests are power ICs and devices for automotive

applications, power converter circuits, active gate drive topology, and integrated power electronics modules (IPEMs).

Shihong Park was born in Korea. He received the B.S. degree in electrical engineering from Yonsei University, Seoul, Korea, in 1988, and the M.S. and Ph.D. degrees from the University of Wisconsin, Madison, in 2003 and 2004, respectively. From 1988 to 1998, he was with Samsung Electronics, Buchen, Korea, as a Senior

Power IC Design Engineer. In 2004, he was a Principal Research Engineer with Fairchild Semiconductor Korea, Buchen, Korea. In March 2005, he joined the School of Electrical and Electronics Engineering, Dankook University, Yongin. His main research interests are power ICs and devices for automotive applications, LED driver circuits, power converter circuits, active gate drive topology, and integrated power electronics modules (IPEMs).