## JPE 17-6-1

1391

# A Secondary Resonance Soft Switching Half Bridge DC-DC Converter with an Inductive Output Filter

Zhang-yong Chen<sup>†</sup> and Yong Chen<sup>\*</sup>

<sup>†</sup>School of Energy Science and Engineering, University of Electronic Science and Technology of China, Chengdu, China <sup>\*</sup>Institute for Electric Vehicle Driving System and Safety Technology, University of Electronic Science and Technology of China, Chengdu, China

#### Abstract

In this paper, a secondary resonance half-bridge dc-dc converter with an inductive output filter is presented. The primary side of such a converter utilizes asymmetric pulse width modulation (APWM) to achieve zero-voltage switching (ZVS) of the switches, and clamps the voltage of the switch to the input voltage. In addition, zero current switching (ZCS) of the output diode is achieved by a half-wave rectifier circuit with a filter inductor and a resonant branch in the secondary side of the proposed converter. Thus, the switching losses and diode reverse-recovery losses are eliminated, and the performance of the converter can be improved. Furthermore, an inductive output filter exists in the converter reduce the output current ripple. The operational principle, performance analysis and design equation of this converter are given in this paper. The analysis results show that the output diode voltage stress is independent of the duty cycle, and that the voltage gain is almost linear, similar to that of the isolation Buck-type converter. Finally, a  $200V \sim 380V$  input, 24V/2A output experimental prototype is built to verify the theoretical analysis.

Key words: Asymmetrical duty cycle, Half bridge converter, Secondary resonance, Soft-switching technique

#### I. INTRODUCTION

Half bridge converters have received a lot of attention in mangy application [1]-[9], such as LED lighting, renewable energy applications, distributed generation applications, battery charge application. This is due in large part to the benefits of zero-voltage switching (ZVS) for all of the switches without the help of any auxiliary circuits and no conduction loss penalty. However, the asymmetrical duty cycle technique applied to half bridge DC-DC converters has several demerits. In [10], Paul Imbertson and Ned Mohan analyzed the fundamental principle of the asymmetric half-bridge (AHB) converter and gave design equations for the converter topology. They also explained that some of the phenomenon of the traditional asymmetric half-bridge (AHB) converter suffer from nonlinear voltage gain characteristics, narrow ZVS switching for the switches, and asymmetric voltage stress for the output diodes when duty cycle is variable.

Thus, improved circuit topologies [11]-[25] should be presented to prefer the application of such a technique. In order to improve and optimize the AHB converter, the voltage gain of this converter has given consideration to the leakage inductor of the transformer and the dead time for the switches [11]-[15]. However, this design equation is very complex and difficult to utilize. By introducing a resonant technique [16]-[18] to the primary of the transformer, ZVS switching for all of the switches are extended. However, variable switching frequency modulation [18] is used, which increases the complexity of the magnetic component or the input filter. In addition, due to the nonlinear voltage gain of the AHB converter, the duty cycle range of this converter is limited and duty cycle is effective in the range of 0~0.5. By using the two transformers of the traditional AHB converter [19], such a technique allows duty cycle to become larger than 50%. Hence, it has the merits of a lower output rectifier stress and a wider input voltage range.

In order to further improve the performance of the AHB converter, the voltage spike and oscillation of the output diode rectifier should be suppressed. The active clamp technique [20]

Manuscript received Feb. 20, 2017; accepted Jul. 3, 2017

Recommended for publication by Associate Editor Chun-An Cheng.

Corresponding Author: zhang\_yong\_ch@126.com

Tel: +86-028-66360106, Univ. Electronic Sci. & Tech. China (UESTC) <sup>\*</sup>Institute for Electric Vehicle Driving System and Safety Technology, University of Electronic Science and Technology of China, China

can be used on the secondary-side of the transformer, and the voltage stress of the output diode can be clamped. However, an auxiliary switch and capacitor should be added and this increases the cost and control complexity. Zero current turned-off for the diode can be achieved by utilizing the secondary-side resonance technique [21]-[24], and output inductor is eliminated. Thus, the current ripple of the output capacitor is increased. In [25], a multi-phase interleaving technique is used to reduce the output capacitor. However, a complex load sharing control strategy should be adopted.

In this paper, the secondary resonance soft technique half bridge DC-DC converter with an inductive output filter is presented, as shown in Fig. 1. The asymmetrical pulse width modulated (APWM) strategy is adopted and ZVS switching for all of the switches is achieved. By adding a resonant inductor and resonant capacitor on the secondary-side of the transformer, ZCS for the output diode is obtained. Therefore, the switching losses and diode reverse-recovery losses are eliminated. Furthermore, theoretical analysis results show that the linear voltage transfer gain vs. the duty cycle for the proposed converter is obtained and duty cycle range is extended. In addition, when compared with the traditional AHB converter, the voltage stress for the output diode has no relation to the duty cycle or the nearly perform constant voltage stress.

The circuit configuration and operation principle of the proposed converter are presented in Section II. Steady-state analysis results are given in Section III. A performance analysis of the proposed converter is developed in Section IV. The performance of the proposed converter is verified by experimental results obtained with a  $200V \sim 380V$  input, 24V/2A output experimental prototype in Section V. Some conclusions are given in Section VI.

#### II. PROPOSED SECONDARY RESONANCE HALF BRIDGE DC/DC CONVERTER

#### A. Circuit Configuration

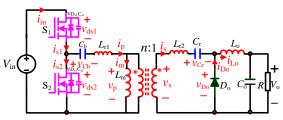

Fig. 1 shows the circuit configuration of the proposed converter. As shown in Fig. 1, the proposed converter is composed of a half bridge configuration with a blocking capacitor  $C_b$  on the primary side, a resonant circuit network consisting of a leakage inductor  $L_{lk}$  or an external inductor  $L_r$ and a resonant capacitor  $C_r$  on the secondary side, a diode  $D_o$ is the rectifier diode, and an inductive filter with an inductor  $L_o$ and a capacitor  $C_o$  is connected to the lode side. In this circuit configuration, the switches  $S_1$  and  $S_2$  are pulsed by a complementary duty cycle with a dead time to obtain zero voltage switching for the switches  $S_1$  and  $S_2$ . A resonance network composed of  $L_r$  and  $C_r$  on the secondary side is utilized to achieve zero current switching for the diode  $D_o$ . In addition, an inductive filter is used to reduce the output current ripple of the proposed converter. As a result, the size or volume

Fig. 1. Proposed secondary resonance half bridge converter.

of the capacitor  $C_{\rm o}$  is reduced.

In order to simplify the analysis of the proposed converter, the following assumptions are made:

- 1) The power switches  $S_1$  and  $S_2$  are ideal except for their anti-paralleled diodes and output capacitances; the output capacitances of the switches  $S_1$  and  $S_2$  are equal, *i.e.*  $C_{oss} = C_{s1} = C_{s2}$ ; and the switches  $S_1$  and  $S_2$  are pulsed by a complementary duty cycle with a dead time.

- 2) The capacitance of the capacitors  $C_{\rm b}$  and  $C_{\rm o}$  are so large that the voltages  $V_{\rm cb}$  and  $V_{\rm o}$  can be considered as constants in a switching cycle.

- 3) The transformer is modeled as an equivalent circuit composed of a magnetizing inductor  $L_{\rm m}$ , a leakage inductor  $L_{\rm lk}$  and an ideal transformer with a turns ratio of *n*:1, with  $L_{\rm m} >> n^2 L_{\rm lk}$ . The converter operates in the steady state.

#### **B.** Operation Principle

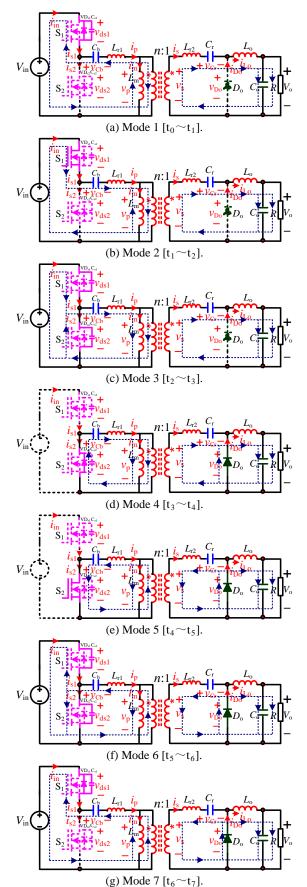

In a switching cycle, the proposed converter has seven operational modes, with their corresponding equivalent circuits in each operation mode, as shown in Fig. 2. In addition, key waveforms of the proposed converter are shown in Fig. 3.

*Mode* 1 [ $t_0 \sim t_1$ ]: At  $t=t_0$ , when  $i_P(t)$  is negative, the anti-paralleled diodes of the switch  $S_1$  are conducted to provide a flowing path for  $i_P(t)$ , and zero voltage turn-on is achieved for the switch S1. The current  $i_s(t)$  on the transformer secondary side is equal to the output current  $i_{Lo}(t)$ , and the diode  $D_o$  is turned-off. In this mode, the magnetizing inductor current  $i_m(t)$  increases linearly from negative with a current slope of  $(V_{in} - V_{cb})/L_m$ . Thus, the current  $i_m(t)$  can be expressed as:

$$i_{\rm m}(t) = i_{\rm m}(t_0) + \frac{V_{\rm in} - V_{\rm cb}}{L_{\rm m}}(t - t_0)$$

(1)

Then, the current  $i_p(t)$  is the sum of the magnetizing inductor current  $i_m(t)$  and the secondary-side current  $i_s(t)$ reflected to the primary-side of the transformer. It can be obtained as

$$i_{\rm p}(t) = i_{\rm m}(t) + \frac{i_s(t)}{n} \tag{2}$$

In addition, according to the Kirchhoff's voltage laws (KVL), the circuit equations of the secondary side of the transformer can be obtained as:

$$(L_{r2} + L_o)\frac{di_s(t)}{dt} = \frac{V_{in} - V_{cb}}{n} - v_{cr}(t) - V_o$$

(3)

$$i_{\rm s}(t) = C_{\rm r} \frac{\mathrm{d}v_{\rm cr}(t)}{\mathrm{d}t} \tag{4}$$

Then, it is possible to obtain the following:

$$i_{s}(t) = i_{s}(t_{0})\cos[\omega_{o}(t-t_{0})] + \frac{[(V_{in} - V_{cb}) / n - V_{o}] - v_{cr}(t_{0})}{Z_{o}} \sin[\omega_{o}(t-t_{0})]$$

(5)

$$v_{\rm cr}(t) = [(V_{\rm in} - V_{\rm cb}) / n - V_{\rm o}] + Z_{\rm o}i_{\rm s}(t_0)\sin[\omega_{\rm o}(t - t_0)] - [(V_{\rm in} - V_{\rm cb}) / n - V_{\rm o} - v_{\rm cr}(t_0)]\cos[\omega_{\rm o}(t - t_0)]$$

(6)

Where,  $\omega_0 = 1/\sqrt{(L_{r2}+L_0)C_r}$ ,  $Z_0 = \sqrt{(L_{r2}+L_0)/C_r}$ . The switching frequency  $f_s(f_s = \omega_s/2\pi)$  is much larger than the frequency  $f_0(f_0 = \omega_0/2\pi)$ , which is composed of the output inductor  $L_0$  and the resonant capacitor  $C_r$ . Thus,  $\omega_0(t-t_0) = \omega_s(t-t_0)\cdot f_0/f_s \approx 0$ . Then  $\cos[\omega_0(t-t_0)] \approx 1$  and  $\sin[\omega_0(t-t_0)] \approx \omega_0(t-t_0)$ . Thus, equation (5) and (6) can be simplified as:

$$i_{s}(t) = i_{Lo}(t) = i_{s}(t_{0}) + \frac{\left[\left(V_{in} - V_{cb}\right) / n - V_{o}\right] - v_{cr}(t_{0})}{L_{o}}(t - t_{0})$$

(7)

$$v_{\rm cr}(t) = v_{\rm cr}(t_0) + \frac{\dot{t}_{\rm s}(t_0)}{C_{\rm r}}(t - t_0)$$

(8)

*Mode* 2  $[t_1 \sim t_2]$ : At  $t=t_1$ , the primary-side current  $i_p(t)$  linearly increase to zero, and the switch  $S_1$  is conducted. As shown in mode 1, zero voltage turn-on of the switch  $S_1$  is guaranteed because the anti-paralleled diode of  $S_1$  is conducted. In this mode, the current  $i_m(t)$  continues to increase and the output diode  $D_o$  continues to be bias-reversed. In this mode, all of the circuit equations are the same as those in operation mode 1.

*Mode* 3 [ $t_2 \sim t_3$ ]: At  $t=t_2$ , the switches  $S_1$  is turned off and  $i_P(t)$  charges the output capacitor of the switch  $S_1$  and discharges the output capacitor of the switch  $S_2$ . Because the output capacitors of the switches  $S_1$  and  $S_2$  are very small, the charging time and discharging time are very short. In this mode, the primary-side current  $i_P(t)$  is recognized as being kept constant.

*Mode* 4  $[t_3 \sim t_4]$ : At  $t=t_3$ , the voltage of the output capacitor for the switch  $S_1$  is charged to the input voltage. Then, the voltage of switch  $S_2$  is discharge to zero, and the anti-paralleled diodes of  $S_2$  is forward-biased and turned-on to provide the following path for the primary-side current  $i_p(t)$ . Then, the voltage across the primary-side of the transformer is clamped to  $-V_{cb}$ , the magnetizing inductor current  $i_m(t)$  decreases linearly from positive with a current slope of  $(-V_{cb})/L_m$ . In addition, at the secondary-side of the transformer, the output diode  $D_o$  is conducted due to the forward-bias of the diodes on the condition of the positive reflected secondary-side voltage  $V_{cb}/n$ . Then, the current through the output inductor is decreased with a current slope of  $(-V_o)/L_o$ ,  $i_{Lo}(t)$ , which can be expressed as:

$$\dot{i}_{\rm Lo}(t) = \dot{i}_{\rm Lo}(t_3) - \frac{V_{\rm o}}{L_{\rm o}}(t - t_3) \tag{9}$$

At the secondary-side, the circuit equation can be obtained as:

$$L_{\rm f2} \frac{{\rm d}i_{\rm s}(t)}{{\rm d}t} = \frac{-V_{\rm cb}}{n} - v_{\rm cr}(t) \tag{10}$$

$$\dot{i}_{\rm s}(t) = C_{\rm r} \frac{\mathrm{d}v_{\rm cr}(t)}{\mathrm{d}t} \tag{11}$$

Then, it is possible to obtain:

$$i_{s}(t) = i_{s}(t_{3})\cos[\omega_{r}(t-t_{3})] + \frac{-V_{cb}/n - v_{cr}(t_{3})}{Z_{r}}\sin[\omega_{r}(t-t_{3})]$$

(12)

$$v_{\rm cr}(t) = -V_{\rm cb} / n + Z_{\rm r} i_{\rm s}(t_3) \sin[\omega_{\rm r}(t-t_3)] - [-V_{\rm cb} / n - v_{\rm cr}(t_3)] \cos[\omega_{\rm r}(t-t_3)]$$

(13)

Where,  $\omega_r = 1/\sqrt{L_{r2}C_r}$  and  $Z_r = \sqrt{L_{r2}/C_r}$ . According to equation (12), the transformer secondary-side current  $i_s(t)$  varies with a sinusoidal-shape. Therefore, there exist two cases. In the first case, the current  $i_s(t)$  can be returned to zero and zero current turned-off for the diode  $D_o$  is achieved when the switch S1 is turned-off, and then the output inductor current  $i_{Lo}(t)$  is equal to the current  $i_s(t)$ . In the second case, when the switch  $S_1$  is turned-off, the current  $i_s(t)$  cannot return to zero, and then the output inductor current  $i_s(t)$ . In order to obtain ZCS for the diode, the first case is analyzed in the following.

*Mode* 5  $[t_4 \sim t_5]$ : At  $t=t_4$ , the primary-side current  $i_p(t)$  decrease to zero from the positive to the negative, and then the switch  $S_2$  is turned-on. The zero voltage turned-on for the switch  $S_2$  is achieved due to the conduction of the anti-parallel diode of S2 in mode 4. After the switch  $S_2$  is turned-on, the current im(t) continues to decrease, and the output diode  $D_o$  conducts. In addition, the current  $i_{Lo}(t)$  through the output inductor continues to decreased with a current slope of  $(-V_o)/L_o$ , and the equation is the same as equation (9).

*Mode* 6 [ $t_5 \sim t_6$ ]: At  $t=t_4$ , the resonant current  $i_s(t)$  is equal to the output inductor current  $i_{Lo}(t)$  and zero current turned-off for the diode  $D_o$  is achieved. The circuit equation is similar to that of mode 1. Then:

$$i_{\rm s}(t) = i_{\rm Lo}(t) = i_{\rm s}(t_5) + \frac{(-V_{\rm cb} / n - V_{\rm o}) - v_{\rm cr}(t_5)}{L_{\rm o}}(t - t_5)$$

(14)

$$v_{\rm cr}(t) = v_{\rm cr}(t_5) + \frac{i_{\rm s}(t_5)}{C_{\rm r}}(t - t_5)$$

(15)

*Mode* 7 [ $t_6 \sim t_7$ ]: At  $t=t_6$ , the switch  $S_2$  is turned off and  $i_P(t)$  charges the output capacitor of the switch  $S_2$ , and discharges the output capacitor of the switch  $S_1$ . When the output capacitors of the power switch  $S_2$  is charged to the input voltage  $V_{in}$ , the anti-paralleled diode of the switch  $S_1$  is conducted and the next switching cycle begins.

Fig. 2. Operational modes of the proposed converter.

Fig. 3. Key waveforms of the proposed converter.

### **III. STEADY STATE ANALYSIS**

#### A. Voltage Transfer Gain

Assume the dead times in mode 3 and mode 7 are so short that they can be neglected. From the previous analysis, the voltage across the transformer primary side is  $V_{in}-V_{cb}$ , and in mode 4, mode 5 and mode 6, the voltage across the transformer primary side is  $-V_{cb}$ , where  $V_{cb}$  is the average voltage across the blocking capacitor  $C_b$ .

In the steady state, by applying the volt-second balance to the magnetizing inductor  $L_m$ , the average voltage across the clamp capacitor is given as:

$$(V_{\rm in} - V_{\rm cb})DT_{\rm s} - V_{\rm cb}(1 - D)T_{\rm s} = 0$$

(16)

And then:

$$V_{\rm cb} = DV_{\rm in} \tag{17}$$

Due to the volt-second balance of the inductors  $L_{\rm o}$ ,  $L_{\rm m}$  and  $L_{\rm r}$ , the average voltage across the resonant capacitor is equal to the output voltage, i.e.  $V_{\rm cr} = -V_{\rm o}$ . Then, the voltage across the output diode can be obtained as:

$$v_{\text{Do}}(t) = \begin{cases} \frac{V_{\text{in}} - V_{\text{cb}}}{n} - v_{\text{cr}}(t) - L_{\text{r2}} \frac{di_{\text{s}}(t)}{dt}, & t \in [t_0, t_3] \\ 0, & t \in [t_3, t_5] \\ \frac{-V_{\text{cb}}}{n} - v_{\text{cr}}(t) - L_{\text{r2}} \frac{di_{\text{s}}(t)}{dt}, & t \in [t_5, t_7] \end{cases}$$

(18)

Where:

$$L_{r2} \frac{di_{s}(t)}{dt} = L_{r2} \frac{\left[ (V_{in} - V_{cb}) / n - V_{o} \right] - v_{cr}(t_{0})}{L_{o}} = K_{1}, \ t \in [t_{0}, t_{3}]$$

$$L_{r2} \frac{di_{s}(t)}{dt} = L_{r2} \frac{(-V_{cb} / n - V_{o}) - v_{cr}(t_{5})}{L_{o}} = K_{2}, \ t \in [t_{5}, t_{7}]$$

Because the proposed converter operates in the steady state, in one switching period, the average voltage across the output diode  $D_o$  is equal to  $V_o$  with the volt-second balance of the inductor  $L_o$ . Thus, integral equation (18) and solve these equations, and the output voltage  $V_o$  can be obtained as:

$$V_{\rm o} = \frac{DV_{\rm in}}{n} - \frac{D}{1 - D} K_1 + \frac{-DV_{\rm in}/n - K_2}{1 - D} \frac{\Delta t_{57}}{T_{\rm s}} - \frac{1}{(1 - D)T_{\rm s}} \int_{t_{\rm c}}^{t_{\rm f}} v_{\rm cr}(t) dt$$

(19)

Where,  $\Delta t_{57}=t_7-t_5$ . In reality, in order to achieve ZCS for the diode  $D_o$ , the resonant frequency  $f_r$  must be slightly larger than the switching frequency  $f_s$ . Thus, the time interval  $\Delta t_{57}$  is short. Then, the voltage across the resonant capacitor can be considered as constant, and equation (19) can be simplified as:

$$V_{o} = \frac{DV_{in}}{n} - \frac{D}{1 - D} K_{1} - \frac{K_{2}}{(1 - D)} \frac{\Delta t_{57}}{T_{s}} + \frac{-DV_{in}/n + V_{o} + \Delta v}{1 - D} \frac{\Delta t_{57}}{T_{s}}$$

(20)

In addition, from equation (6), the voltage ripple of the resonant capacitor can be expressed as:

$$\Delta v = \frac{I_{\rm o} - \frac{V_{\rm o}}{2L_{\rm o}} (1 - D)T_{\rm s}}{2C_{\rm r}} DT_{\rm s}$$

(21)

Furthermore, the output inductor  $L_o$  is so large that the current ripple can be neglected. Then the half-sinusoidal wave through the diode  $D_o$  can be considered. Thus  $\Delta t_{57}=(1-D)T_s-T_r/2$ , where  $T_s$  and  $T_r$  are the switching period and the resonant period, respectively. Therefore, the voltage transfer gain of the proposed converter can be expressed as:

$$M = \frac{V_{\rm o}}{V_{\rm in}} = \frac{\frac{D}{n}}{1 - \frac{T_{\rm s}}{L_{\rm o}} \frac{DT_{\rm s}}{2C_{\rm r}D_{\rm r}} (Q - \frac{1 - D}{2})(1 - D - D_{\rm r})}$$

(22)

Where, the quality factor  $Q=L_o/RT_s$  and  $D_r=T_r/(2T_s)$ . The parameter quality K is defined as:

$$K = \frac{T_{\rm s}}{L_{\rm o}} \frac{DT_{\rm s}}{2C_{\rm r}D_{\rm r}} (Q - \frac{1 - D}{2})(1 - D - D_{\rm r})$$

(23)

Thus, equation (22) can be simplified as:

$$M = \frac{V_{\rm o}}{V_{\rm in}} = \frac{D/n}{1-K}$$

(24)

When the resonant duty cycle  $D_r$  is fixed, the curves are plotted as the parameter quality *K* versus the duty cycle *D* and the quality factor *Q*, as shown in Fig. 4(a). From Fig. 4(a), when the duty cycle *D* is smaller than 0.835, the amplitude of the parameter quality *K* is in the range of [-0.3, 0.3] with a variable duty cycle *D* and a quality factor *Q*. When *D* is larger than 0.835, the parameter quality *K* varies sharply.

When the quality factor Q is fixed, the curves are plotted

Fig. 4. Curves of the parameter quality *K*: (a) the parameter quality *K* versus *D* and *Q* with a constant  $D_r$ ; (b) the parameter quality *K* versus *D* and  $D_r$  with a constant *Q*.

as the parameter quality *K* versus the duty cycle *D* and the quality factor  $D_r$ , as shown in Fig. 4(b). From Fig. 4(b), the parameter quality *K* increases when  $D_r$  decreases and *D* increases. However, the parameter quality *K* behaves as a parabolic-wave property. When *D* gets larger, the parameter quality *K* is decreased.

From equation (24), the curves of the voltage transfer gain of the proposed converter are shown in Fig. 5. Fig. 5(a) plot the curves of the voltage transfer ratio M versus D and Q with a constant  $D_{\rm r}$ , when the resonant duty cycle  $D_{\rm r}$  is fixed. As can be seen from Fig. 5(a), the proposed converter nearly has the same linear voltage transfer gain characteristics as the buck-type converter when  $D_r$  is constant. When the load get lighter, the linearity of the characteristic is better. When the quality factor is fixed, the curves of the voltage transfer ratio M versus the duty cycle D and  $D_r$  is shown in Fig. 5(b). As can be seen from Fig. 5(a), in order to obtain the linearity voltage gain of the proposed converter, the resonant duty cycle  $D_r$  should be large but should not exceed the duty cycle with ZCS for the output diode, and the parameter of Q should be kept smaller at the maximum power to keep the linearity of voltage transfer gain.

Fig. 5. Curves of the voltage transfer ratio M: (a) the voltage transfer ratio M versus D and Q with a constant  $D_r$ ; (b) the voltage transfer ratio M versus D and  $D_r$  with a constant Q.

#### IV. PERFORMANCE ANALYSIS

#### A. ZCS Condition for the Output Diode

From the above operational mode analysis, the ZCS condition for the output diode  $D_o$  is achieved when the resonant current  $i_s(t)$  is equal to the output inductor current  $i_{Lo}(t)$  before the switch  $S_2$  is turned-off. The sinusoidal-wave for the output diode is considered due to the current ripple of the output inductor being neglected with a large inductance value. Thus, the ZCS condition for the output diode can be obtained as:

$$\frac{1}{2f_{\rm r}} < (1-D)T_{\rm s}$$

(25)

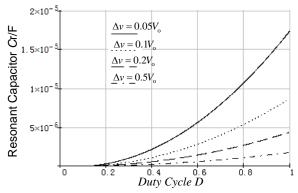

Based on the expression of equation (21), the resonant capacitor  $C_r$  can be obtained as:

$$C_{\rm r} = \frac{I_{\rm o} - \frac{V_{\rm o}}{2L_{\rm o}} (1 - D)T_{\rm s}}{2\Delta v} DT_{\rm s}$$

(26)

Fig. 6 shows the curves resonant capacitor value versus the duty cycle *D* with a quality factor of Q=0.5,  $f_s=50$ kHz and  $L_o=100\mu$ H. As can be seen from Fig.6, when the voltage ripple is below 20 percent of the output voltage, the capacitor

Fig. 6. Curves of the resonant capacitor selection.

value can be selected below  $5\mu F$  in the entire duty cycle range. Thus, ceramic or film capacitors with a small equivalent series resistance can be selected.

When the resonant capacitor is obtained according to equation (26), the resonant inductor can be achieved from equation (25) as:

$$L_{\rm r2} < \frac{(1-D)^2 T_{\rm s}^2}{\pi^2 C_{\rm r}}$$

(27)

#### B. ZVS Condition for the Primary-Side Power Switches

Based on operation principle of the proposed converter in the section II, in order to achieve zero-voltage turned-on for the power switches, the output capacitor voltage of the switches  $S_1$  and  $S_2$  should be charged or discharged to zero in the dead time. In addition, the key waveforms of the proposed converter, as shown in Fig. 3, indicate that the current through the primary-side of the transformer is positive at the time  $t_2$ , and ZVS for the switch  $S_2$  can be achieved. Furthermore, the current through the primary-side of the transformer is negative at the time  $t_6$ , and ZVS for the switch  $S_1$  can be achieved. Thus, ZVS condition for the switches  $S_1$ and  $S_2$  can be expressed as:

$$-I_{\rm m}(t_6) + I_{\rm Lo,min} < 0$$

(28)

$$I_{\rm m}(t_2) + I_{\rm Lo,max} > 0$$

(29)

Where,  $I_{\rm m}(t_2)$  and  $-I_{\rm m}(t_6)$  are the maximum and minimum of the magnetizing inductor current  $i_{\rm m}$ . Because there exists a blocking capacitor in the primary-side of the transformer, no bias current get through the magnetizing inductor. Thus,  $I_{\rm m}(t_2) = I_{\rm m}(t_6) = V_{\rm in} * D(1 - D)T_s/(2L_{\rm m})$ . In the proposed converter, the average of the output inductor current  $i_{\rm Lo}$  is equal to the output current  $I_o$  ( $I_{\rm Lo}=I_o$ ). Thus,  $I_{\rm Lo,max}$  and  $I_{\rm Lo,min}$ can be expressed as  $I_{\rm Lo,max} = (1 + \Delta I/I_o * 100\%)I_o$  and  $I_{\rm Lo,max} = (1 - \Delta I/I_o * 100\%)I_o$ . Therefore, the ZVS condition for the switches S<sub>1</sub> and S<sub>2</sub> can be obtained as:

$$-\frac{V_{\rm in}D(1-D)T_{\rm s}}{2L_{\rm m}} + (1 - \frac{\Delta I}{I_{\rm o}} \cdot 100\%) \cdot I_{\rm o} < 0$$

(30)

$$\frac{V_{\rm in}D(1-D)T_{\rm s}}{2L_{\rm m}} + (1 + \frac{\Delta I}{I_{\rm o}} \cdot 100\%) \cdot I_{\rm o} > 0$$

(31)

Based on equations (30) and (31), the ZVS for the switch  $S_2$  can be achieved during the entire load range. In addition, in order to achieve ZVS turned-on for the switch  $S_1$ , the magnetizing inductor can be satisfied by the following inequality equation:

$$L_{\rm m} < \frac{V_{\rm in} D (1 - D) T_{\rm s}}{2 (1 - \Delta I / I_{\rm o} \cdot 100\%) \cdot I_{\rm o}}$$

(32)

Thus, equation (32) is satisfied when the rated power is given and the output current  $I_0$  is decided. At this moment, the maximum magnetizing inductor can be selected to achieve ZVS for the primary-side power switches  $S_1$  and  $S_2$ .

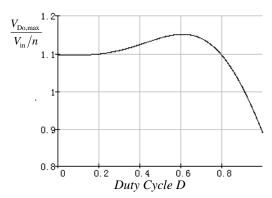

#### C. Voltage Stress for the Power Switches and Diode

Based on the above analysis, it can be easily seen that the voltage stress of the power switches  $S_1$  and  $S_2$  is clamped to the input voltage. It can be seen from equation (18), that the voltage stress for the output diode  $D_0$  can be obtained as:

$$V_{\rm do,max} = \frac{V_{\rm in} - V_{\rm cb}}{n} + V_{\rm o} + \Delta v$$

=  $\frac{V_{\rm in}}{n} [(1 - D) + \frac{D}{1 - K}] + \Delta v$  (33)

When the input voltage is selected as the base voltage, the voltage stress for the output diode can be expressed as:

$$\frac{V_{\rm do,max}}{V_{\rm in} / n} = (1 - D) + (1 + \frac{\Delta v}{V_{\rm o}} \cdot 100\%) \cdot nM \qquad (34)$$

where, *M* is voltage transfer gain of the proposed converter and  $\Delta v/V_o$  is the ripple coefficient of the output voltage.

Fig. 7 describes the curves of the voltage stress of the output diode  $D_0$  versus the duty cycle D with  $\Delta v=20\% V_0$ . It can be seen from Fig.7 that the voltage stress for the output diode  $D_0$  is always below  $1.15V_{in}/n$  in the entire duty cycle range. In addition, the voltage stress of the output diode  $D_0$ varies slowly vs. the duty cycle. The reason can be explicated that in order to get a constant output voltage when the input voltage decreases, the voltage transfer gain is at its maximum, but the duty cycle D is large. Inversely, when the input voltage increases, voltage transfer gain is at its minimum, but the duty cycle D is small. Therefore, the duty cycle D seldom has an influence on the voltage stress of the output diode. Comparing the traditional asymmetric half bridge converter with the forward-type rectifier, the voltage stress for the output diodes are  $V_{in}/(nD)$  and  $V_{in}/(n(1-D))$ , respectively. It can be obtained that in the traditional AHB converter topology, the voltage stresses for the output diode varies with the duty cycle. Therefore, the proposed converter has preferred performance with a nearly constant voltage stress for the output diode.

#### V. EXPERIMENTAL RESULTS

Experimental studies of the proposed converter have been performed to verify the above analysis results with the

Fig. 7. Curves of the diode voltage stress selection.

Fig. 8. Photograph of an experiment prototype for the proposed converter.

TABLE I PARAMETERS OF THE PROPOSED CONVERTER

| Main switches( $S_1 \sim S_2$ ) | SPW11N60C3                                                                                                                                           |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| $diodes(D_0)$                   | STTH2002C                                                                                                                                            |

| Main Transformer                | Core: ETD34 PC40<br>Trun Ratio: 26 : 5<br><i>Manetizing inductance L<sub>m</sub></i> : 410µH<br>Secondary resonant inductor L <sub>r2</sub> : 1.65µH |

| Output inductor                 |                                                                                                                                                      |

| Blocking Capacitor $(C_b)$      | 1µF/600V                                                                                                                                             |

| Output Capacitor ( $C_{o}$ )    | 200µF/100V                                                                                                                                           |

| Resonant Capacitor ( $C_r$ )    | 2.2µF                                                                                                                                                |

converter parameters as: 1) input voltage  $V_{in}=200V \sim 380V$ ; 2) output voltage  $V_o=24V$ ; 3) maximum output power  $P_o=50W$ ; 4) switching frequency  $f_s=50$ kHz, output inductor  $L_o=100\mu$ H, and output capacitor  $C_o=200\mu$ F.

Based on the above analysis, in order to achieve ZCS for the diode  $D_o$ , the resonant frequency should be larger than the switching frequency. In addition, when  $f_r$  become very large, the conduction losses of the power switch and diode for the proposed converter are dominant and decrease the performance of the converter. Thus, for a trade-off between the conduction losses and ZCS condition of diode, a resonant duty cycle  $D_r$  equal to 0.3 is selected to guarantee the ZCS of the output diode on the condition of the rated output power

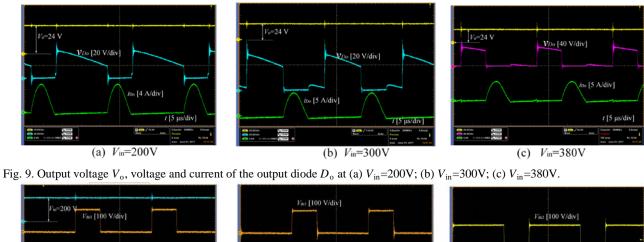

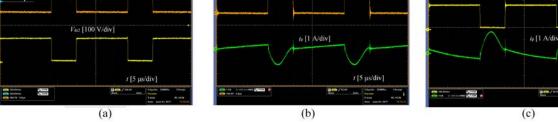

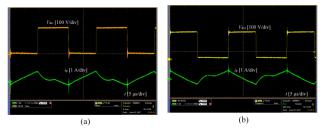

Fig. 10. Voltage and current of the switches  $S_1$  and  $S_2$  at an input voltage of  $V_{in}=200V$  (D=0.65) at a 100% load.

Fig. 11. Voltage and current of the switches  $S_1$  and  $S_2$  at an input voltage of  $V_{in}$ =300V (D=0.45) at a 100% load.

Fig. 12. Voltage and current of the switches  $S_1$  and  $S_2$  at an input voltage of  $V_{in}$ =380V (D=0.32) at a 100% load.

and the minimum input voltage. According to Fig. 6, the capacitance value of the resonant capacitor can be obtained on the condition of  $\Delta v=20\% V_o$ . Thus,  $C_r=2.2\mu$ F was selected. When  $C_r$  is fixed, according to equation (27), the resonant inductor can be selected. A TDK ETD34 core is used for the design of the transformer. The primary and secondary turns of the transformer are  $n_p=26$ T and  $n_s=5$ T. The magnetizing inductance  $L_m=410\mu$ H is designed to achieve ZVS turned-on for the switches S<sub>1</sub> and S<sub>2</sub> according to equation (32). The

secondary resonant inductor is  $L_{r2}=1.65\mu$ H. Then the resonant frequency  $f_r = 1/2\pi\sqrt{L_rC_r} = 83$ kHz. In addition, the quality factor is Q=0.417 at a full load. The parameters of the passive components and semiconductors are shown in Fig. 8 with the circuit parameters given in Table I.

t [5 us/div

#### A. Experimental Results

Fig. 8 shows a photograph of an experiment prototype for the proposed converter. The key waveforms of the proposed

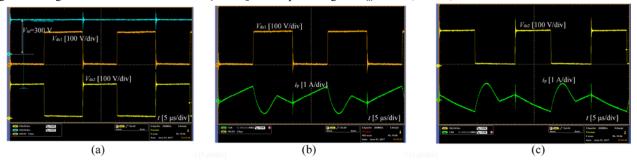

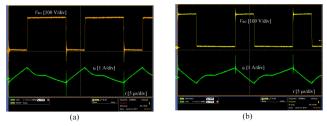

Fig. 13.  $V_{in}$ =200V and a 20% load: (a) waveforms for the switch S<sub>1</sub>; (b) waveforms for the switch S<sub>2</sub>.

Fig. 14.  $V_{in}$ =300V and a 20% load: (a) waveforms for the switch S<sub>1</sub>; (b) waveforms for the switch S<sub>2</sub>.

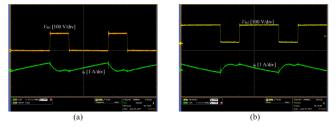

converter at the input voltage, *i.e.*, 200V, 300V, 380V, at a full load are given in Fig. 9-Fig. 12. Fig. 9 shows experimental waveforms of the output voltage, and the voltage and current waveforms of the output diode. It can be seen from Fig. 9 that before the diode is turned-off, the current through the output diode is decreased to zero. Therefore, ZCS for the diode is achieved under a wide input voltage through appropriate design of the resonant tank. Moreover, it can be seen that the voltage stress of the output diode varies in a narrow range under different input voltages.

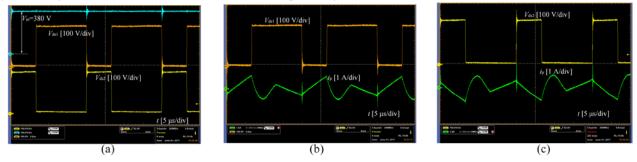

Fig. 10-Fig. 12 show voltage and current waveforms for the switches  $S_1$  and  $S_2$  at different input voltages. It can be seen from Fig. 10-Fig. 12 that the anti-parallel diode for the switches  $S_1$  and  $S_2$  are conducted before the switches are turned-on. Thus, ZVS for the switches  $S_1$  and  $S_2$  can be achieved through appropriate design of the magnetizing inductor. Fig. 13-Fig. 15 show waveforms of the switches  $S_1$ and  $S_2$  at a 20% load under different input voltages. In addition, at light load, ZVS for the switches  $S_1$  and  $S_2$  can be obtained to eliminate the switching losses and to improve the efficiency of the proposed converter.

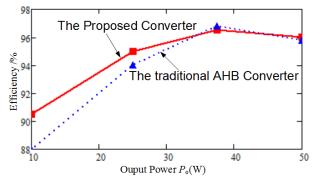

#### B. Efficiency

Fig. 16 shows the efficiency at an input voltage of 200 V. It can be seen from Fig. 10 that the proposed converter has a peak efficiency of 96.5%. At a light-load, the efficiency decreases because the switching-related losses of this converter are dominant. In addition, it can be seen from Fig. 16 that at a full load, the efficiency of the proposed converter is slightly smaller than that of the traditional AHB converter. This is due to the fact that in order to obtain ZCS for the output diode and ZVS for the switch, the magnetizing inductor in the proposed converter is smaller than that in the traditional AHB converter.

Fig. 15.  $V_{in}$ =380V and a 20% load: (a) waveforms for the switch S<sub>1</sub>; (b) waveforms for the switch S<sub>2</sub>.

Fig. 16. Efficiency curves.

losses are dominant, but the reverse recovery loss for the output diode is eliminated in the proposed converter.

Thus, the conduction loss and reverse recovery loss should be a trade-off. However, at a light load, the efficiency of the proposed converter is much higher than that in the traditional AHB converter. ZCS for the output diode and ZVS for the switch in the proposed converter are maintained in the entire load range. However, ZVS for the switch is lost in the traditional AHB converter.

#### VI. CONCLUSIONS

This paper presented a secondary resonance half-bridge DC-DC converter with an inductive output filter. The operational principle, performance analysis and design equations of the proposed converter are given. Analysis results show that the output diode voltage stress is independent of the duty cycle, and that it achieves preferred performance with a nearly constant voltage stress for the output diode. In addition, the voltage gain is almost linear, which is similar to that of the isolation Buck-type converter. Experimental results of a prototype converter verify the theoretical analysis results. They show that ZVS switching for the switches and ZCS switching for the output diode are achieved in the entire load range. Based on these merits, the proposed converter is available for application, especially in the high-voltage applications such as high-voltage battery chargers (200-400 V), LED lighting, etc.

#### ACKNOWLEDGMENT

This work was supported by the National Natural Science Foundation of China under grant no.51607027, the Fundamental Research Funds for the Central Universities under project number ZYGX2016KYQD123, and the Scientific and Technical Supporting Programs of Sichuan Province under Grant (2016GZ0395, 2017GZ0391 and 2017GZ 0392).

#### REFERENCES

- E. Mujjalinvimut, P. N. N. Ayudhya, and A. Sangswang, "An improved asymmetrical half-bridge converter with self-driven synchronous rectifier for dimmable LED lighting," *IEEE Trans. Ind. Electron.*, Vol. 63, No. 2, pp. 913-925, Feb. 2016.

- [2] M. Arias, D. G. Lamar, F. F. Linera, D. Balocco, A. A. Diallo, and J. Sebastian, "Design of a soft-switching asymmetrical half-bridge converter as second stage of an LED driver for street lighting application," *IEEE Trans. Power Electron.*, Vol. 27, No. 3, pp. 1608-1621, Mar. 2012.

- [3] J.-P. Lee, B.-D. Min, T.-J. Kim, D.-W. Yoo, and J.-Y. Yoo, "Design and control of novel topology for photovoltaic DC/DC converter with high efficiency under wide load ranges," *Journal of Power Electronics*, Vol. 9, No. 2, pp. 300-307, Mar. 2009.

- [4] M. Arias, M. F. Diaz, D. G. Lamar, D. Balocco, A. A. Diallo, and J. Sebastian, "High-efficiency asymmetrical half-bridge converter without electrolytic capacitor for low-output-voltage AC–DC LED drivers," *IEEE Trans. Power Electron.*, Vol. 28, No. 5, pp. 2539-2550, May 2013.

- [5] M. Arias, M. F. Diaz, J. E. R. Cadierno, D. G. Lamar, and J. Sebastian, "Digital implementation of the feedforward loop of the asymmetrical half-bridge converter for LED lighting applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 3, No. 3, pp. 642-653, Sep. 2015.

- [6] H. Wu, K. Sun, L. Zhu, and Y. Xing, "An interleaved half-bridge three-port converter with enhanced power transfer capability using three-leg rectifier for renewable energy applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 4, No. 2, pp. 606-616, Jun. 2016.

- [7] S. Abe, J. Yamamoto, and T. Ninomiya, "Hybrid controlled soft-switching half-bridge converter in DCM operation with voltage doubler rectifier for battery charge application," in *IEEE International Telecommunications Energy* Conference (INTELEC), Oct. 2015.

- [8] H. Moradisizkoohi, J. Milimonfared, M. Taheri, and S. Salehi, "Duty-cycle-controlled resonant dual-half-bridge converter with multifunctional capacitors for distributed generation applications," *IET Power Electronics*, Vol. 9, No. 9, pp. 1873-1884, Jul. 2016.

- [9] J.-P. Lee, B.-D. Min, T.-J. Kim, D.-W. Yoo, and J.-Y. Yoo, "Input-series-output-parallel connected DC/DC converter for a photovoltaic pcs with high efficiency under a wide load range," *Journal of Power Electronics*, Vol. 10, No. 1, pp. 9-13, Jan. 2010.

- [10] P. Imbertson and N. Mohan, "Asymmetrical duty cycle permits zero switching loss in PWM circuits with no conduction loss penalty," *IEEE Trans. Ind. Appl.*, Vol. 29,

No. 1, pp. 121-125, Jan./Feb. 1993.

- [11] S. Korotkov, V. Meleshin, R. Miftahutdinov, and S. Fraidlin, "Soft-switched asymmetrical half-bridge DC/DC converter steady-state analysis: an analysis of switching processes," in *Proceedings of the TELESCON*, pp. 177-184, 1997.

- [12] R. Oruganti, P. C. Heng, J. T. K. Guan, and L. A. Choy, "Soft-switched DC/DC converter with PWM control," *IEEE Trans. Power Electron.*, Vol. 13, No. 1, pp. 102-114, Jan. 1998.

- [13] S. Chakraborty and S. Chattopadhyay, "An improved asymmetric half-bridge converter with zero DC offset of magnetizing current," in *IEEE Applied Power Electronics Conference and Exposition (APEC)*, pp. 1-8, Mar. 2015.

- [14] R. Miftakhutdinov, A. Nemchinov, V. Meleshin, and S. Fraidlin, "Modified asymmetrical ZVS half-bridge DC-DC converter," in *Fourteenth Annual Applied Power Electronics Conference and Exposition (APEC)*, pp. 567-574, Mar. 1999.

- [15] W. Chen, P. Xu, and F. C. Lee, "The optimization of asymmetrical half bridge converter," in *Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (APEC)*, pp. 703-707, Mar. 2001.

- [16] P. K. Jain, A. St-Martin, and G. Edwards. "Asymmetrical pulse-width-modulated resonant DC/DC converter topologies," *IEEE Trans. Power Electron.*, Vol. 11, No. 3, pp. 413-422 May 1996.

- [17] D. J. Tschirhart and P. K. Jain, "A CLL resonant asymmetrical pulsewidth-modulated converter with improved efficiency," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 1, pp. 114-122, Jan. 2008.

- [18] J.-B. Lee, J.-K. Kim, J.-I. Baek, J.-H. Kim, and G.-W. Moon, "Resonant capacitor on/off control of half-bridge LLC converter for high-efficiency server power supply," *IEEE Trans. Ind. Electron.*, Vol. 63, No. 9, pp. 5410-5415, Sep. 2016.

- [19] M. Arias, M. F. Diaz, D. G. Lamar, F. M. F. Linera, and J. Sebastian, "Small-signal and large-signal analysis of the two-transformer asymmetrical half-bridge converter operating in continuous conduction mode," *IEEE Trans. Power Electron.*, Vol. 29, No. 7, pp. 3547-3562, Jul. 2014.

- [20] B. R. Lin and J. Y. Dong, "Analysis and implementation of an active clamping zero-voltage turn-on switching/ zero-current turn-off switching converter," *IET Power Electronics*, Vol. 3, No. 3, pp. 429-437, May 2010.

- [21] K.-B. Park, C.-E. Kim, G.-W. Moon, and M.-J. Youn, "A new high efficiency PWM single-switch isolated converter," *Journal of Power Electronics*, Vol. 7, No. 4, pp. 301-309, Oct. 2007.

- [22] B.-R. Lin, J.-J. Chen, and J.-Y. Jhong, "Analysis and Implementation of a dual resonant converter," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 7, pp. 2952- 2961, Jul. 2011.

- [23] J.-J. Lee, J.-M. Kwon, E.-H. Kim, and B.-H. Kwon, "Dual series-resonant active-clamp converter," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 2, pp. 699-710, Feb. 2008.

- [24] Z. Chen, Q. Zhou, J. Xu, and X. Zhou, "Asymmetrical pulse-width-modulated full-bridge secondary dual resonance DC-DC converter," *Journal of Power Electronics*, Vol. 14, No. 6, pp. 1224-1232, Nov. 2014.

- [25] T. Jin and K. Smedley. "Multiphase LLC series resonant converter for microprocessor voltage regulation," in 41<sup>st</sup> IAS Annual Meeting. Conference Record of the 2006 IEEE Industry Applications Conference, pp. 2136–2143, Oct. 2006.

Zhang-yong Chen was born in Sichuan, China, in 1988. He received his B.S. degree in Electrical Engineering and its Automation, and his Ph.D. degree in Electrical Engineering from Southwest Jiaotong University (SWJTU), Chengdu, China, in 2010 and 2015, respectively. From September 2014 to September 2015, he was

a Visiting Student in the Future Energy Electronics Center (FEEC), Virginia Tech, Blacksburg, VA, USA. Since January 2016, he was been a Lecturer in the School of Energy Science and Engineering, University of Electronic Science and Technology of China (UESTC), Chengdu, China. His current research interests include switching-mode power supplies, soft switching techniques, power factor correction converters and renewable energy sources.

Yong Chen (SM'16, M'08) was born in Sichuan Province, China, in 1977. Since 2015, he has been a Professor and a Ph.D. Supervisor in the School of Energy Science and Engineering, and the Director of the Institute for Electric Vehicle Driving System and Safety Technology, University of Electronic Science and Technology of China

(UESTC), Chengdu, China. He was a Visiting Scholar in School of Mechanical Engineering, University of Adelaide, Adelaide, SA, Australia. He is presently presiding over a National Natural Science Foundation of China project and over Scientific and Technical Supporting Programs in Sichuan Province. He has published over 50 technical papers in journals and conference proceedings. In addition he has 15 Chinese patents. His current research interests include power electronics, motor control, energy control and network control. He is a Senior Member of the IEEE, and a Member of the Chinese Society for Electrical Engineering (CSEE).