JPE 9-5-15

# A Novel Soft-Switching Full-Bridge PWM Converter with an Energy Recovery Circuit

Dong-Young Lee\*, Bo-Hyung Cho\*\*, and Joung-Hu Park†

\*International Rectifier, El Segundo, California, USA

\*\*Dept. of Electrical Eng. and Comp. Sci., Seoul National University, Seoul, Korea

†Dept. of Electrical Eng., Soongsil University, Seoul, Korea

#### **ABSTRACT**

This paper proposes a new phase-shift full-bridge DC-DC converter by applying energy recovery circuits to a conventional full-bridge DC-DC converter in plasma display panel applications. The converter can achieve soft-switching in main-switches by an extra auxiliary resonant network even with the wide operating condition of both output load and input voltage. The un-coupled design guidelines to the main bridge-leg component parameters for soft-switching operation contribute to conduction loss reduction in the transformer primary side leading to efficiency improvement. The auxiliary switches in the resonant network also operate in zero-current switching. This paper analyzes the operation modes of the proposed scheme and presents the key design guidelines through steady state analysis. Also, the paper verifies the validity of the circuits by hardware experiments with a 1kW DC/DC converter prototype.

Keywords: Energy Recovery Circuit, Full-Bridge, DC-DC, Zero Voltage Switching, Regenerative Transformer

### 1. Introduction

Generally, switching devices utilized for power converters or inverters have parasitic capacitances between each terminal such as a collector and an emitter or a drain and a source. In high-power MOSFETs and IGBTs, widely used for applications demanding high-speed switching with excellent transition characteristics, the capacitances are especially large.

IGBTs also have a tail current phenomena which drastically increases turn-off loss. An external parallel capacitive snubber generally used for relieving the problem also enhances the un-desired capacitance. This large capacitance causes severe dissipation switching loss and strong EMI noise at turn on time with hard switching operation.

To overcome this problem, various kinds of soft-switching technique have been proposed for the switching converters/inverters in high frequency driving<sup>[1-16]</sup>. Among the soft-switching schemes, a phase-shift PWM full-bridge DC-DC converter is one of the most widely-prevailing topology for medium to high power applications<sup>[10]</sup>. The full-bridge topology has a very simple configuration and it is easy to implement the

Manuscript received Feb. 5, 2009; revised Aug. 10, 2009

<sup>&</sup>lt;sup>†</sup>Corresponding Author: whoishe@snu.ac.kr

Tel: +82-2-828-7269, Fax: +82-2-817-7961, Soongsil Univ.

<sup>\*</sup>International Rectifier, El Segundo, California, USA.

<sup>\*\*</sup>Dept. of Electrical Eng. and Comp. Sci., Seoul Nat'l Univ., Korea

soft-switching by controlling the MOSFET-driving pulse sequence. The converter enhances the power efficiency through the zero voltage switching operation of the switching devices and enables it to drive in very high frequency switching actions. It also makes it easy to design transformers and magnetic filters with a fixed switching frequency. The converter typically utilizes the leakage inductance of the transformer or an extra inductor in series.

However, the soft-switching range is affected by the load current level and the resonant inductance. For a wide range, the inductance should be large, which causes effective duty cycle reduction affecting the load as the load current increases. Duty reduction leads to high transformer ratios, which enhances the diode voltage stress. Duty reduction also limits the converter frequency. Additionally, a large inductor can resonate to the junction capacitance of the secondary rectifier diodes. Furthermore, since magnetic current flowing through the resonant inductor of the phase-shift converter always circulates around the main path for soft-switching in the next period, additional conduction losses on the primary switches, resonant inductor and the transformer take place even during the operational mode in which the resonant power is not transferred to the output load. Moreover, the circulating current increases according to the load current. Therefore, heavy load current and low input voltage applications should consider this circulating loss factor seriously because the resonant conduction loss portion becomes un-negligible to the entire loss.

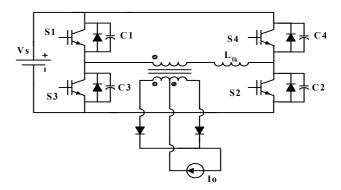

As an alternative soft switching technique, energy recovery circuits (ERC) generally used for PDP applications can be applied. The purpose of an ERC is the charging and discharging of any kind of capacitive load<sup>[17-30]</sup>. Figure 1 shows a comparison between a full-bridge DC/DC converter and an AC PDP display's sustain driver with an ERC. The converter always sees a partially capacitive load due to the main-switch body-capacitances (C1-C4 in Fig. 1(a)). The ERC also sees a capacitive load (Co in Fig. 1(b)) because the PDP has an electrically capacitive characteristic like a MOSFET junction capacitances during the sustain mode. The ERC enhances power efficiency through energy recovery from the capacitive load as well as from the

(a) Conventional phase-shift full-bridge DC/DC converter.

(b) Circuit diagram of PDP sustain driver with energy recovery circuit.

Fig. 1. Comparison between conventional DC-DC converter and AC PDP driving circuit of a capacitive load.

junction capacitances. Likewise, a DC/DC converter can achieve soft-switching by charging and discharging the capacitances using an ERC. When an external auxiliary circuit such as an ERC is utilized, the power stage design for soft switching is possible regardless of the operating condition range. The auxiliary resonant circuits processing a minimal amount of energy for soft switching operation contribute to its size and cost competitiveness as well as its high efficiency.

From the family of ERC topologies, a forward type ERC with an auxiliary regenerative transformer was taken as an example and has been analyzed<sup>[19]</sup>. Design guidelines with a design example are described and verified by experimental results from a 1 kW prototype converter operating at 50 kHz.

## 2. Operating Principle

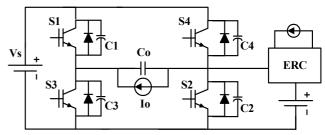

Fig. 2 shows a proposed full-bridge DC/DC converter with an ERC. As shown in the figure, the proposed circuit is a converter with an ERC employing a regenerative

transformer as a ZVS auxiliary circuit [19]. The auxiliary circuit is connected with the lagging-leg switches of the phase-shift converter. Without the auxiliary circuits, the soft-switching voltage is determined by the initial current of the inductor. As shown in (1) and (2), this initial current is determined by the load current, the junction capacitances of the secondary rectifier diodes and the primary resonant inductor. Soft-switching is achieved only when the inductor current energy is greater than the junction capacitor energy. Since the energy is dependent on the load current, the design requirement for soft-switching can be very harsh in applications with extremely light load conditions. In order to avoid dependency on load variations, an auxiliary resonant network is included in the proposed scheme for supplying resonant energy, instead of a resonant inductor in the main circuit itself. With the assistance of external energy sources, soft-switching operation is achieved regardless of the input-voltage/output-load conditions.

Due to the energy-recovery operation of the external auxiliary network, circulating energy can be minimized, which results in a reduction of conduction losses in the primary side. Furthermore, the effective duty ratio can be increased due to the small leakage resonance inductor. The performance of the proposed scheme is superior in applications that have a wide load fluctuation that is 2-3 times greater than average. The detailed operation principles are described in the following sections. A summary of the advantages of the proposed scheme is as follows:

- Wide input voltage and load variation range for the soft-switching condition.

- Conduction loss decreasing especially on the primary side.

- Easy design procedure for the transformer secondary and the diodes due to optimal resonance inductor selection.

$$\begin{split} T_{delay} &= C_{sw} \frac{V_S}{I_{Llk}} \,, \\ L_{lk} \cdot I_{Llk0}^2 &\geq C_{sw} \cdot V_S^2 \\ \text{where } I_{Llk} &= I_{load} / N \,, \end{split} \tag{1}$$

$$I_{Llk0} = I_{Llk} - \Delta I_{Llk}, \quad \Delta I_{Llk} = \frac{V_S}{\sqrt{\frac{L_{lk}}{C_{eq}}}}, \quad (2)$$

$C_{sw}$ : Switch junction capacitance.

$V_S$ : Input voltage.

$L_{lk}$ : Leakage inductance.

N: Turn ratio (secondary).

## 3. Operating Analysis

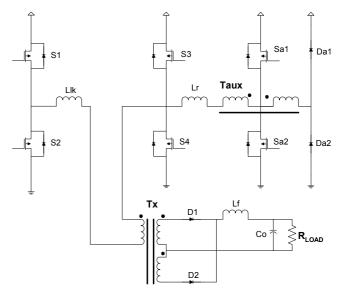

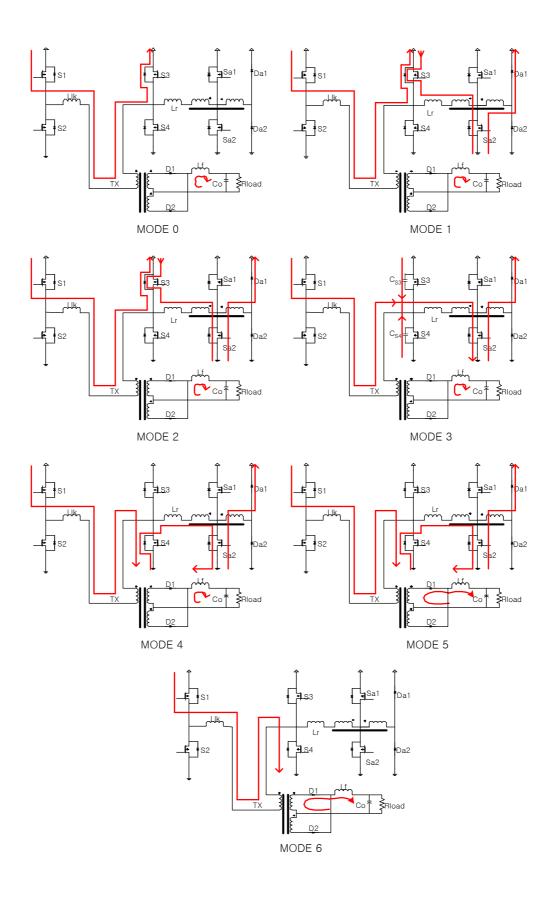

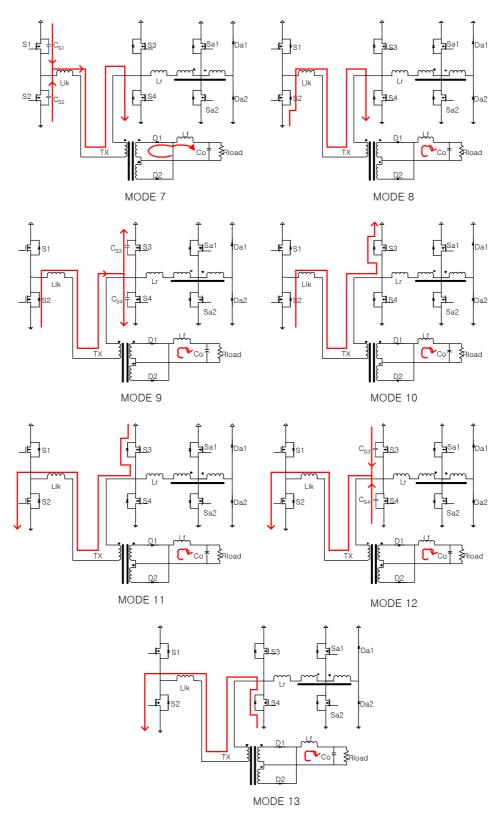

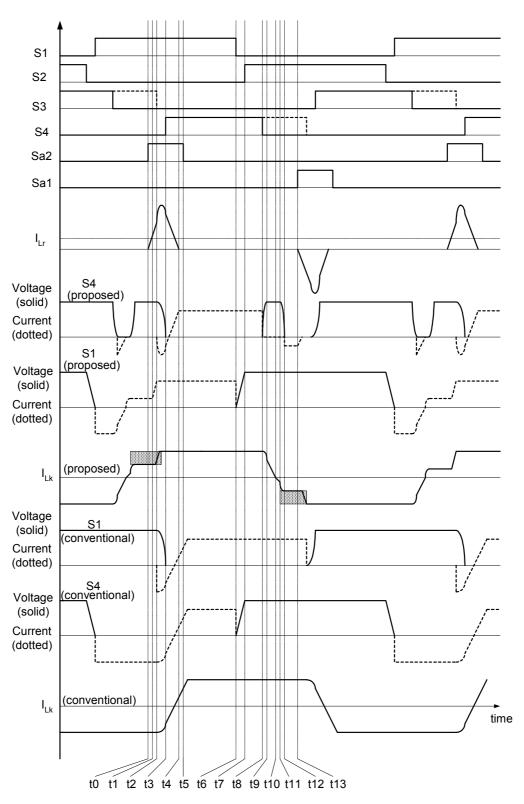

In the following analysis, it is assumed that the output filter is large enough to be considered as a DC current source. Also, all the junction capacitances of the switches are identical. Figure 3 shows the operating modes and conduction paths of the proposed converter. As shown in the figure, the proposed converter has fourteen operation modes during a switching cycle. The key waveforms including the gate pulses are shown in Fig. 4.

MODE 0 [ $\sim$ t0]: S1, S3 and the body diode are ON.

MODE 1 [t0~t1]: At t0, Sa2, S1, S3 are ON, the other switches are OFF. The leakage inductor has a current flow. The resonance inductor current increases linearly up to the

Fig. 2. Proposed full-bridge converter circuit.

leakage inductor current due to the voltage difference between the source and the regenerative transformer  $(T_{aux})$  voltages. In the meantime, some current from the regenerative transformer is recovered to the source through Da1.

$$I_{Lr}(t) = \frac{V_s - \alpha V_s}{L_r} (t - t_0) \quad \text{where} \quad 0 < \alpha < 0.5$$

$$I_{Lkr}(t_1) = I_{Llk}(t_1) = I_{Llk0} \qquad t_o < t < t_1$$

(3)

MODE 2 [t1~t2]: At t1, S1, Sa2 are ON and the others are OFF. The anti-parallel diode current of S3 is conducting during the reverse recovery time. In the meantime, the resonant current increases linearly.

$$I_{Lr}(t) = I_{Llk0} + \frac{V_s - \alpha V_s}{L_r} (t - t_1)$$

(4)

where,

$$I_{Lr}(t_2) = I_{Lr0}$$

$t_1 < t < t_2$ ,

$t_2 - t_1 = t$  (body diode reverse recovery).

The current on the regenerative transformer is recovered to the source through Da1.

MODE 3 [t2 $\sim$ t3]: At t2, the body diode of S<sub>3</sub> naturally turns off. Meanwhile, S1, Sa2 are ON, and the others are OFF. The resonant inductor starts to resonate to the parasitic capacitances of S3 and S4. The voltage across S4 decreases to zero. The turn ratio design for T<sub>aux</sub> is always more than twice as high in the secondary winding than in the primary one.

$$i_{Llk}(t) = -\frac{Z}{L_{lk}\varpi} (I_{Llk0} - I_{Lr0})(1 - \cos \varpi t)$$

$$+ \frac{1}{\varpi} \cdot \frac{(\alpha - 1)}{L_{lk} + L_r} V_S \sin \varpi t - \frac{(\alpha - 1)V_S}{L_{lk} + L_r} t + I_{Llk0}$$

$$i_{Lr}(t) = (I_{Llk0} - I_{Lr0}) \cdot \frac{L_{lk}}{L_{lk} + L_r} (1 - \cos \varpi t)$$

$$- \frac{1}{\varpi L_r} \cdot \frac{L_{lk}}{L_{lk} + L_r} (\alpha - 1)V_S \sin \varpi t + \frac{(1 - \alpha)V_S}{L_{lk} + L_r} t + I_{Lr0}$$

$$v_c(t) = (I_{Llk0} - I_{Lr0})Z \sin \varpi t$$

$$+ \frac{L_{lk}}{L_{lk} + L_r} (\alpha - 1) \cdot V_S \cdot (1 - \cos \varpi t) + V_S$$

(5)

where:

$$Z = \sqrt{\frac{L_{eq}}{C_{eq}}}, L_{eq} = L_{lk} // L_r, C_{eq} = C_{s3} // C_{s4}, \omega = 1 / \sqrt{L_{eq} C_{eq}},$$

$$v_c(t_3) = 0, i_{Llk}(t_3) = I_{Llk1}, i_{Lr}(t_3) = I_{Lr1}.$$

In the meantime, some current from the regenerative transformer is recovered to the source through Da1.

MODE 4 [t3~t4]: At t3, the body diode of S4 naturally turns on and S4 has ZVS turn–on. Simultaneously, the resonance is finished and the current starts to decrease linearly.

$$v_{C}(t) = 0$$

$$i_{Llk}(t) = I_{Llk1} + \frac{V_{S}}{L_{lk}}(t - t_{3}) \qquad i_{Llk}(t_{4}) = I_{Llk2} = \frac{1}{N}I_{0} \quad (6)$$

$$i_{Lr}(t) = I_{Lr1} + \frac{-\alpha V_{S}}{L_{r}}(t - t_{3}) \qquad i_{Lr}(t_{4}) = I_{Lr2}$$

In the meantime, some current from the regenerative transformer is recovered to the source through Da1.

MODE 5 [t4~t5]: At t4, the resonant current becomes zero. The body diode of Sa2 naturally turns off, and Sa2 has ZCS turn-off. S1 and S4 provide the load current.

$$v_{C}(t) = 0$$

$$i_{Llk}(t) = \frac{1}{N} I_{0}$$

$$i_{Lr}(t) = I_{Lr2} + \frac{-\alpha V_{S}}{L_{v}} (t - t_{4}) \qquad i_{Lr}(t_{5}) = 0$$

(7)

MODE 6 [t5~t6]: At t5, the energy recovery part has relaxation. S1 and S4 provide the load current.

$$v_C(t) = 0$$

$i_{Llk}(t) = \frac{1}{N}I_0$   $i_{Lr}(t) = 0$  (8)

MODE 7 [t6~t7]: At t6, S<sub>1</sub> turns off. The load current starts to charge linearly the parasitic capacitances of S1and S2. The voltage across S2 decreases to zero. This period is called the 'active zero voltage switching mode by load current' because the leading switch has ZVS operation.

$$v'_{C}(t) = -\frac{1}{C_{eq}} \cdot \frac{1}{N} I_{0}(t - t_{6}) + V_{S}$$

$$i_{Llk}(t) = \frac{1}{N} I_{0} \quad , \qquad i_{Lr}(t) = 0$$

$$v'_{C}(t_{7}) = 0$$

(9)

MODE 8 [t7~t8]: At t7, the body diode of S2 naturally turns on when the voltage across S2 decreases to zero. Then, S2 has ZVS turn–on. The leakage inductor has current circulation through S2 and S4.

$$v'_{C}(t) = 0$$

$$i_{L/k}(t) = \frac{1}{N} I_0 \Rightarrow I'_{L/k} \quad , \qquad i_{Lr}(t) = 0$$

(10)

MODE 9 [t8~t9]: At t8, S4 turns off. Then, the leakage inductor starts to resonate to the parasitic capacitances of S3 and S4. The inductor energy is proportional to the square of the load current and the switch voltage of S4 rises up to the input voltage when the energy is sufficiently large.

$$v_{C}(t) = I'_{Llk} Z_{1} \sin \varpi_{1}(t - t_{8})$$

$$where, \quad Z_{1} = \sqrt{\frac{L_{lk}}{C_{eq}}} \quad , \quad \varpi_{1} = \frac{1}{\sqrt{C_{eq} \cdot L_{lk}}}.$$

$$i_{Llk}(t) = I'_{Llk} \cos \varpi_{1}(t - t_{8}) \qquad i_{Lr}(t) = 0.$$

(11)

At the end of mode 9,

$$v_C(t_9) = V_S \text{ and } i_{Llk}(t_9) = I'_{Llk0}$$

with an assumption of  $I'_{Llk}Z_1 > V_S$ . (12)

MODE 10 [t9~t10]: At t9, the body diode of S3 turns on. Then, the freewheeling current of the leakage inductance is recovered to the source through the body diode of S2 and S3. The current decreases linearly.

$$v_c(t_9) = V_S = v_C(t_{10})$$

$$i_{Llk}(t) = \frac{-V_S}{L_{lk}}(t - t_9) = I'_{Llk0}, i_{Llk}(t_{10}) = 0 (13)$$

$$i_{Lr}(t) = 0$$

MODE 11 [t10~t11]: At t10, the anti-parallel diode current of S3 is conducting during the reverse recovery time. Meanwhile, the leakage current decreases linearly.

$$i_{Llk}(t) = \frac{-V_S}{L_{lk}}(t - t_{10}) , \quad i_{Lr}(t) = 0$$

$$v_C(t_{10}) = v_C(t_{11}) = V_S, \quad i_{Llk}(t_{11}) = -I'_{Llk1}$$

(14)

MODE 12 [t11 $\sim$ t12]: At t11, the body diode of  $S_3$  naturally turns off. Then, the leakage inductor starts to resonate to the parasitic capacitances of  $S_4$  with the input voltage. The voltage across  $S_4$  decreases to zero through the resonance.

$$v_{c}(t) = -I'_{Llk1} Z_{1} \sin \overline{\omega}_{1}(t - t_{11}) - V_{S}(1 - \cos \overline{\omega}_{1}(t - t_{11})) + V_{S}$$

$$i_{Llk}(t) = -I'_{Llk1} \cos \overline{\omega}_{1}(t - t_{11}) - \frac{V_{S}}{Z_{1}} \sin \overline{\omega}_{1}(t - t_{11})$$

$$v_{c}(t_{12}) = 0, \quad i_{Llk}(t_{12}) = -I'_{Llk2}$$

(15)

MODE 13 [t12 $\sim$ t13]: At t11, the body diode of  $S_4$  naturally turns on and  $S_4$  has ZVS turn–off. Then, the resonance is finished and the leakage inductor has current circulation through the body diodes of  $S_2$  and  $S_4$ .

$$v_c(t) = 0$$

$$i_{Llk}(t) = -I'_{Llk2} - I_{Llk0}$$

(16)

MODE 14 [t13~t0]: At t13, Sa1 turns on. The operation mode then repeats from MODE 0.

## 4. Design Guidelines and Experimental Results

### 4.1 Design guideline

The proposed scheme has the following design considerations:

First, the resonant capacitance for soft-switching is considered. This capacitance includes the junction capacitances between the MOSFET drain and source. A smaller capacitance requires less circulating energy for soft-switching.

Fig. 3. Operating mode and Conduction path of the proposed converter.

Fig. 4. Gating signal and waveforms of proposed and phase-shift full-bridge converter.

Table 1. Major devices used for hardware implementation.

|                       | Parameter / Part number                              | A remarks                                |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Transformer           | PQ4040, 2 pieces<br>Input-parallel,<br>output-series | Primary turns: 36<br>Secondary turns: 13 |

| DC blocking<br>Cap.   | 4.7 uF (63V)                                         |                                          |

| Leak.<br>Inductance   | 25 uH                                                | Extra inductor (10 uH) added             |

| Output Cap.           | 44 uF (250V)                                         |                                          |

| Output<br>Inductance  | 260 uH (40A)                                         | MPP core                                 |

| Main Switch           | 2SK2837 (600V, 20A)                                  | MOSFET 4                                 |

| Rect. Diode           | FML34S (400V, 20A)                                   | Ultra fast diode, 4 pieces               |

| Snubber Cap.          | 0.33 uF (200V)                                       |                                          |

| Snubber Res.          | 22 kΩ (2W)                                           |                                          |

| Snubber<br>Diode      | UF5404                                               | Ultra fast diode,<br>single              |

| Reso.<br>Inductor     | 5 uH                                                 | MPP core                                 |

| Reso. Aux.<br>Switch  | IGBT (600V, 10A)                                     | 2 pieces                                 |

| Reso. Aux.<br>Diode   | MUR860 (600V, 8A)                                    | Ultra fast diode,<br>single              |

| Regen.<br>Transformer | PQ2020                                               | Primary turns: 7<br>Secondary turns: 24  |

Secondly, select the resonant inductance (Lr) according to the features of the full-bridge converter and the auxiliary resonant network. If a resonant inductance is selected that is too small, then the peak and RMS currents are enhanced extremely high as a result of conduction time and zero-switching time shortening. The auxiliary diodes also have a severe reverse-recovery when the slope of the turn-off current is steep. There is a design trade-off between conduction loss and conduction time.

Thirdly, an extra inductor (Llk) to further reduce conduction loss in the proposed scheme as a supplementary device for the leakage inductance is considered. However, since a large inductance leads to the loss of effective duty ratios, there is a trade-off between conduction loss and switching frequency.

Fourthly, the optimal resonance condition determines

the regenerative transformer turn-ratio design. The turn ratio should be lower than a half of the soft-switching.

Finally, select a conduction time for the auxiliary switches according to the leakage inductor current, the resonant inductance, the input voltage, the transformer turn ratios and the load current.

There are also some subsidiary consideration factors such as the reverse-recovery time of the body diodes in lagging-leg switches affecting the design results of the auxiliary resonant network. The reverse time has current injection to the resonant inductor in the ERC. Hence, this time should be included for an optimal circuit design. A design example is presented along with the results of hardware experiments for validating the proposed converter.

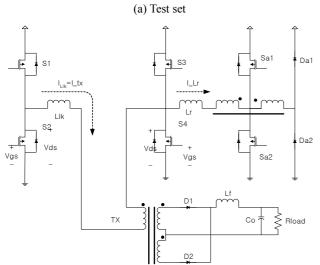

For experimental verification of the design guideline, a hardware prototype was implemented with the specification that the input voltage range is  $200{\sim}400V$  DC, the maximum duty cycle  $D_{max}=0.9$ , the output voltage is 90V DC and the output power is  $100W{-}1kW$ . The switching frequency is 50kHz. Then the turn ratio N of Tx is derived as follows:

$$\begin{split} N &\geq V_{in,\text{min}} \cdot D_{eff} / V_O \\ \text{where} \quad D_{eff} &= D_{\text{max}} - f_{sw} \cdot T_{soft} \,, \\ T_{soft} &= 4\pi / \omega_1 + (t11 - t9) \quad \text{(from eq. (11))}. \end{split}$$

Another transformer, Taux, has a turn ratio that is smaller than 0.5 to confirm the ZVS of S3 and S4. An Lr can be chosen to make a trade off between conduction loss, Trr of the auxiliary ERC and conduction time.

Table 1 shows the design results for the proposed full-bridge converter.

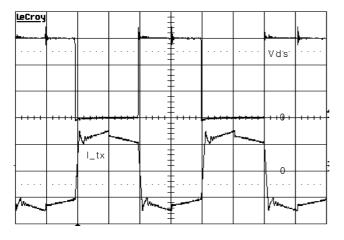

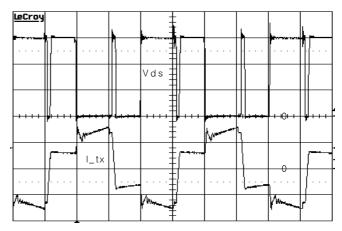

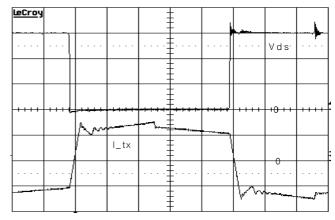

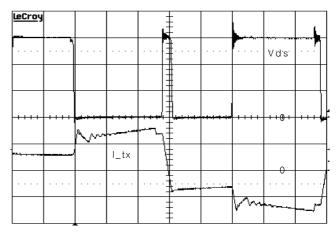

Figures 5(a) and (b) show pictures of the hardware set and the circuit diagram, respectively. The controller has the same operation as that of a conventional phase–shift full-bridge converter except for the ERC part. Figures 6(a) to (d) show a comparison between a conventional and the proposed converter's key waveforms such as transformer current and switching voltage. As shown in figures 6(c) and 6(d), a conventional phase-shift converter has a free-wheeling current of 6A, and the proposed one has a smaller current of 3A in free-wheeling current mode.

Fig. 5. Hardware prototype for experimental test.

(b) Circuit diagram

(a) Transformer's primary current and S4 voltage waveforms in conventional converter (100V/div. 5A/div. 2usec/div.)

(b) Transformer's primary current and S4 voltage waveforms in proposed converter (100V/div. 5A/div. 2usec/div.).

(c) Transformer's primary current and S4 voltage waveforms in conventional converter (100V/div. 5A/div. 1usec/div.)

(d) Transformer's primary current and S4 voltage waveforms in proposed converter (100V/div. 5A/div. 1usec/div.)

Fig. 6. Experimental waveforms of the proposed and the conventional DC/DC converters (Vin 300V, Pout 1000W).

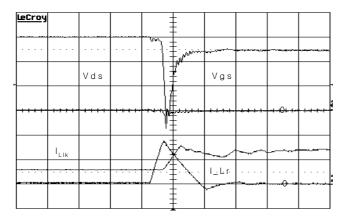

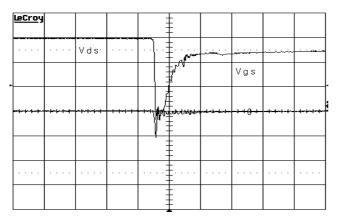

(a) Primary current, resonant inductor current, and Vds, Vgs of S4 in proposed converter (100V/div. 5V/div. 5A/div. 0.5usec/div.)

(b) Vds, Vgs waveforms of leading-leg switch S2 in proposed converter (100V/div. 5V/div. 0.5usec/div.)

Fig. 7. Experimental waveforms of proposed converter (Vin 300V, Pout 1000W).

From figures 6(a) and 6(b), it is also shown that in contrast to a conventional phase-shift converter, the proposed one recovers the circulating energy into the source.

Fig. 7(a) shows that the legging-leg switch in the proposed converter has soft-switching through the ERC regardless of the load condition. The current peak of  $I_{Llk}$  is caused by a current injection from the reverse-recovery of the anti-parallel body diode in the lagging-leg switch. Fig. 7(b) shows that soft-switching is achieved at the leading-leg switch S2, as well.

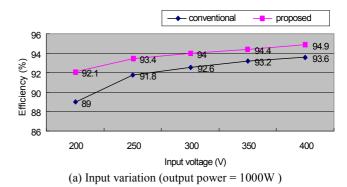

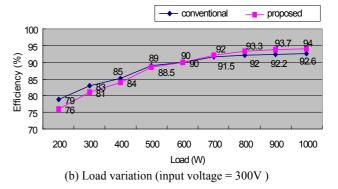

Fig. 8 shows the efficiency graphs for the performance comparison. There is a significant performance improvement with the proposed converter under certain operating conditions, such as a large primary current,

Fig. 8. Efficiency comparison between the conventional and proposed converters.

where the input is low and the load is heavy. The reason is that a circulating current reduction in the primary leads to a conduction loss reduction in the proposed scheme. From the results, the proposed scheme is shown to be suitable for applications with wide input ranges and load variations.

## 5. Conclusion and Further works

In this paper, a new full-bridge converter is proposed which eliminates the effective duty-cycle reduction of conventional phase-shift converters and reduces the conduction loss caused by primary current circulation. The converter has an extra auxiliary resonant network to support soft-switching operation in the main switches under wide input voltage and load variation. The resonant network includes a small-size regenerative transformer and switching devices connected to the lagging-leg side. The proposed converter has excellent power efficiency especially when the input is low and the load is heavy. The steady-state operation mode analysis and design

guidelines are proposed and verified by hardware experiments with a 1kW converter prototype for measuring the key waveforms and the power efficiency. The maximum efficiency was 94% at full-load.

The proposed soft-switching converter concept can be extended by applying other energy recovery circuits in a PDP sustain driver to conventional phase-shift converters. The extended power-conversion topology family with an extra resonant network will be examined in the future.

#### References

- [1] I. Barbi, D. C. Martins, "A true PWM zero-voltage switching pole with very low additional rms current stress," *Proc. PESC'91*, pp.261-267,

- [2] W. McMurray, "Resonant snubbers with auxiliary switches," *IEEE Trans. Ind. Applicat.*, Vol.29, pp.335-362, Mar./Apr. 1993.

- [3] R. W. De Doncker, J. P. Lyons, "The auxiliary resonant commutated pole converter," *Conf. Rec. IEEE IAS Annual Meeting*, pp.1228-1235, 1990.

- [4] C. P. Henze, H. C. Martin, D.W. Parsley, "Zero-voltage-switching in high frequency power converters using pulse width modulation," *IEEE Applied Power Electronics Conf. Proc.*, pp. 33-40, 1988.

- [5] G. Hua, F. C. Lee, "A new class of ZVS-PWM converters," High Frequency Power Conversion Conf. Rec., pp. 244-251, 1991.

- [6] G. Hua, C. Leu, F. C. Lee, "Novel zero-voltage-transition PWM converters," *VPEC Power Electronics Seminar Proc.*, pp. 81-88, 1991.

- [7] D. C. Martins, F. Seixas, J. A. Brilhante, I. Barbi, "A family of dc-to-dc converter using a new ZVS commutation cell," *IEEE Power Electronics Specialists Conf. Rec.*, pp.524-530, 1993.

- [8] J. Gegner, C. Q. Lee, "Zero-voltage-transition PWM converters using an inductor feedback technique," *IEEE Applied Power Electronics Conf. Proc.*, pp. 862-868, 1994.

- [9] G. Hua, F. C. Lee, "An overview of soft-switching techniques for PWM converters," *EPE Journal*, Vol. 3, No 1, March 1993. Also: 4th European Power Electronics Conf. Proc., 1993.

- [10] J. A. Sabate', V. Vlatkovic, R. D. Ridley, F. C. Lee, B. H. Cho, "Design considerations for high-voltage high-power full-bridge zero voltage switched PWM converters," *Proc. IEEE APEC*, pp.275-284, 1990.

- [11] J. G. Cho, J. L. Sabate', G. Hua, F. C. Lee, "Zero voltage and zero current switching full-bridge PWM converter for high power applications," *Proc. IEEE PESC*, pp.102-108, 1994

- [12] J. Cho, J. Sabate, F. C. Lee, "Novel full-bridge ZVT-PWM dc-dc converter for high-power applications," *IEEE Applied Power Electronics Conf. Proc.*, pp. 143-149, 1994.

- [13] Jung G. Cho, Ju W. Baek, D.W. Yoo, Hong S. Lee, and Geun H. Rim, "Novel Zero-Voltage and Zero-Current-Switching(ZVZCS) Full Bridge PWM Converter Using Transformer Auxiliary Winding," *IEEE Power Electronics Specialist Conf. Rec.*, pp. 227-232, 1997.

- [14] Jung G. Cho, J. W. Baek, D.W. Yoo, H. S. Lee, and G. H. Rim, "Novel Zero-Voltage and Zero-Current-Switching (ZVZCS) Full Bridge PWM Converter Using a simple auxiliary circuit," *IEEE APEC Rec.*, pp.834-839, 1998.

- [15] Hang-Seok Choi; Jung-Won Kim; Bo H. Cho, "Novel zero-voltage and zero-current-switching (ZVZCS) full-bridge PWM converter using coupled output inductor," *IEEE Transactions on Power Electronics*, Vol. 17, No. 5, pp. 641-648, Sep. 2002.

- [16] H. S. Choi, J. W. Kim, J. H. Lee and B. H. Cho, "Analysis and Design Considerations of Zero-Voltage and Zero-Current-Switching (ZVZCS) Full-Bridge PWM Converters," *IEEE Power Electronics Specialist Conference*, Vol. 4., pp. 1835-1840, 2002.

- [17] Woo-Sup Kim, Jong-Won Shin, Su-Yong Chae, Byung-Chul Hyun and Bo-Hyung Cho, "A Study of a Simple PDP Driver Architecture using the Transformer Network," *Journal of Power Electronics*, Vol. 8, No. 2, pp. 148-155, April 2008.

- [18] Sangshin Kwak, Jin-Woo Jung, Dong-Myung Lee, Tae-Seung Cho, "A New Sustain Driver with Energy Recovery Circuit based on Low-Voltage Components and Low-Voltage Power Supply for AC Plasma Display Panel," *IEEE Transactions on Consumer Electronics*, Vol. 54, No. 3, pp. 1321-1328, Aug. 2008.

- [19] D.Y. Lee, J. H. Yang, and B. H. Cho, "Novel Energy-Recovery Driving Circuit for Plasma Display Panel using Regenerative Transformer," *PESC03*, Vol. 2, pp. 656-659, Jun. 2003.

- [20] W. S. Kim, S. Y. Chae, B. C. Hyun, D. Y. Lee, and B. H. Cho, "A Cost Effective PDP Sustainer using Two-Winding Transformer with Hybrid Operation," *Applied Power Electronics Conference*, pp. 294-298, 2007.

- [21] Y. Jin Ho, K. Joong Kyun, and W. Ki Woong, "An energy recovery circuit for AC plasma display panel with series CLC resonance-SER1," Consumer Electronics, IEEE Transactions on, Vol. 51, pp. 718-724, 2005.

- [22] L. Jun-Young, K. Jin-Sung, J. Nam-Sung, and Bo-Hyung Cho, "The current injection method for AC plasma display panel (PDP) sustainer," *Industrial Electronics*, *IEEE Transactions on*, Vol. 51, pp. 615-624, 2004.

- [23] Jun-Young Lee, Jin-Sung Kim, Myeong-Seop So, and Bo-Hyung Cho, "New Energy Recovery Concept for AC PDP Sustaining Driver Using Current Injection Method(CIM)," *Journal of Power Electronics*, Vol. 2, No.3, pp. 189-198, 2002.

- [24] Sang-Kyoo Han, and Myung-Joong Youn, "High Performance and Low Cost Single Switch Current-fed Energy Recovery Circuits for AC Plasma Display Panels," *Journal of Power Electronics*, Vol. 6, No.3, pp. 253-263, 2006.

- [25] Seong-Wook Choi, Sang-Kyoo Han, and Gun-Woo Moon, "High Frequency and High Luminance AC-PDP Sustaining Driver," *Journal of Power Electronics*, Vol.6, No.1, pp. 73-82, 2006.

- [26] Kang-Hyun Yi, Sang-Kyoo Han, Seong-Wook Choi, Chong-Eun Kim, and Gun-Woo Moon, "A Simple ZVZCS Sustain Driver for a Plasma Display Panel," *Journal of Power Electronics*, Vol.6, No.4, pp. 298-306, 2006.

- [27] Sang-Kyoo Han, Gun-Woo Moon, and Myung-Joong Youn, "A Novel Current-fed Energy Recovery Sustaining Driver for Plasma Display Panel (PDP)," *Journal of Power Electronics*, Vol.4, No.1, pp. 39-45, 2004.

- [28] R. Chung-Wook, "Novel plasma display driver with low voltage/current device stresses," *Consumer Electronics*, *IEEE Transactions on*, Vol. 49, pp. 1360-1366, 2003.

- [29] Jun-Young Lee, "Dual Path Magnetic-Coupled AC-PDP Sustain Driver with Low Switching Loss," *Journal of Power Electronics*, Vol. 6, No.3, pp. 205-213, 2006.

- [30] Jongwon Shin, Woosup Kim, Joung-Hu Park, Bo-Hyung Cho, "A New Energy-Recovery Circuit for the Plasma Display Panel Using the Switched Transformer," *PESC*, pp.1857-1861, June 2008.

**Dong-Young Lee** was born in Korea in 1971. He received his B.S, M.S., and Ph.D. from the Electrical Engineering and Computer Science department of Seoul National University, Seoul, South Korea in 1995, 1997, and 2003, respectively. From 2003 to

2005, he was a researcher at Samsung SDI Co. He is currently a senior system engineer at International Rectifier in California, USA. His interests include analysis and design of plasma display systems, renewable energy systems, high-frequency switching converters, etc.

**Bo-Hyung Cho** was born in Korea in 1952. He received B.S. and M.E. degrees in electrical engineering from the California Institute of Technology, Pasadena, and his Ph.D., also in electrical engineering, from the Virginia Polytechnic Institute and State

University (Virginia Tech), Blacksburg. Prior to his research at Virginia Tech, he worked for two years as a member of the technical staff in the Power Conversion Electronics Department at TRW Defense and Space System Group, where he was involved in the design and analysis of spacecraft power processing equipment. From 1982 to 1995, he was a professor in the Department of Electrical Engineering, Virginia Tech, Blacksburg, Virginia. He joined the school of Electrical Engineering, Seoul National University, Seoul, Korea in 1995 where he is presently a professor. His main research interests include power electronics, modeling, analysis and control of spacecraft power processing equipment, power systems for space stations and space platforms, and distributed power systems.

Joung-Hu Park was born in Korea in 1975. He received his B.S, M.S., and Ph.D. from the Electrical Engineering and Computer Science department of Seoul National University, Seoul, South Korea in 1999, 2001, and 2006, respectively. From 2006 to

2009, he was a post doctoral researcher at Seoul National University. He is currently a full-time lecturer in Soongsil Univ. in Seoul, Korea. His research interests include the analysis and design of high-frequency switching converters, renewable energy systems, piezoelectric transformer power applications, etc.