# JPE 13-4-11

# Analysis of the Admittance Component for Digitally Controlled Single-Phase Bridgeless PFC Converter

Younghoon Cho\*<sup>†</sup>, Hyungsoo Mok\*, and Jih-Sheng Lai\*\*

<sup>\*†</sup>Dept. of Electrical Eng., Konkuk University, Seoul, Korea <sup>\*\*</sup>Dept. of Electrical and Computer Eng., Virginia Tech, Blacksburg, USA

#### Abstract

This paper analyzes the effect of the admittance component for the digitally controlled single-phase bridgeless power factor correction (PFC) converter. To do this, it is shown how the digital delay effects such as the digital pulse-width modulation (DPWM) and the computation delays restrict the bandwidth of the converter. After that, the admittance effect of the entire digital control system is analyzed when the bridgeless PFC converter which has the limited bandwidth is connected to the grid. From this, the waveform distortion of the input current is explained and the compensation method for the admittance component is suggested to improve the quality of the input current. Both the simulations and the experiments are performed to verify the analyses taken in this paper for the 1 kW bridgeless PFC converter prototype.

Key words: Admittance compensation, Bridgeless PFC converter, Digital current controller, K-factor approach

#### I. INTRODUCTION

Single-phase power factor correction (PFC) converters have been used for many industrial applications such as aircraft power supplies, light-emitting-diode drivers. electronic ballast circuits, and so on [1]-[5]. Among many circuit topologies for PFC operation, the bridgeless PFC topology which does not have the diode bridge for rectification of the input voltage and current is getting popular because the topology features high efficiency and simple control [6]-[8]. Generally, controllers for the bridgeless PFC converter are not different from the ones of the traditional boost PFC converters, in where a voltage controller as an outer loop and a current controller as an inner loop are employed. For the voltage controller, the bandwidth is selected to be lower than the fundamental electrical frequency to minimize the well-known double frequency power fluctuation effect for the control loop. However, for the current controller, the bandwidth is required to have as high as possible to regulate the shape of the input current as the input voltage [9]. Consequently, maximizing the

bandwidth of the current controller is an important issue for the single-phase bridgeless PFC converter. The current controller can be implemented either in analog or in digital control scheme. In terms of regulating performance, analog controllers may show better results than digital controllers. However, digital controllers have more flexibility to implement entire control system including operating sequences, communication features, fault protections, and so on. Hence, adapting the digital control techniques is getting popular for the bridgeless PFC converters. Basically, most of the existing control schemes for traditional boost PFC converter can be directly applied to the bridgeless PFC converter. In [10], the current sharing and the proportional-integral (PI) controllers are designed for digital signal processor (DSP) based interleaved boost PFC converter. A predictive control strategy has been proposed in [11]. Some papers have been discussed about continuous conduction mode (CCM) and discontinuous conduction mode (DCM) operations for the single-phase boost PFC converters [12]-[15]. Reference [16] discusses that the digital delays normally degrade the performance of the digital current controller by analyzing the small-signal model considering the time delay effect as well as evaluating the stability of the converter. In [17], the transfer functions for a digitally controlled PFC converter have been described with consideration of the digital delay effects. On the other hand, the duty feed-forward schemes have been studied to improve

Manuscript received Mar. 22, 2012; revised Apr. 5, 2013 Recommended for publication by Associate Editor Jinjun Liu.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: yhcho98@konkuk.ac.kr

Tel: +82-2-450-0519, Fax: +82-2-447-9186, Konkuk University

<sup>&</sup>lt;sup>\*</sup>Dept. of Electrical Eng., Konkuk University, Korea

<sup>\*\*</sup>Dept. of Electrical and Computer Eng., Virginia Tech, USA

the quality of the input phase current. The impedance analyses have been performed with and without the duty feed-forward scheme, and it is proven that the duty feed-forward scheme can improve the behavior of the current controller [17]. Reference [18] proposes the feed-forward control which includes a term proportional to the derivative of the reference current. The duty feed-forward schemes can be also called as "admittance compensation method" in some literatures [19]-[21] because the effect of the input voltage fluctuation can be physically modeled as an admittance component in the entire control system.

In this paper, the effect of the admittance component is analyzed for the digitally controlled single-phase bridgeless PFC converter. To consider the digital delay effects, a zero-order-hold (ZOH) which causes phase delay in high frequency regions and reduces the phase margin of the plant is included into the control-to-inductor current model. By using the derived model and assuming a type-II compensator is employed, the maximum achievable bandwidth of the converter is evaluated with the given parameters and the operating conditions. Then the design procedure for the type-II compensator based current controller is described in detail. After that, the admittance component is analyzed in the entire control loop. Apparently, the analysis taken in this paper shows that the effect of the admittance component with the digital controller is more severe than analog controllers because of the reduced bandwidth. In order to compensate the admittance component effect, the admittance compensation method which may be a similar form with the duty feed-forward schemes is introduced. The simulations and the experiments have been carried out to verify the analyses taken in this paper and the effect of the admittance compensation strategy for the 1 kW bridgeless PFC converter.

## II. MODELING OF THE BRIDGELESS PFC CONVERTER

#### A. The Analog and the Digital Models

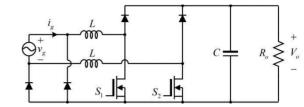

Fig. 1 shows the bridgeless PFC converter dealt in this paper. In terms of the control of the bridgeless PFC converter, the input phase current and the output voltage controllers are necessary. Generally, the performance of the current controller affects the performance of the PFC converter a lot. In order to design the current controller, a control-to-inductor current model for the bridgeless PFC converter may be needed. Usually, the control-to-inductor current model can be expressed as a second order function. However, the first order model as shown in (1) is also a popular solution to simplify the analysis [21].

$$G_{id}(s) = \frac{V_o}{sL} \tag{1}$$

Fig. 1. Circuit configuration of the bridgeless PFC converter.

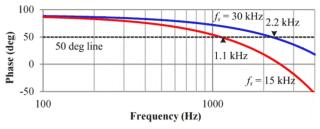

Fig. 2. Changes of  $\theta_{idz}$  according to  $f_s$ .

| TABLE I           The Maximum Bandwidth of the Bridgeless PFC Converter |             |             |             |             |  |

|-------------------------------------------------------------------------|-------------|-------------|-------------|-------------|--|

| Phase margin                                                            | 40          | 50          | 60          | 70          |  |

| Bandwidth                                                               | $0.091 f_s$ | $0.073 f_s$ | $0.055 f_s$ | $0.036 f_s$ |  |

where  $V_o$  represents the output dc-link voltage. Although (1) does not contain the LC resonance which can be found in the second order model, it is enough to be utilized for current controller design. If the triangular carrier waveform is employed, and the digital controller and the DPWM are updated once in a switching period, the modulator can be modeled as a ZOH [22]. By considering the typical one sample delay in a digital controller [23], the control-to-inductor current model  $G_{idz}(z)$  which consider the plant model of the bridgeless PFC converter is simply modeled as,

$$G_{idz}(z) = \frac{T_s V_o}{L} \frac{1}{z(z-1)}$$

(2)

where  $T_s$  represent the sampling frequency which is inverse proportional to the switching frequency  $f_s$ . Equation (2) will be utilized to design the digital feedback controller which will be discussed in a later section.

### *B.* Bandwidth limitation of the Digitally Controlled Bridgeless PFC Converter

In this section, the limitation of the current control bandwidth is discussed. To design the feedback controller, it is assumed that K-factor design based type-II compensator is employed. Note that a type-II compensator induces maximum 90 deg of the phase boost effect. In this paper, the target phase margin is selected to be 50 deg to operate the entire control system in stable. From (1), it can be intuitively recognized that the phase margin of the *s*-domain model can be 90 deg in the entire frequency region. Unlike the *s*-domain

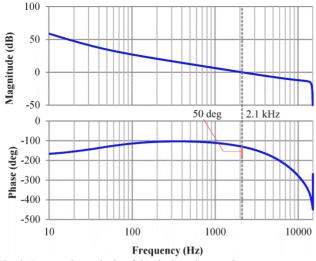

Fig. 3. Loop gain analysis of the designed control system.

| TABLE II<br>The Parameters of the Bridgeless PFC Converter |         |  |  |

|------------------------------------------------------------|---------|--|--|

| Rated power $(P_o)$                                        | 1 kW    |  |  |

| Input RMS voltage $(V_{g_rms})$                            | 120 V   |  |  |

| Output dc-link voltage $(V_o)$                             | 200 V   |  |  |

| Input filter inductance (L)                                | 800 μΗ  |  |  |

| Output dc-link capacitance (C)                             | 1120 μF |  |  |

| Switching frequency $(f_s)$                                | 30 kHz  |  |  |

model, the *z*-domain model in (2) may have phase lagging in high frequency region because of the delays caused from the DPWM and the digital calculation delay. Accordingly, the phase margin of  $G_{idz}(z)$  is reduced in high frequency regions. It should be noted that the phase margin of  $G_{idz}(z)$  is the maximum achievable phase margin in the closed-loop control system with the type II compensator. By substituting  $z = e^{j2\pi f_r T_s}$  and manipulating several steps, the maximum achievable phase margin can be derived as,

$$\theta_{idz} = -\tan^{-1} \left( \frac{\sin\left(4\pi f_r T_s\right) - \sin\left(2\pi f_r T_s\right)}{\cos\left(4\pi f_r T_s\right) - \cos\left(2\pi f_r T_s\right)} \right) \times \frac{180}{\pi}$$

(3)

where  $f_r$  is the evaluating frequency. If  $f_r$  is fixed,  $\theta_{idz}$  depends on  $T_s$  from (3).

Fig. 2 illustrates the changes of  $\theta_{idz}$  when the switching frequencies are 30 kHz and 15 kHz. If over 50 deg of phase margin is guaranteed in the control system,  $\theta_{idz}$  should be higher than 50 deg at the crossover frequency. The frequencies which satisfy the condition above are 2.2 kHz for  $f_s = 30$  kHz and 1.1 kHz for  $f_s = 15$  kHz in Fig. 2. Consequently, the maximum bandwidths which secure 50 deg of phase margin are evaluated as 2.2 kHz and 1.1 kHz for  $f_s = 30$  kHz and 15 kHz, respectively. Table I shows the maximum achievable bandwidth at the different phase margins when  $f_s$  is fixed as 30 kHz. Note that unlike an analog controller implementation which generally maximizes

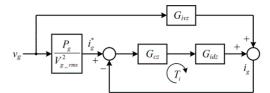

Fig. 4. Current control loop of the bridgeless PFC converter.

the control bandwidth up to  $0.16f_s$  with 40 deg of phase margin, the bandwidth of the digital controller is much reduced as shown in Table I. This is one of the key issues which degrade the quality of the input current waveform in the digitally controlled bridgeless PFC converter.

#### C. Digital Current Controller Design

The general expression of a type-II based digital feedback controller is given as [24], [25],

$$G_{cz}(z) = \omega_c G_b \frac{T_s(z+1)}{2(z-1)} \left( \frac{\omega_c T_s(z+1) + 2K(z-1)}{K \omega_c T_s(z+1) + 2(z-1)} \right)$$

(4)

where  $\omega_c$  and K are represented as,

$$\omega_c = \frac{2}{T_s} \tan\left(f_c T_s \pi\right) \tag{5}$$

$$K = \sqrt{\frac{\left(1 + \sin\left(\left(PM - (90^{\circ} - \phi_{b})\right)\frac{\pi}{180}\right)\right)}{\left(1 - \sin\left(\left(PM - (90^{\circ} - \phi_{b})\right)\frac{\pi}{180}\right)\right)}}$$

(6)

where  $f_c$  and *PM* mean the crossover frequency of the control system and the required phase margin at  $f_c$ . Note that (5) reflects the pre-warped frequency by considering the digitalization effect. In (4) and (6),  $G_b$  and  $\phi_b$  denote the gain-boost and the phase-boost constants, respectively. Physically,  $G_b$  and  $\phi_b$  are the required gain and phase which are adjusted by the feedback controller to achieve the desired design specification. In this paper, for a stable operation of the digitally controlled bridgeless PFC converter, the crossover frequency and the phase margin of the digital control system are chosen as,

$$f_c = 0.07 f_s$$

$PM = 50 \deg$  (7)

The converter parameters are shown in Table II. By using the parameters in the table and the design specification,  $G_b$ ,  $\phi_b$  and K are calculated as,

$$G_{b} = |G_{idz}(z)| = 25.62 \approx 0.0524$$

$$\phi_{b} = \angle |G_{idz}(z)| = 127.8 \deg$$

$$K \approx 52.08$$

(8)

By substituting these values into (4), the digital feedback controller  $G_{cz}(z)$  is numerically derived as,

$$G_{cz}(z) = 0.04842 \frac{(z+1)(z-0.9915)}{(z-1)(z+0.8418)}$$

(9)

On the other hand, by using Table II, the numerical expression of the control-to-inductor current model  $G_{idz}(z)$

can be calculated as,

$$G_{idz}(z) = \frac{8.333}{z(z-1)}$$

(10)

From (9) and (10), the loop-gain of the digital current control system  $T_i(z)$  is derived as,

$$T_i(z) = G_{cz}(z)G_{idz}(z) = \frac{0.4035(z+1)(z-0.9915)}{z(z+0.8418)(z-1)^2} \quad (11)$$

The loop-gain of the current control system versus the frequency ranges from 10 Hz to the Nyquist frequency 15 kHz is shown in Fig. 3. As shown in the figure, the crossover frequency and the phase margin at the crossover frequency of  $T_i(z)$  satisfies the required design specification  $0.07f_s$ (=2.1 kHz) and 50 deg.

#### III. ADMITTANCE COMPENSATION

#### A. Derivation of the Admittance Component in Z-domain

Fig. 4 shows the current control model of the bridgeless PFC converter shown in Fig. 1. From Fig. 4, the digital control model for the input current  $i_{\sigma}$  is given as,

$$i_g(z) = \frac{G_{ivz}(z)}{1 + T_i(z)} v_g(z) + \frac{T_i(z)}{1 + T_i(z)} \frac{P_g}{V_{g_{z},rms}^2} v_g(z)$$

(12)

where  $P_g$  means the input power. The input power stage line-to-current model  $G_{ivz}(z)$  is represented as,

$$G_{ivz}(z) = \frac{T_s}{L} \frac{1}{z(z-1)}$$

(13)

As similar to the method in [21], from (11), the closed-loop input admittance model in *z*-domain is derived as,

$$Y_{z}(z) = \frac{i_{g}(z)}{v_{g}(z)} = \frac{G_{ivz}(z)}{1 + T_{i}(z)} + \frac{T_{i}(z)}{1 + T_{i}(z)} \frac{P_{g}}{V_{g_{-rms}}^{2}}$$

(14)

#### B. Analysis of the Admittance Component

Equation (14) can be separated into the two components below.

$$Y_{zv}(z) = \frac{G_{ivz}(z)}{1 + T_i(z)}, \qquad Y_{zi}(z) = \frac{T_i(z)}{1 + T_i(z)} \frac{P_g}{V_{g_rms}^2}$$

(15)

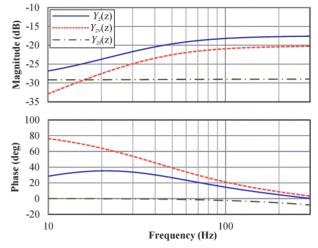

Fig. 5 shows the frequency responses of  $Y_{zv}(z)$ ,  $Y_{zi}(z)$ , and  $Y_z(z)$  when  $P_g$  is 500 W. In physical,  $Y_{zi}(z)$  represents the admittance component for the closed-loop duty-to-inductor current, and  $Y_{zv}(z)$  means the closed-loop input power admittance component. As shown in Fig. 5, the magnitude of  $Y_{zi}(z)$  is almost constant in the evaluated frequency range. Furthermore, the phase of  $Y_{zi}(z)$  is also unvarying near the fundament frequency 60 Hz, but getting lagged in higher frequencies. Both of the magnitude and the phase of  $Y_{zi}(z)$  shows a good agreement with a normal feedback control system. However, a large phase leading is observed at the low frequency region for  $Y_{zv}(z)$ . The magnitude of  $Y_{zv}(z)$  is even

Fig. 5. Frequency responses of the admittance components.

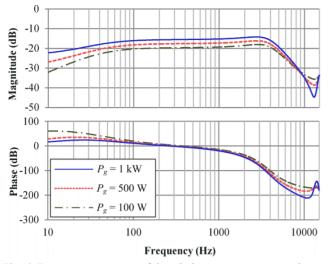

more than  $Y_{zi}(z)$  over 16 Hz. Consequently, the admittance of the entire control system over 16 Hz is mainly determined by  $Y_{zy}(z)$ . Generally, the fundamental and the third harmonic components affect the shape of the input current. In Fig. 5, the phases of the admittance component are leading at the fundamental frequency 60 Hz and the third harmonic frequency 180 Hz. This implies the input current will lead the input voltage. On the other hand, the response of  $Y_z(z)$ depends on the input power  $P_g$  from (14) which includes  $Y_{zi}(z)$ . Fig. 6 shows the frequency responses of  $Y_z(z)$  at different input power levels. As shown in the figure, more phase lagging is found under lower  $P_g$  conditions near the fundamental frequency. Consequently, it is supposed that the phase leading effect is dominant as  $P_g$  becomes lower. If an analog controller is applied so that the bandwidth of the entire control system is large enough to overcome the admittance component, the shape of the input current can be a beautiful sinusoidal waveform even with only a simple feedback control. However, in the digitally controlled bridgeless PFC converter, the admittance component cannot be compensated even at the fundamental frequency because of the lower bandwidth of the digital current controller from this analysis. This explains why the admittance compensation loop is essentially required in the digital PFC control.

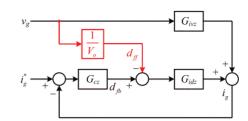

#### C. Admittance Compensation

The admittance compensation methods have been emphasized in many previous studies [16] – [18]. There are basically two methods, the current reference correction and the duty feed-forward, to compensate the admittance component. Especially, many research papers have been discussed about the duty feed-forward method [14] – [15]. In this paper, the duty feed-forward method as shown in Fig. 7 is employed to compensate the admittance component. Without the duty feed-forward scheme, the input current  $i_g$  is

Fig. 6. Frequency responses of the admittance component at the different power levels.

simply written as,

$$i_g(z) = d_{fb}G_{idz}(z) + v_g G_{ivz}(z)$$

(16)

In fact, from (2) and (13), there is a relation between  $G_{idz}(z)$  and  $G_{ivz}(z)$  as below.

$$G_{idz}(z) = V_o G_{ivz}(z) \tag{17}$$

By considering the feed-forward duty  $d_{ff}$ ,  $i_g$  is represented as,

$$i_{g}(z) = (d_{fb} - d_{ff})G_{idz}(z) + v_{g}G_{ivz}(z)$$

$$= d_{fb}G_{idz}(z) - \frac{v_{g}}{V_{o}}V_{o}G_{ivz}(z) + v_{g}G_{ivz}(z) = d_{fb}G_{idz}(z)$$

(18)

From (18), it can be seen that ideally  $G_{ivz}(z)$  is no longer existed in  $i_g$  by using  $d_{ff}$ . In fact, there is a digital sampling effect which is modeled as the ZOH between the feed-forward duty  $d_{ff}$  and the input voltage  $v_g$ . However, the sampling frequency is 500 times faster than the fundamental frequency in this paper, and the phase delay effect caused by the ZOH is just 0.036° which can be ignored for the fundamental frequency.

#### IV. SIMULATION

The simulations were carried out to address the effects of the bandwidth limitation and the admittance component. For the simulation, a simulation software package PSIM was utilized. The same simulation parameters in Table II were also applied. As the feedback controller, the controller in (9) was implemented.

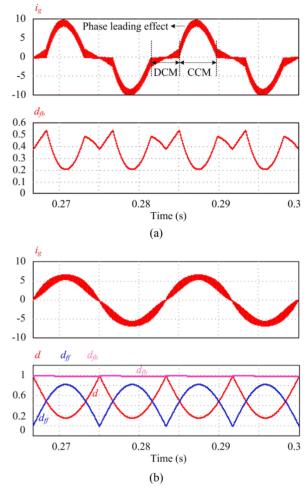

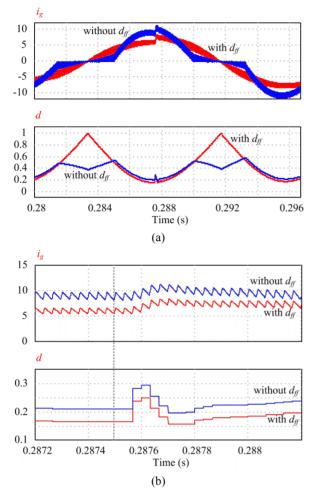

Fig. 8 compares the input phase current and the duty references of the bridgeless PFC converter without and with the admittance compensation. Note that the output voltage and the output power are the same in both of the cases. In Fig. 8(a), the input phase current  $i_g$  is severely distorted because of the phase leading current effect which is caused by the

Fig. 7. Duty feed-forward method for admittance compensation.

Fig. 8. Comparison of the simulation results. (a) without the admittance compensation. (b) with the admittance compensation.

admittance component. In the result, the zero crossing points (ZCP) occurred in advance of normal ZCPs. Consequently, the zero current clamping effect is dominant in the current response because of the advanced ZCPs. In addition to this, the system is operated in DCM which deteriorates the input current quality near the ZCPs. Note that the duty reference  $d_{fb}$  never reach to 1.0 which is the ideal duty reference near ZCPs of the input voltage. Even if the current is increased so that the system goes into CCM, the shape of the input current is not pure sinusoidal but phase leaded sinusoidal because of the phase leading effect of the admittance component. Fig. 8(b) shows the input current response when both the feedback controller and the admittance compensation strategy are

Fig. 9. Comparison of the transient response. (a) normal view. (b) zoomed in view.

applied. As shown in the figure,  $i_g$  is well regulated as a sinusoidal shape, and the distortion near the ZCPs are much smaller than in Fig. 8(a). In terms of the duty cycles, the variation of the duty cycle from the feedback control  $d_{tb}$  is very small because the feed-forward duty  $d_{ff}$  takes most of the required duty variation for the input voltage fluctuation. Consequently, the total duty cycle d to the modulator is mainly reflecting the shape of the inversed  $d_{ff}$ . Compared to Fig. 8(b), the maximum amplitude of the input current waveform in Fig. 8(a) is almost 1.5 times higher than the one in Fig. 8(b) even if the operating power is the same. Accordingly, it requires higher current rating of the power semiconductors, and increases the cost. Fig. 9 shows the transient responses of the bridgeless PFC converter with and without the admittance compensation. In Fig. 9(a), the current reference is increased by 25 percent in step at t = 0.2875 s. Fig. 9(b) compares the zoomed in waveforms of the input current  $i_g$  and the total duty cycle d with and without the admittance compensation. As in Fig. 9(b), the magnitude of the overshoot and the tendency of the duty variance are almost similar in both the cases. This implies that the

Fig. 10. Experimental setup.

characteristics of the feedback controller in the two control strategies are almost the same. From this, paradoxically, the quality of the input current is mainly determined by the admittance compensation in the digitally controlled bridgeless PFC converter. Regarding the magnitude of the peak current,  $i_g$  without the admittance compensation is higher than the case with the admittance compensation, because the input voltage fluctuation acts as a disturbance which may not be compensated by the feedback controller only. Accordingly, the admittance compensation method can be also considered as a feed-forward controller to compensate the predictable disturbance in the view point of the control theory.

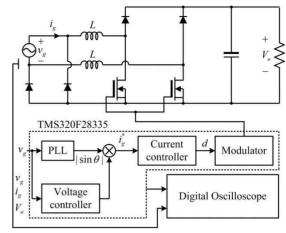

#### V. EXPERIMENTAL RESULTS

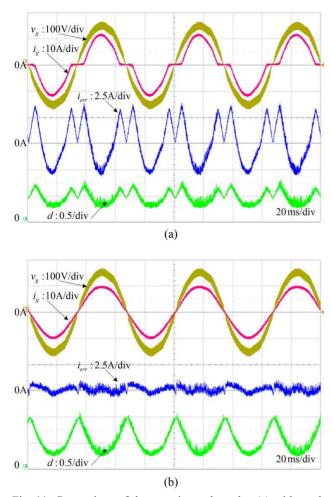

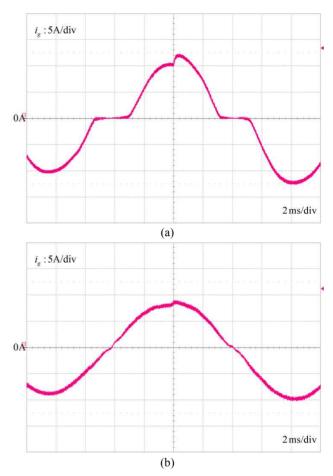

In order to verify the analysis taken in this paper, the experiments have been carried out using the bridgeless PFC converter which has the same parameters in Table II. Fig. 10 shows the experimental configuration for the test. The phase locked loop (PLL) algorithm is implemented to generate the sinusoidal reference. To implement the digital control algorithm, Texas Instruments' 32 bit DSP TMS320F28335 has been employed. The DSP board includes the 4 channel digital-to-analog converter (DAC) to monitor the DSP inside variables through the digital oscilloscope. The digital controller derived in (9) has been implemented as the feedback controller for the all experiments. Fig. 11 compares the steady state current waveforms with and without the admittance compensation. In Fig. 11(a), the input current is severely distorted near ZCPs as similar in Fig. 8(a). The maximum current error between the current reference and the actual phase current is around 3.5 A. On the other hand, if the admittance compensation is applied, the shape of the input current becomes more sinusoidal as shown in Fig. 11(b). The distortion near ZCPs is much reduced compare to the previous case. With the admittance compensation, the phase current error ranges within 1.25 A. Fig. 12 compares the step

Fig. 11. Comparison of the experimental results. (a) without the admittance compensation. (b) with the admittance compensation.

current responses without and with the admittance compensation. At t = 0.01 s, the magnitude of the current reference is changed from 8 A to 10 A. In order to be free from the dynamics of the voltage control effect, the current reference itself was changed, and the voltage control loop was not considered. In both of the cases, there are not severe overshoot or ringing at the phase current, and the shapes of the current responses are similar to the simulation results in the previous section. In Fig. 12(a), it is found that the magnitude of the phase current near the peak of the reference always has a current error. This means that the current regulation is not performed very well without the admittance compensation as expected.

#### VI. CONCLUSION

The limitations of the digital current controller and the admittance component were discussed for the digitally controlled bridgeless PFC converter. The *z*-domain transfer function of the bridgeless PFC converter was derived. By analyzing the maximum achievable bandwidth of the digital

Fig. 12. Comparison of the step current responses. (a) without the admittance compensation. (b) with the admittance compensation.

current controller, it had been shown that the phase current distortion which is caused by the admittance component in the control system and the limited bandwidth of the controller is inevitable with the digital feedback controller only. To compensate the admittance component, the duty feed-forward method was discussed. Both the simulation and the experimental results for the 1 kW single-phase bridgeless PFC converter prototype support the analyses in the paper.

#### REFERENCES

- B. Singh, S. Singh, A. Chandra, and K. Al-Haddad, "Comprehensive study of single-phase AC-DC power factor corrected converters with high-frequency isolation," *IEEE. Trans. Ind. Informat.*, Vol. 7, No. 4, pp. 540-556, Nov. 2011.

- [2] F. J. Azcondo, C. Branas, R. Casanueva, and S. Bracho, "Power-mode-controlled power-factor corrector for electronic ballast," *IEEE Trans. Ind. Electron.*, Vol. 52, No. 1, pp. 56-65, Feb. 2005.

- [3] Y.-C. Li and C.-L. Chen, "A novel single-stage high-power-factor AC-to-DC LED driving circuit with leakage inductance energy recycling," *IEEE Trans. Ind. Electron.*, Vol. 59, No. 2, pp. 793-802, Feb. 2012.

- [4] J.-M. Wang, S.-T. Wu, Y. Jiang, and H.-J. Chiu, "A Dual-Mode Controller for the Boost PFC Converter," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 1, pp. 369-372, Jan. 2011.

- [5] B. A. Mather and D. Maksimovic, "A simple digital power-factor correction rectifier controller," *IEEE Trans. Power Electron.*, Vol. 26, No. 1, pp. 9-19, Jan. 2011.

- [6] Y. Jang and M. M. Jovanovic, "A bridgeless PFC boost rectifier with optimized magnetic utilization," *IEEE Trans. Power Electron.*, Vol. 24, No. 1, pp. 85-93, Jan. 2009.

- [7] P. Kong, S. Wang, and F. C. Lee, "Common mode EMI noise suppression for bridgeless PFC converters," *IEEE Trans. Power Electron.*, Vol. 23, No. 1, pp. 291-297, Jan. 2008.

- [8] F. Musavi, W. Eberle, and W. G. Dunford, "A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers," *IEEE Trans. Ind. Applicat.*, Vol. 47, No. 4, pp. 1833-1843, Jul./Aug. 2011.

- [9] A. Prodic, "Compensator design and stability assessment for fast voltage loops of power factor correction rectifiers," *IEEE Trans. Power Electron.*, Vol. 22, No. 5, pp. 1719-1730, Sep. 2007.

- [10] N. Genc and I. Iskender, "DSP-based current sharing of average current controlled two-cell interleaved boost power factor converter," *IET Power Electron.*, Vol. 4, No. 9, pp. 1015-1022, 2011.

- [11] W. Zhang, G. Feng, Y. –F. Liu, and B. Wu, "a digital power factor correction (PFC) control strategy optimized for DSP", *IEEE Trans. Power Electron.*, Vol. 19, No. 6, pp. 1474-1485, Nov. 2004.

- [12] S. F. Lim and A. M. Khambadkone, "A simple digital DCM control scheme for boost PFC operating in both CCM and DCM," *IEEE Trans. Ind. Applicant.*, Vol. 47, No. 4, pp. 1802-1812, Jul./Aug. 2011.

- [13] F.-Z. Chen and D. Maksimovic, "Digital control for improved efficiency and reduced harmonic distortion over wide load range in boost PFC rectifiers," *IEEE Trans. Power Electron.*, Vol. 25, No. 10, pp. 2683-2692, Oct. 2010.

- [14] K. D. Gusseme, D. M. Van de Sype, A. P. Van. den Bossche, and J. A. Melkebeek, "Input-Current Distortion of CCM Boost PFC Converters Operated in DCM," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 2, pp.858-865, Apr. 2007.

- [15] K. D. Gusseme, D. M. Van de Sype, A. P. Van den Bossche, and J. A. Melkebeek, "Digitally controlled boost power-factor-correction converters operating in both continuous and discontinuous conduction mode," *IEEE Trans. Ind. Electron.*, Vol. 52, No. 1, pp. 88-97, Feb. 2005.

- [16] J. Zou, X. Ma, and C. Du, "Asymmetrical oscillations in digitally controlled power-factor-correction boost converters," *IEEE Trans. Circuits Syst. II, Exp. Briefs.*, Vol. 56, No. 3, pp. 230-234, Mar. 2009.

- [17] D. M. Van de Sype, K. D. Gusseme, A. P. Van den Bossche, and J. A. Melkebeek, "Duty-ratio feedforward for digitally controlled boost PFC converters," *IEEE Trans. Ind. Electron.*, Vol. 52, No. 1, pp. 108-115, Feb. 2005.

- [18] M. Chen and J. Sun, "Feedforward current control of boost single-phase PFC converters," *IEEE Trans. Power Electron.*, Vol. 21, No. 2, pp. 338-345, Mar. 2006.

- [19] S.-Y. Park, C.-L. Chen, J.-S. Lai, and S.-R. Moon, "Admittance compensation in current loop control for a grid-tie LCL fuel cell inverter," *IEEE Trans. Power Electron.*, Vol. 23, No. 4, pp. 1716-1723, Jul. 2008.

- [20] S.-Y. Park, C.-L. Chen, and J.-S. Lai, "A wide-range active and reactive power flow controller for a solid oxide fuel cell power conditioning system," *IEEE Trans. Power Electron.*, Vol. 23, No. 6, pp. 2703-2709, Nov. 2008.

- [21] K. P. Louganski and J. –S. Lai, "Current phase lead compensation in single-phase PFC boost converters with a reduced switching frequency to line frequency ratio," *IEEE Trans. Power Electron.*, Vol. 22, No. 1, pp. 113-119, Jan. 2007.

- [22] D. M. Van de Sype, K. D. Gusseme, F. M. L. L. De Belie, A. Van den Bossche, and J. A. Melkebeek, "Small-signal z-domain analysis of digitally controlled converters," *IEEE Trans. Power Electron.*, Vol. 21, No. 2, pp. 470-478, Mar. 2006.

- [23] P. Mattavelli, G. Spiazzi, and P. Tenti, "Predictive digital control of power factor preregulators with input voltage estimation using disturbance observers," *IEEE Trans. Power Electron.*, Vol. 20, No. 1, pp. 140-147, Jan. 2005.

- [24] Y. Cho, H. Miwa, and J.-S. Lai, "A digital single-loop control of multiphase DC-dc converter for fuel cell powered truck auxiliary power unit," *IEEE 8<sup>th</sup> ICPE-ECCE ASIA*, pp. 2261-2266, 2011.

- [25] H. D. Venable, "The K factor: a new mathematical tool for stability analysis and systems," Available: http://icwic.cn/icwic/data/pdf/cd/cd057/Switching,%20DC -DC%20Regulator,%20Controller/1184.pdf.

Younghoon Cho was born in Seoul, Korea, in 1980. He received the B.S. degree in electrical engineering from Konkuk University, Seoul, Korea, in 2002, the M.S. degree in electrical engineering from Seoul National University, Seoul, in 2004, and the Ph. D. degree from Virginia Polytechnic Institute and State University, Blacksburg,

VA, USA, in 2012. From 2004 to 2009, he was an Assistant Research Engineer at Hyundai MOBIS R&D Center, Yongin, Korea. Since 2013, he has been with the Department of Electrical Engineering, Konkuk University, Seoul, Korea. His current research interests include digital control techniques for power electronic converters in vehicle and grid applications, multilevel converters, and high performance motor drives.

Hyungsoo Mok received the B.S., M.S. and Ph.D. degrees in electrical engineering from Seoul National University, Korea, in 1986, 1988, and 1992, respectively. He was with the Department of Control and Instrumentation Engineering at Seoul National Polytechnic University from 1993 to 1997. Since 1997, he has been with the

Department of Electrical Engineering at Konkuk University. His teaching and research interests include electric machines, electric machine drive systems, and power electronic control for industrial and power systems.

**Jih-Sheng Lai** received M.S. and Ph.D. degrees in electrical engineering from the University of Tennessee, Knoxville, in 1985 and 1989 respectively. From 1980 to 1983, he was the Head of the Electrical Engineering Department of the Ming-Chi Institute of Technology, Taipei, Taiwan, where he initiated a power electronics program and

received a grant from his college and a fellowship from the National Science Council to study abroad. In 1986, he became a staff member at the University of Tennessee, where he taught control systems and energy conversion courses. In 1989, he joined the Electric Power Research Institute (EPRI) Power Electronics Applications Center (PEAC), where he managed EPRI-sponsored power electronics research projects. From 1993, he worked with the Oak Ridge National Laboratory as the Power Electronics Lead Scientist, where he initiated a high power electronics program and developed several novel high power converters including multilevel converters and His work brought him several soft-switching inverters. distinctive awards including a Technical Achievement Award in Lockheed Martin Award Night, three IEEE IAS Conference Paper Awards, Best Paper Awards from IECON-97, IPEC-05, and PCC-07. In 1996, he joined Virginia Polytechnic Institute and State University. His student teams won three awards from future energy challenge competitions and the first place award from TI Enginous Prize Analog Design Competition. He is currently a professor and the Director of the Future Energy Electronics Center. His main research areas are in high efficiency power electronics conversions for high power and energy applications. He has published more than 240 technical papers and 2 books and received 20 U.S. patents. Dr. Lai chaired the 2000 IEEE Workshop on Computers in Power Electronics (COMPEL 2000), 2001 IEEE/DOE Future Energy Challenge, and 2005 IEEE Applied Power Electronics Conference and Exposition (APEC 2005).