**JPE 14-2-2**

http://dx.doi.org/10.6113/JPE.2014.14.2.217 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Driving Scheme Using a Single Control Signal for a ZVT Voltage Driven Synchronous Buck Converter

Amin Asghari<sup>†</sup> and Hosein Farzanehfard<sup>\*</sup>

<sup>†\*</sup>Department of Electrical and Computer Engineering, Isfahan University of Technology, Isfahan, Iran

### **Abstract**

This paper deals with the optimization of the driving techniques for the ZVT synchronous buck converter proposed in [1]. Two new gate drive circuits are proposed to allow this converter to operate by only one control signal as a 12V voltage regulator module (VRM). Voltage-driven method is applied for the synchronous rectifier. In addition, the control signal drives the main and auxiliary switches by one driving circuit. Both of the circuits are supplied by the input voltage. As a result, no supply voltage is required. This approach decreases both the complexity and cost in converter hardware implementation and is suitable for practical applications. In addition, the proposed SR driving scheme can also be used for many high frequency resonant converters and some high frequency discontinuous current mode PWM circuits. The ZVT synchronous buck converter with new gate drive circuits is analyzed and the presented experimental results confirm the theoretical analysis.

**Key words:** Synchronous buck converter, Voltage-driven synchronous rectifier (VDSR), Voltage regulator module (VRM), Zero-voltage switching (ZVS)

## I. INTRODUCTION

Due to the improvements in semiconductor technology, more transistors are being placed on integrated circuits (ICs). To decrease the power consumption of an IC, its operating voltage must be reduced. The voltages of today ICs are 5, 3.3, and 1.2 V or lower. On the other hand, increasing the bus voltage reduces the conduction losses. For this reason, the bus voltage has been changed from 5 V to 12 V in several applications such as portable equipment, telecommunication equipment, data processing units, etc. Therefore, efficiently converting the 12 V input to the IC voltages by high quality voltage regulator modules (VRMs) is very challenging.

A synchronous buck converter is usually the first choice for such a VRM. In this topology, the synchronous rectifier (SR) decreases the conduction losses of the main diode. However, the reverse recovery time of the SR body diode considerably increases both the switching losses and the electro-magnetic interference (EMI). By applying zero-voltage transition (ZVT) techniques to a synchronous buck converter, a time gap would be created between the conduction time of the main switch and

the diode. Thus, the losses related to the reverse recovery time of the SR body diode are significantly reduced [1]. In addition, like other Soft switching methods, ZVT techniques decrease the switching losses and EMI. Among the many ZVT techniques, the studies in [1]-[6] have applied the ZVT and synchronous rectification techniques simultaneously. The ZVT synchronous buck converter proposed in [1] is shown in Fig. 1(a). In this technique, the zero-voltage switching (ZVS) condition is provided for the main and SR switches without any additional current or voltage stress. In addition, it provides the zero-current-switching (ZCS) condition for the auxiliary switch. Another distinctive advantage of this technique is that when the auxiliary switch current reaches the output inductor current, the SR does not turn off and remains on for a short interval. Therefore, the direction of the SR current is reversed and additional energy is stored in the auxiliary inductor. This additional energy can completely discharge the snubber capacitor even if the output voltage is less than V<sub>in</sub>/2. In addition, this would eliminate the reverse recovery loss of the SR body diode. These advantages are created by a simple auxiliary circuit. However, this converter needs a complicated circuit to generate 3 isolated gate pulses for the main switch, the auxiliary switch and the SR. This complicated circuit can decrease reliability and increase the converter cost. Therefore, the driving scheme for the switches is a technical challenge of this new approach. Ref. [1] applies the external driven method

Manuscript received Dec. 16, 2012; accepted Nov. 12, 2013 Recommended for publication by Associate Editor Joung-Hu Park.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: a.asghari@ec.iut.ac.ir

<sup>\*</sup>Dept. of Electrical and Computer Eng., Isfahan University of Technology, Iran

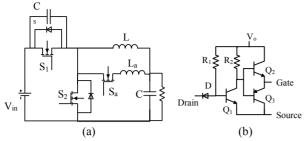

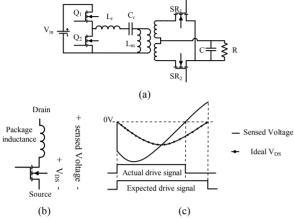

Fig. 1. (a) ZVT synchronous buck converter proposed in [1], (b) SR driving circuit proposed in [26]( $V_0$  is the converter output voltage).

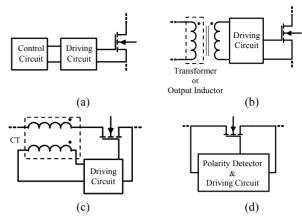

to drive the SR. Besides this method, there are two other methods to control the synchronous rectifiers namely self-driven and control-driven methods. In the external-driven method, which is shown in Fig. 2(a), a control unit utilizes the switching signal to generate the SR driving signal. Thus, a more complicated circuit is required. In addition, in many applications, the SR driving signal needs to be isolated. Therefore, a transformer-isolated or an opt-isolated gate driver is required. As a result, this technique may adversely affect reliability while the system implementation is more complicated and costly.

The self-driven method, which is shown in Fig. 2(b), utilizes the voltage across the output inductor or the secondary side of the transformer to drive the SR [7]-[14]. This converter is non-isolated and does not have a transformer. In addition, when the SR is on, the voltage on the output inductor is clamped to  $V_{\rm O}$  and cannot be utilized to turn off the SR. Thus, the implementation of a self-driven technique for this converter is very difficult.

The control-driven method develops the driving signal by monitoring the SR current [15]-[27]. This technique can be applied to this type of converter since the SR current is reversed before the SR is turned off. The control-driven method is divided into current-driven and voltage-driven methods. In the current-driven method, which is shown in Fig. 2(c), the current transformer (CT) is placed in series with the MOSFET to sense the SR current [15]-[24]. However, the CT has a large size and its winding adds resistance to the current path. Therefore, the current driven-method sacrifices power density and efficiency especially in low-voltage high-current applications.

The voltage-driven method, which is shown in Fig. 2(d), monitors the voltage developed across the SR drain-source and generates the driving signal according to the detected polarity [25]-[27]. This voltage is the result of the SR current flowing through its on resistance. In [26], a new circuit based on the voltage-driven method is proposed for a flyback converter as illustrated in Fig. 1(b).

This circuit detects the SR voltage polarity by a series combination of the diode and BJT base-emitter junction that

Fig. 2. Methods to control the synchronous rectifier. (a) External-driven method, (b) self-driven method, (c) current-driven method, (d) voltage-driven method.

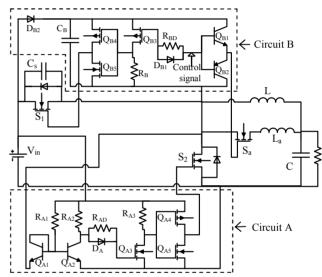

Fig. 3. ZVT synchronous buck converter with proposed driving circuits.

are placed across the SR drain-source terminals. Then, the generated signal is applied to the SR gate through a push-pull buffer. However, this circuit switches the SR as soon as the drain-source voltage polarity changes. In addition, the polarity of a voltage with such a low magnitude may not be detected.

As it can be observed from Fig. 1(a), the main and auxiliary switches of the Ref. [1] converter have a common source. Therefore, this paper proposes a driving circuit for these switches by using only one signal. In addition, this paper presents a new, improved voltage-driven synchronous rectification scheme for this converter. In addition, no extra DC voltage source is required to provide the supply voltage for the gate drivers. This is due to the fact that for low input voltage applications, especially 12V VRM applications, the variations of the input voltage are limited and thus, the input voltage can be used to supply the gate drive circuits. By incorporating these drivers, the converter driving scheme is

improved without any change in its main operational intervals or capabilities. Therefore, the converter driving complexity is reduced and the reliability is improved while the previously mentioned advantages of the converter in [1] are maintained. On the other hand, in the proposed synchronous rectification scheme, the SR can remain on when the drain-source voltage polarity changes. Consequently, it is very suitable for converters where the SR must not turn off as soon as its voltage polarity becomes positive, like some ZVT synchronous buck converters, some high-frequency resonant converters and some high-frequency discontinuous current mode PWM circuits.

This paper is composed of six sections. After this introduction, the ZVT synchronous buck converter with the proposed gate drive circuits is presented and analyzed in section II. Section III focuses on the design considerations. Other applications of the proposed voltage-driven synchronous rectifier are provided in section IV. In section V, experimental results from the implemented prototype are provided to confirm the validity of the theoretical analysis. Finally, some conclusions are presented in section VI.

# II. CIRCUIT DESCRIPTION AND PRINCIPLE OF OPERATION

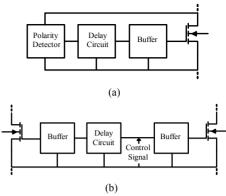

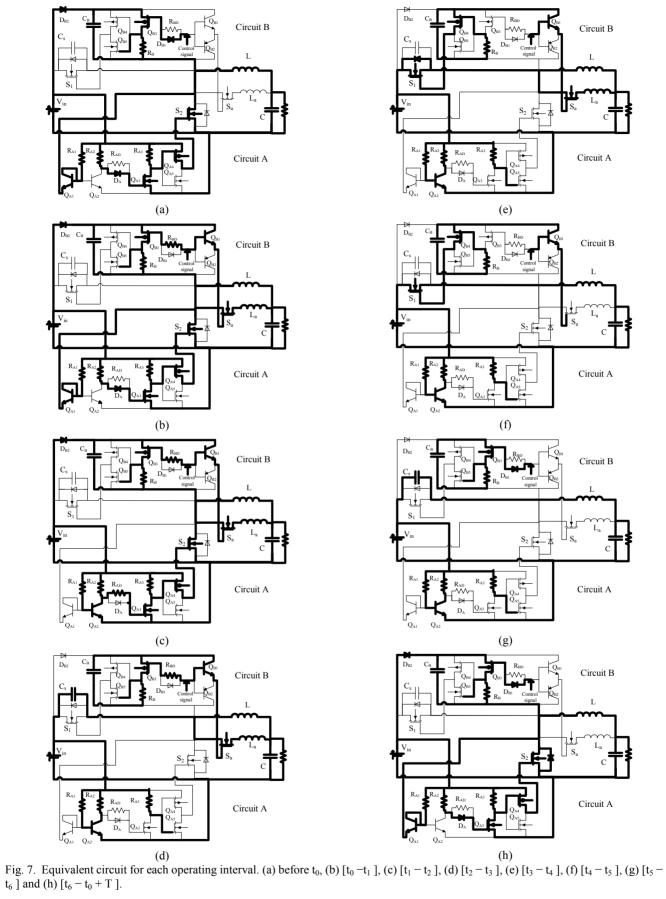

The ZVT synchronous buck converter together with its gate drive circuits is shown in Fig. 3. Circuit A which is based on the voltage-driven method, drives the SR. The main and auxiliary switches are driven by circuit B. The rest of the circuit is the converter which is composed of the main switch  $S_1$ , the SR switch  $S_2$ , and the output filter L & C. The snubber capacitor C<sub>s</sub>, the unidirectional auxiliary switch S<sub>a</sub> and the auxiliary inductor L<sub>a</sub> are the auxiliary components to provide the ZVS condition. In circuit A, transistors Q<sub>A1</sub> & Q<sub>A2</sub> detect the SR voltage polarity. These transistors with resistors R<sub>A1</sub> & R<sub>A2</sub> generate proper signals with respect to the SR voltage polarity. Resistor R<sub>AD</sub> provides the turn off signal to the SR with delay. Diode D<sub>A</sub> bypasses R<sub>AD</sub> when the turn on signal is generated. Finally, transistors QA3, QA4, and QA5 along with resistor R<sub>A3</sub> operate as a buffer to amplify and sharpen the edge of the gate signals. The reference voltage for this circuit is the input voltage. In circuit B, transistors Q<sub>B1</sub> & Q<sub>B2</sub> operate as a push-pull topology to drive the auxiliary switch. In addition, transistors Q<sub>B3</sub>, Q<sub>B4</sub>, and Q<sub>B5</sub> along with resistor R<sub>B</sub> operate as a buffer to drive the main switch. Resistor R<sub>BD</sub> provides the main switch turn on with delay. Diode  $D_{B1}$  circumvents  $R_{BD}$ when the control signal becomes low. Finally, diode D<sub>B2</sub> and capacitor C<sub>B</sub> form the required bootstrap to make the supply voltage. Operation block diagrams of the proposed driving circuits are illustrated in Fig. 4. To simplify the converter analysis, the following assumptions are made: 1) all semiconductor devices are ideal; 2) the input voltage is

Fig. 4. Operation block diagrams. (a) circuit A, (b) circuit B.

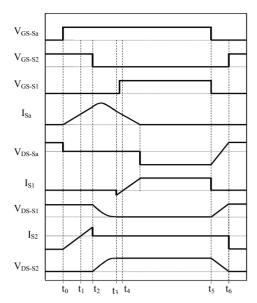

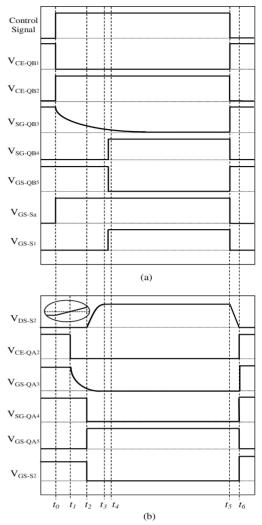

constant and equal to  $V_{in}$  in a switching cycle; and 3) the inductor L current and capacitor C voltage are constant and equal to  $I_o$  &  $V_o$ , respectively. Fig. 5 and Fig. 6 illustrate the essential theoretical waveforms. Fig. 7 presents the equivalent circuit of each operating interval. The circuit operation is explained as follows.

Before the first interval [Before  $t_0$ ]: It is assumed that the SR is on and all of the other semiconductor devices in the main circuit are off. In circuit A, transistors  $Q_{A1}$ ,  $Q_{A3}$ , and  $Q_{A4}$  are on, while  $Q_{A2}$  and  $Q_{A5}$  are off. In addition, in circuit B, transistors  $Q_{B2}$ ,  $Q_{B3}$ , and  $Q_{B5}$  are on, while  $Q_{B1}$  and  $Q_{B4}$  are off.

Interval 1 [ $t_0 - t_I$ ]: This interval starts when the control signal becomes high and it turns on  $Q_{B1}$  and turns off  $Q_{B2}$ . Transistor  $Q_{B1}$  delivers current to the gate-source capacitor of  $S_a$ , and turns this switch on at  $t_0$ . At the same time, the gate-source capacitor of  $Q_{B3}$  begins to discharge through  $R_{BD}$  and thus,  $Q_{B3}$  turns off with a delay. When  $S_a$  turns on, the output voltage is placed across  $L_a$ . Accordingly, the  $L_a$  current increases from zero to  $I_o$  and the  $S_2$  current decreases from  $I_o$  to zero linearly. Due to  $L_a$ ,  $S_a$  is turned on under zero-current switching.

Interval 2  $[t_1 - t_2]$ : At the beginning of this interval, the  $L_a$  current becomes more than  $I_o$ . Thus, the  $S_2$  current is reversed and the drain-source voltage of  $S_2$  becomes positive. In this condition, the base-emitter voltage of  $Q_{A2}$  is higher than  $Q_{A1}$ , and  $Q_{A2}$  is turned on by the current flowing through resistor  $R_{A1}$ . As a result, the input capacitor of  $Q_{A3}$  begins to discharge through  $R_{AD}$  and  $Q_{A2}$ . By proper design of  $R_{AD}$  (as discussed in the next section),  $Q_{A3}$  is turned off at the end of this interval. Therefore,  $S_2$  is on and like the previous interval, the  $L_a$  current linearly increases from  $I_o$ . The maximum value of the  $L_a$  current at the end of this interval is defined as  $I_1$ . In this interval, additional energy is stored in  $L_a$  to make sure it would discharge the snubber capacitor.

Interval 3  $[t_2-t_3]$ : This interval starts by turning  $Q_{A3}$  off at  $t_2$ . The input capacitor of  $Q_{A4}$  is discharged through  $R_{A3}$ , and  $Q_{A4}$  is turned off. At the same time, the supply voltage charges the input capacitor of  $Q_{A5}$  through  $R_{A3}$  and turns on this

Fig. 5. Theoretical waveforms of the synchronous buck converter.

transistor. Finally, the input capacitor of the SR switch  $(S_2)$  is discharged trough  $Q_{A5}$ , and  $S_2$  is turned off. By turning  $S_2$  off, a resonance begins between  $L_a$  and  $C_s$ . By proper design of  $L_a$ ,  $C_s$  and  $R_{AD}$  as discussed in the next section,  $C_s$  is completely discharged and the  $L_a$  current is slightly greater than  $I_o$  at the end of this interval. Due to  $C_s$ ,  $S_2$  is turned off under zero-voltage switching (ZVS).

Interval 4  $[t_3 - t_4]$ : The body diode of  $S_1$  turns on at  $t_3$  and the voltage of  $C_s$  remains zero. The voltage difference between the input and output voltages is placed across  $L_a$  and its current decreases linearly to  $I_o$ . By proper design of  $R_{BD}$ , transistor  $Q_{B3}$  is turned off in this interval. Then, the input capacitor of  $Q_{B5}$  is discharged through  $R_B$ , and  $Q_{B5}$  is turned off. At the same time, the input capacitor of  $Q_{B4}$  is charged by the supply voltage through  $R_B$ , and  $Q_{B4}$  is turned on. Finally, the supply voltage charges the input capacitor of the main switch  $S_1$  through  $Q_{B4}$ , and turns on this transistor.  $S_1$  is turned on under ZVS because the  $L_a$  current is greater than  $I_o$  and thus, the body diode of  $S_1$  is on during this interval.

Interval 5  $[t_4-t_5]$ : In this interval, the main switch  $S_1$  is on. As a result, the  $L_a$  current continues to decrease from  $I_o$  to zero. Then, the unidirectional auxiliary switch  $S_a$  does not allow the  $L_a$  current to become negative, and it stops conduction. Thus, the converter behaves like a regular buck converter.

Interval 6  $[t_5 - t_6]$ : This interval starts when the control signal becomes low. This signal turns off  $Q_{B1}$  and turns on  $Q_{B2}$ . Transistor  $Q_{B2}$  discharges the input capacitor of the auxiliary switch  $S_a$ , and turns off this switch. On the other hand, diode  $D_{B1}$  bypasses  $R_{BD}$ , and  $Q_{B3}$  is turned on immediately. As a result,  $Q_{B4}$  is turned off,  $Q_{B5}$  is turned on and consequently, the main switch  $S_1$  is turned off. Then,  $I_o$  flows through  $C_s$  and charges it until the  $S_1$  and  $S_2$  voltages reach  $V_{in}$  and zero, respectively. Due to  $C_s$ ,  $S_1$  is turned off under the ZVS

Fig. 6. Theoretical waveforms of the gate drive circuits. (a) circuit B waveforms and, (b) circuit A waveforms.

condition.

Interval 7  $[t_6-t_0+T]$ : The body diode of  $S_2$  starts to conduct and the drain-source voltage of  $S_2$  becomes negative. In this condition, the base-emitter voltage of  $Q_{A1}$  is higher than that of  $Q_{A2}$ , and  $Q_{A2}$  is turned off. Therefore,  $Q_{A3}$  is turned on immediately through  $D_A$ . Also,  $Q_{A4}$  is turned on,  $Q_{A5}$  is turned off and as a result, SR switch  $S_2$  is turned on under ZVS.

# III. DESIGN GUIDELINES

The design of the ZVT synchronous buck converter is discussed in [1]. In this converter, during the second interval, the  $L_a$  current increases from  $I_o$  to its maximum value at the end of this interval defined as  $I_1$ .

Therefore, additional energy proportional to  $(I_1-I_o)$  is stored in  $L_a$ . This additional energy is used to discharge  $C_s$  when the output voltage is less than  $V_{in}/2$ . The required value for  $I_1$  to completely discharge  $C_s$ , and the durations of the various operating intervals are also discussed in [1]. Consequently,

only the gate drive circuits need to be designed. Resistor  $R_{\text{AD}}$  is used to reduce the gate-source voltage of  $Q_{\text{A3}}$  as follows:

$$V_{gs_{-}Q_{A3}} = V_{in}e^{\frac{-t-t_1}{\tau_A}}.$$

(1)

where

$$\tau_A = R_{AD} \times C_{gs} \,_{O_{43}}. \tag{2}$$

$Q_{A3}$  must be on during Interval 2 and it should turn off at the end of this interval. For this purpose,  $V_{gs\_QA3}$  must be greater than its threshold voltage in Interval 2 and it must reach  $V_{th\_QA3}$  at  $t_2$ . Thus,  $\tau_A$  is obtained from (1) as:

$$\tau_{A} = -\frac{t_{2} - t_{1}}{\ln \frac{V_{th_{-}Q_{A3}}}{V_{in}}}.$$

(3)

Finally, from (2) and (3), R<sub>AD</sub> can be calculated as follows:

$$R_{AD} = -\frac{t_2 - t_1}{C_{gs_{-Q_{A3}}} \times \ln \frac{V_{th_{-Q_{A3}}}}{V_{in}}}.$$

(4)

R<sub>BD</sub> discharges the input capacitor of Q<sub>B3</sub> as follows:

$$V_{gs_{-}Q_{B3}} = -V_{in}e^{\frac{t-t_0}{\tau_B}}. (5)$$

where

$$\tau_B = R_{BD} \times C_{gs} O_{Bs}. \tag{6}$$

Therefore, Q<sub>B3</sub> turns off with following delay:

$$t_D = -\tau_B \ln \frac{V_{th\_Q_{B3}}}{V_{in}}. (7)$$

$Q_{\rm B3}$  must be turned off during Interval 4 when the body diode of  $S_1$  conducts. Thus,  $t_D$  should be greater than  $t_3$ - $t_0$  and smaller than  $t_4$ - $t_0$ . Finally, from (6) and (7),  $R_{\rm BD}$  can be calculated as follows:

$$R_{BD} = -\frac{t_D}{C_{gs_{-}Q_{B3}} \times \ln \frac{V_{th_{-}Q_{B3}}}{V_{th_{-}}}}.$$

(8)

where

$$t_3 - t_0 < t_D < t_4 - t_0. (9)$$

$R_{\rm AD}$  and  $R_{\rm BD}$  are designed for the nominal load with  $t_D = t_3 - t_0$ . By applying these resistors, at the nominal load, the main switch is turned on at the beginning of the fourth interval. At light loads, the duration of the first interval reduces and the fourth interval begins early. Thus, the main switch is turned on during the fourth interval. As a result, ZVS is guaranteed for the main switch at turn on and only the conduction time of its body diode is increased at light loads.

Power MOSFETs usually have large gate-source

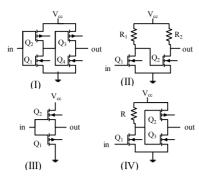

capacitances. In particular, Power MOSFETs with low on resistances have high die sizes. As a result, they have high gate-source capacitances. In addition, some MOSFETs may be paralleled to reduce the on resistance. Therefore, the gate drive circuits need buffers to drive these switches. The auxiliary switch  $S_a$  turns on/off as soon as the control signal becomes high/low. Therefore, a push-pull circuit is a proper buffer for the control signal. However, the main switch  $S_1$  and the SR switch  $S_2$ , must be switched with a delay.

As discussed in the previous section, with the RC circuits, the initial signals rise/fall times increase and their values reach the threshold levels with desired delays. In this situation, if push-pull buffers are used, the drive signals have slow rise/fall times (they are soft). This can decrease efficiency because the on resistance of a power MOSFET has a reverse ratio with respect to its gate-source voltage. Thus, the on resistance is high during the interval that the gate-source voltage is between the threshold and maximum values.

Among the various buffers illustrated in Fig. 8, the theoretical analysis and simulation results show that the proper buffer for this situation is buffer IV. In buffer I, if the initial signal is soft, both of the transistors in the first stage would be on during the interval that the gate voltage is between V<sub>th</sub> and (12-V<sub>th</sub>). Buffer II drives the power switch through a resistor. Thus, the drive signal is soft in the rising edge. Buffer III, which is a push-pull with MOSFET, may incompletely charge or discharge the gate-source capacitor of the power switch. However, in buffer IV, when Q<sub>1</sub> turns off, the input capacitors of Q2 and Q3 discharge and charge through R at a high speed because of their low values. When Q1 turns on, the input capacitors of Q2 and Q3 immediately charge and discharge through Q<sub>1</sub>. In addition, the gate-source capacitor of the power switch, charges and discharges through the second stage transistors, immediately. Consequently, this buffer can almost generate a pulse from the initial soft signal.

In circuit B, the input voltage cannot be directly used as the supply voltage because the main switch source voltage is float. For this reason, as can be observed in Fig. 3, diode  $D_{\rm B2}$  and capacitor  $C_{\rm B}$  provide the supply voltage from the input voltage with the bootstrap technique. The first stage of circuit A must detect the polarity of a very small voltage. For this purpose, a BJT similar to  $Q_{\rm A2}$  is used as a diode connected transistor in order to place two similar base-emitter junctions across each other.

Normally, control ICs have an under voltage lock out (UVLO) threshold. By using a control IC with an UVLO threshold of about 8 volts, the converter would not have problem in the transition time. During the transition time, until the input voltage is below the operational voltage of the control IC, it remains off. Thus, no control signal is generated. In this situation, the proposed driver circuit does not provide gate pulses for the main and auxiliary switches. Thus, the

Fig. 8. Various buffers to drive a MOSFET.

Fig. 9. (a) LLC resonant converter with SR, (b) simple schematic of the SR package, and (c) deviation in the sensed voltage due to SR package inductance.

converter stays off with no output voltage. In addition, by implementing the soft start technique, the overshoot problem is solved.

# IV. OTHER APPLICATIONS FOR THE PROPOSED SR DRIVING SCHEME

The proposed SR driver is also proper for many high-frequency resonant converters and some high-frequency discontinuous current mode PWM circuits such as LLC resonant converter and DCM synchronous buck converter. As it is mentioned in the introduction, in voltage-driven method, the drain-source voltage of the SR is used to drive it. The existence of parasitic inductances in MOSFET packages is inevitable. As it can be observed from Fig. 9(b), the developed voltage across the MOSFET drain-source terminals is actually the sum of the MOSFET resistive voltage (which is the ideal V<sub>DS</sub>) and the package inductive voltage. Fig. 9(a) shows an LLC resonant converter with SR. In this converter, the SR current with a positive slope goes to zero and then the SR turns off. In this condition, as shown in Fig. 9(c), the sensed voltage of the SR terminals deviates greatly from the ideal V<sub>DS</sub> and it goes to zero early (due to the positive voltage of the package inductor). As it can be observed, if this sensed voltage is directly used to drive the SR, the drive signal would be much shorter than the expected signal. As a result, the SR would be turned off much earlier than the expected time and its body diode would start conducting [27]. This phenomenon becomes noticeable at high frequencies. A similar condition exists for DCM synchronous buck converter. However, the proposed SR driver can produce a delay in the SR turn off signal. Thus, with the proposed driver, the SR used in any of these converters remains on after the sensed voltage becomes positive and is driven at almost ideal condition.

# V. EXPERIMENTAL RESULTS

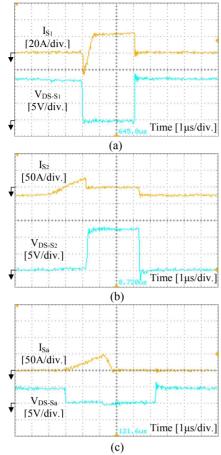

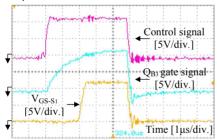

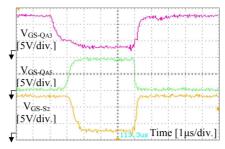

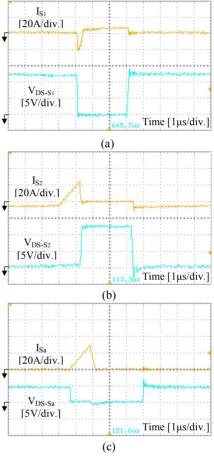

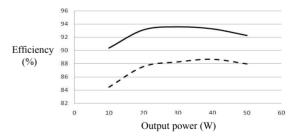

A 12V input and 3.3V/15A output laboratory prototype is designed and implemented to operate at 100kHz switching frequency. In the main circuit of the converter, IRF1404 with  $R_{ds(op)}$ =4m $\Omega$  is used for the main and SR switches. In addition, an IRF1404 with a S30SC4M diode create the unidirectional auxiliary switch  $S_a$ . Finally, the values of L,  $L_a$  and  $C_s$  are 8.2μH, 0.12μH and 15nF, respectively. In the gate drive circuits, BS170 and BS250 are used for all of the N-Channel and P-Channel MOSFETs, respectively. All of the NPN BJTs are BC107 and the PNP BJT is a BC177. 1N4148 is used for all of the diodes. Based on the design procedure explained in the previous section, the values of  $R_{\text{AD}}$  and  $R_{\text{BD}}$  are calculated as  $17k\Omega$  and  $7.2k\Omega$ , respectively. A  $1\mu F$  capacitor is used for  $C_B$ . In addition,  $1k\Omega$  resistors are used for  $R_{A1}$ ,  $R_{A2}$ ,  $R_{A3}$  and  $R_{B2}$ . The experimental waveforms of the main circuit are presented in Fig. 10. These waveforms show that the synchronous buck converter operates properly when the proposed drivers are incorporated. Fig. 10(a) shows that the main switch is turned on under the ZVS condition while the duty cycle is equal to 0.3 (<0.5). Therefore, it can be concluded that the drivers have provided proper delays to turn off and turn on the SR and the main switches, respectively. The experimental signals of circuit B are illustrated in Fig. 11. In this figure, the signals are shown with respect to the main switch source. When the control signal becomes high, the gate signal of Q<sub>B3</sub> begins to increase with slow rise time. In this condition, the source-gate voltage of Q<sub>B3</sub> decreases slowly, and Q<sub>B3</sub> turns off with a delay. Therefore, R<sub>BD</sub> has provided the required delay. In addition, as it can be observed, the gate-source voltage of the main switch becomes high with a delay in comparison to the control signal. Note that this signal has an acceptable rise time. The experimental waveforms of circuit A are shown in Fig. 12. As it can be seen, the gate-source voltage of QA3 has a slow fall time and reaches the threshold voltage with a delay. After this delay, the gate-source voltage of QA5 becomes high and the gate-source voltage of the SR becomes low with a sharp fall time. As a result, the proposed SR driver has provided a gate signal with the desired delay and fall time. Experimental results under light load (20% of the nominal load) are provided in Fig. 13. In addition, the converter efficiency curve is shown in Fig. 14.

Fig. 10. (Top waveform) current and (bottom waveform) voltage of (a)  $S_1$  (vertical scale is 5V/div or 20A/div). (b)  $S_2$  (vertical scale is 5V/div or 50A/div). (c)  $S_a$  (vertical scale is 5V/div or 50A/div). Time scale is  $1\mu s$ /div.

Fig. 11. Experimental waveforms of circuit B. (Top) control signal, (middle) gate signal of  $Q_{\rm B3}$ , (bottom) gate signal of the main switch (the signals are shown with respect to the main switch source).

## VI. CONCLUSIONS

Two new gate drive circuits are presented in this paper. One circuit drives the synchronous rectifier with the voltage-driven method. The other circuit drives both the main and auxiliary switches by the control signal. Both gate drive circuits are supplied by the input voltage. The ZVT synchronous buck converter along with the introduced gate drive circuits is analyzed. Various operating modes are discussed and the design guidelines are explained. Finally, a prototype converter is implemented to verify the validity of the theoretical analysis.

Fig. 12. Experimental waveforms of circuit A. (Top) gate-source voltage of  $Q_{A3}$ , (middle) gate-source voltage of  $Q_{A5}$ , (bottom) gate-source voltage of the SR switch.

Fig. 13. Experimental waveforms under light load (20% of the nominal load). Current waveform (Top) and voltage waveform (bottom) of (a)  $S_1$  (b)  $S_2$  (c)  $S_a$ .

Fig. 14. Efficiency comparison of the proposed circuit (continuous line) and a hard-switching synchronous buck converter (broken line) versus output power.

### REFERENCES

- [1] E. Adib and H. Farzanehfard, "Zero-voltage-transition pwm converters with synchronous rectifier," *IEEE Trans. Power Electron.*, Vol. 25, No. 1, pp. 105-110, Jan. 2010.

- [2] H. Mao, O. Abdel Rahman, and I. Batarseh, "Zero-voltage-switching DC-DC converters with synchronous rectifiers," *IEEE Trans. Power Electron.*, Vol. 23, No. 1, pp. 369-378, Jan. 2008.

- [3] S. Pattnaik, A. K. Panda, and K. Mahapatra, "Efficiency improvement of synchronous buck converter by passive auxiliary circuit," *IEEE Trans. Ind. Appl.*, Vol. 46, No. 6, pp. 2511-2517, Nov./Dec. 2010.

- [4] H.-L. Do, "Zero-voltage-switching synchronous buck converter with a coupled inductor," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 8, pp. 3440-3447, Aug. 2011.

- [5] N. Z. Yahaya, K. M. Begam, and M. Awan, "Experimental analysis of a new zero-voltage switching synchronous rectifier buck converter," *IET Power Electron.*, Vol. 4, No. 7, pp. 793-798, Aug. 2011.

[6] H. T. Yang, J. T. Liao, and X. Y. Cheng, "A novel dual

- [6] H. T. Yang, J. T. Liao, and X. Y. Cheng, "A novel dual resonant tank for ZVT DC-DC converters with synchronous rectifier," in *Proc. IEEE Trondheim PowerTech.*, 2011.

- [7] P. Alou, J. A. Cobos, O. García, R. Prieto, and J. Uceda, "A new driving scheme for synchronous rectifiers: Single winding self-driven synchronous rectification," *IEEE Trans. Power Electron.*, Vol. 16, No. 6, pp. 803-811, Nov. 2001.

- [8] A. Fernández, J. Sebastián, M. M. Hernando, P. J. Villegas, and J. García, "New self-driven synchronous rectification system for converters with a symmetrically driven transformer," *IEEE Trans. Ind. Appl.*, Vol. 41, No. 5, pp. 1307–1315, Sep./Oct. 2005.

- [9] A. Fernández, J. Sebastián, M. M. Hernando, and D.G. Lamar, "Self-driven synchronous rectification system for converters with symmetrically driven transformer based on the use of the output inductor," in *Proc. APEC '06.*, pp. 763-769, 2006.

- [10] T. Qian, W. Song, and B. Lehman, "Self-driven synchronous rectification scheme without undesired gate-voltage discharge for DC-DC converters with symmetrically driven transformers," *IEEE Trans. Power Electron.*, Vol. 23, No. 1, pp. 506-510, Jan. 2008.

- [11] A. Fernández, D. G. Lamar, M. Rodríguez, M. M. Hernando, J. Sebastián, and M. Arias, "Self-driven synchronous rectification system with input voltage tracking for converters with a symmetrically driven transformer," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 5, pp. 1440-1445, May 2009.

- [12] S. Ye, W. Eberle, and Y-Fei Liu, "A novel non-isolated full bridge topology for VRM applications," *IEEE Trans. Power Electron.*, Vol. 23, No. 1, pp. 427-437, Jan. 2008.

- [13] K. Jin, M. Xu, Y. Sun, D. Sterk, and F. C. Lee, "Evaluation of self-driven schemes for a 12-V self-driven voltage regulator," *IEEE Trans. Power Electron.*, Vol. 24, No. 10, pp. 2314-2322, Oct. 2009.

- [14] Z. Zhang, E. Meyer, Y-Fei Liu, and P. C. Sen, "A nonisolated zvs self-driven current tripler topology for low-voltage and high-current applications," *IEEE Trans. Power Electron.*, Vol. 26, No. 2, pp. 512-522, Feb. 2011.

- [15] E. Sakai and K. Harada, "A new synchronous rectifier using bipolar transistor driven by current transformer," in *Proc. INTELEC'92.*, pp. 424-429, 1992.

- [16] B. Acker, C. R. Sullivan, and S. R. Sanders, "Current-Controlled Synchronous Rectification," in *Proc. APEC*, pp.185-191, 1994.

- [17] X. Xie, J. C. Pong Liu, F. N. K. Poon, and M. H. Pong, "A novel high frequency current-driven synchronous rectifier applicable to most switching topologies," *IEEE Trans. Power Electron.*, Vol. 16, No. 5, pp. 635-648, Sep. 2001.

- [18] X. Xie, J. Zhang, C. Zhao, and Z. Qian, "An improved current-driven method for synchronous flyback AC/DC converters," in *Proc. INTELEC '06*, 2006.

- [19] C. Zhao, X. Wu, P. Meng, and Z. Qian, "Optimum design consideration and implementation of a novel synchronous rectified soft-switched phase-shift full-bridge converter for low-output-voltage high-output-current applications," *IEEE Trans. Power Electron.*, Vol. 24, No. 2, pp. 388-397, Feb. 2009

- [20] S. Shao, X. Wu, M. Chen, and F. Z. Peng, "Design considerations of a self-biased current driven SR in DCM flyback DC/DC converter," in *Proc. ECCE* 2010, pp. 242-248, 2010.

- [21] X. Guo, W. Lin, and X. Wu, "A novel current driven method for center-tapped synchronous rectifier," in *Proc. International Power Electron. Conf.* pp. 449-454, 2010.

- [22] X. Huang, J. Wang, J. Zhang, and Z. Qian, "A hybrid driving scheme for full-bridge synchronous rectified LLC resonant DC/DC converter," in *Proc. APEC 2011*, pp. 579-584, 2011.

- [23] G. K. Y. Ho, R. Yu, and B. M. H. Pong, "Current driven synchronous rectifier with saturable current transformer and dynamice gate voltage control for LLC resonant converter," in *Proc. APEC 2012*, pp. 2345-2351, 2012.

- [24] J. Zhang, J. Liao, J. Wang, and Z. Qian, "A current-driving synchronous rectifier for an LLC resonant converter with voltage-doubler rectifier structure," *IEEE Trans. Power Electron.*, Vol. 27, No. 4, pp. 1894-1904, Apr. 2012.

- [25] G.-Y. Jeong, "High efficiency asymmetrical half-bridge flyback converter using a new voltage-driven synchronous rectifier," *IET Power Electron.*, Vol. 3, No. 1, pp. 18-32, 2008.

- [26] J.-J. Lee, J.-M. Kwon, E.-H. Kim, W.-Y. Choi, and B.-H. Kwon, "Single-stage single-switch PFC flyback converter using a synchronous rectifier," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 3, pp. 1352-1365, Mar. 2008.

- [27] D. Fu, Y. Liu, F. C. Lee, and M. Xu, "A novel driving scheme for synchronous rectifiers in LLC resonant converters," *IEEE Trans. Power Electron.*, Vol. 24, No. 5, pp. 1321-1329, May 2009.

Amin Asghari was born in 1982. He received the B.S. degree in Electrical Engineering from the Shiraz University, Shiraz, Iran, in 2005, and the M.S. degree in Electrical Engineering from the Amirkabir University of Technology, Tehran, Iran, in 2008. He is currently working toward the Ph.D. degree in Electrical Engineering at the

Isfahan University of Technology, Isfahan, Iran. His current research interests include synchronous rectification techniques, and soft switching techniques in dc-dc converters.

Hosein Farzanehfard (M'08) was born in Isfahan, Iran, in 1961. He received the B.S. and M.S. degrees in Electrical Engineering from the University of Missouri, Columbia, USA, in 1983 and 1985, respectively, and the Ph.D. degree from the Virginia Polytechnic Institute and State University, Blacksburg, USA, in 1992. Since 1993, he has been a

faculty member with the Department of Electrical and Computer Engineering, Isfahan University of Technology, Isfahan, Iran, where he is currently an Associate Professor. His current research interests include high-frequency soft switching converters, pulse power applications, power factor correction, active power filters, and high-frequency electronic ballasts. He is the author or coauthor of more than 70 technical papers published in journals and conference proceedings.