**JPE 14-5-13**

http://dx.doi.org/10.6113/JPE.2014.14.5.918 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Extended Boost Single-phase qZ-Source Inverter for Photovoltaic Systems

Hyun-Hak Shin\*, Honnyong Cha<sup>†</sup>, Hongjoon Kim\*\*, and Heung-Geun Kim\*\*

\*\*School of Energy Engineering, Kyungpook National University, Daegu, Korea

\*\*School of Electrical Engineering, Kyungpook National University, Daegu, Korea

#### **Abstract**

This study presents an extended boost single-phase qZ-source DC-AC inverter for a single-phase photovoltaic system. Unlike the previously proposed single-phase qZ-source and semi-qZ-source inverters that achieve the same output voltage as that of the traditional voltage-fed full-bridge inverter, the proposed inverter can obtain higher output than input voltage. The proposed inverter also shares a common ground between DC input voltage and AC output voltage. Thus, possible ground leakage current problem in non-isolated grid-tied inverters can be eliminated with the proposed inverter. A 120 W prototype inverter is built and tested to verify the performance of the proposed inverter.

Key words: Buck-boost, Full-bridge inverter, Semi-qZ-source inverter, Single-phase qZ-source inverter

#### I. Introduction

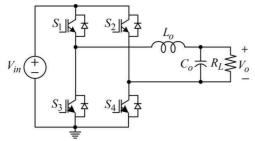

An increasing demand for low-cost, single-phase DC-AC inverters has been observed in recent years in many applications, such as in photovoltaic (PV) systems, fuel cells, and battery-powered systems. The conventional approach to address this demand is to use a full-bridge (FB) inverter (Fig. 1).

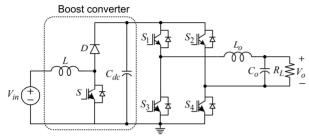

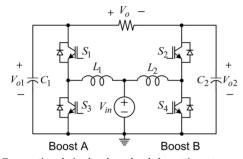

However, a conventional single-phase FB inverter requires four switches, and inverter output voltage is only equal to or smaller than input voltage. If input voltage is low, then the conventional approach requires a DC-DC boost (Fig. 2) at the front end to maintain sufficient DC-link voltage in the inverter. However, two-stage power conversion decreases system efficiency and increases system cost and volume. Another approach (Fig. 3) involves using a buck-boost inverter with two identical DC-DC converters that share the same DC input voltage while the load is across two outputs, namely,  $V_{o1}$  and  $V_{o2}$  [1]-[4].

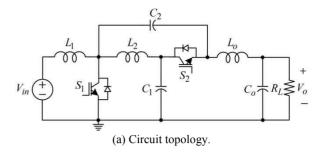

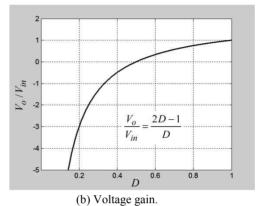

Although this topology can generate higher output voltage than input voltage, one of its distinct drawbacks is that the Many circuit topologies have been introduced recently to overcome the aforementioned problems; some of these topologies are based on a Z-source or qZ-source inverter structure [8]-[14]. Fig. 4(a) shows a single-phase current-fed (CF) qZ-source inverter, and Fig. 4(b) shows the voltage gain curve of this inverter [12].

By defining D as the duty cycle of switch  $S_2$ , the voltage gain of the single-phase CF qZ-source inverter is expressed as follows [12]:

$$\frac{V_o}{V_{in}} = \frac{2D - 1}{D} \,. \tag{1}$$

A voltage gain similar to the one shown in Fig. 4(b) can also be achieved by the recently developed semi-qZ-source inverter (Fig. 5) [13]. The voltage gain of this inverter is the same as that in Fig. 4 but requires less component counts.

voltage stress of the switching device is too high and the circuit requires four switches to boost voltage [1]. Therefore, high efficiency cannot be expected with this topology. An additional problem with the conventional FB inverter in Fig. 1 and the buck–boost inverter in Fig. 3 is that the input and output have different grounds. For transformer-less, grid-tied PV inverter topologies, a large leakage current may occur if the input DC-source (PV) and grid do not share the same ground; this condition can cause safety and electromagnetic interference problems [5]-[7].

Manuscript received Jan. 27, 2014; accepted Jul. 7, 2014

Recommended for publication by Associate Editor Tae-Woong Kim.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: chahonny@knu.ac.kr

Tel: +82-53-950-8972, Fax: +82-53-950-8979, Kyungpook Nat'l Univ. \*School of Energy Engineering, Kyungpook National University, Korea

<sup>\*\*</sup>School of Electrical Engineering, Kyungpook National University, Korea

Fig. 1. Conventional single-phase FB inverter.

Fig. 2. Conventional two-stage single-phase FB inverter.

Fig. 3. Conventional single-phase buck-boost inverter.

Unlike the topologies shown in Figs. 1 to 3, the CF qZ-source and semi-qZ-source inverters shown in Figs. 4 and 5 share common grounds. Therefore, these circuits can eliminate the possible leakage current problem [13].

However, Fig. 4(b) shows that the voltage gains of the single-phase CF qZ-source and semi-qZ-source inverters are limited to 1. The output voltage cannot be greater than the input voltage such as in the conventional FB inverter shown in Fig. 1. Thus, these inverters still present a problem when they are used in low input voltage applications such as in micro-inverters.

An extended boost single-phase qZ-source inverter is introduced in this study to overcome the limited voltage gain of the single-phase CF qZ-source and semi-qZ-source inverters. The proposed inverter also shares a common ground between DC input and AC output voltage.

# II. PRINCIPLE OPERATION OF THE PROPOSED INVERTER

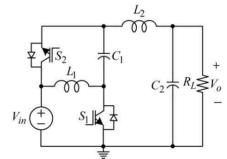

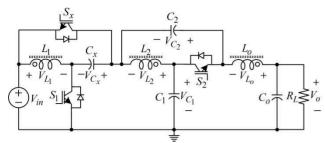

Fig. 6 shows the proposed extended boost single-phase qZ-source inverter topology. Unlike the topology shown in

Fig. 4. Single-phase CF qZ-source inverter [12].

Fig. 5. Semi-qZ-source inverter [13].

Fig. 6. Proposed extended boost single-phase qZ-source inverter.

Fig. 4, the proposed inverter has an additional switch  $(S_x)$  and capacitor  $(C_x)$  to provide extended boost function [15, 16]. Similar to Fig. 4, switches  $S_1$  and  $S_2$  are turned on and off complementarily. The additional switch  $S_x$  is synchronized to  $S_1$ . The detailed mode operation of the proposed inverter is as follows.

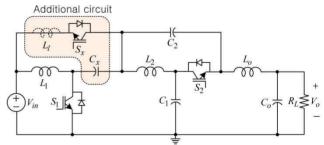

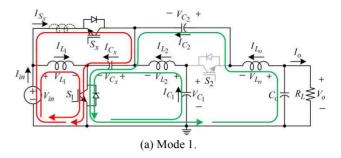

### A. Mode 1

Switches  $S_1$  and  $S_x$  are turned on and  $S_2$  is turned off in mode 1. Fig. 7(a) shows the operation in mode 1. Given that  $S_1$  and  $S_x$  are turned on, capacitor  $C_x$  is charged to  $V_{in}$ . The possible voltage difference between  $V_{in}$  and  $C_x$  being charged/discharged depends on output power. When voltage difference is high, the current in the charging path is also high [15]-[17]. Excessive current can damage switching devices and decrease the lifetime of components. A small current-limiting inductor ( $L_l$ ) is connected in series with  $S_x$  to limit current in this work. Notably, although the added current-limiting inductor induces a voltage spike across  $S_1$  and  $S_x$ , such spike is low because the inductance value used is small (approximately 500 nH).

The voltage and current relations in this mode are shown in Fig. 7. The effect of  $L_l$  on voltage gain is neglected because the  $L_l$  value is small based on the analysis. Thus,

$$V_{C_{\mathbf{r}}} = V_{in} \,, \tag{2}$$

$$V_{L_1} = V_{in} \,, \tag{3}$$

$$V_{L_2} = V_{C_1} - V_{in} , (4)$$

$$V_{L_o} = V_o - V_{in} - V_{C_2} , (5)$$

$$I_{in} = I_{L_1} + I_{S_n} \,, \tag{6}$$

$$I_{S_1} = I_{L_1} + I_{C_Y} \,, \tag{7}$$

$$I_{C_{\nu}} = I_{S_{\nu}} + I_{C_{2}} + I_{L_{2}}, \tag{8}$$

$$I_{C_1} = I_{L_2} ,$$

(9)

$$I_{C_2} = I_{L_0} . {10}$$

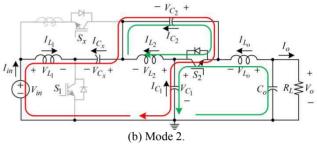

### B. Mode 2

Switches  $S_1$  and  $S_x$  are turned off and  $S_2$  is turned on in mode 2. Capacitor  $C_x$  is discharged by inductor  $L_1$  current. The voltage and current relations in this mode are as follows:

$$V_{L_1} = V_{in} + V_{C_x} + V_{C_2} - V_{C_1}, (11)$$

$$V_{L_2} = V_{C_2} \,, \tag{12}$$

$$V_{L_0} = V_o - V_{C_1} \,, \tag{13}$$

$$I_{S_2} = I_{L_1} + I_{L_2} + I_{L_0} , (14)$$

$$I_{C_x} = -I_{in} = -I_{L_1}, (15)$$

$$I_{C_1} = -(I_{L_1} + I_{L_0}), (16)$$

$$I_{C_2} = -(I_{L_1} + I_{L_2}). (17)$$

Fig. 7. Operating principle of the proposed inverter.

From the volt-sec (or flux) balance condition on  $L_1$  ,  $L_2$  , and  $L_o$  , the following voltage equations are derived:

$$V_{C_1} = 2V_{in} , (18)$$

$$V_{C_2} = \left(\frac{D-1}{D}\right) V_{in}, \tag{19}$$

$$\frac{V_o}{V_{in}} = \frac{3D - 1}{D}$$

, (20)

,where D is the duty cycle of switch  $S_2$ .

Similarly, current equations are derived from the current-sec (or charge) balance condition on  $C_x$ ,  $C_1$ , and  $C_2$  as follows:

$$I_{L_2} = I_{L_o} = -I_o ,$$

(21)

$$I_{L_1} = \left(\frac{2D-1}{D}\right) I_o, \qquad (22)$$

$$I_{S_x} = \left(\frac{1}{1-D}\right) I_o. \tag{23}$$

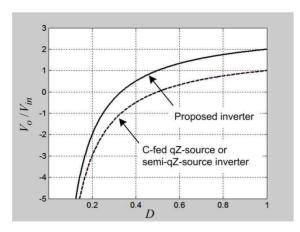

Fig. 8 shows the voltage gain curve of the proposed inverter and its gain is compared with that in Fig. 4. The proposed inverter can achieve twice the voltage gain of the existing CF qZ-source and semi-qZ-source inverters.

## III. MODULATION SCHEME OF THE PROPOSED INVERTER

The modulation scheme of the proposed inverter is the same as those of the conventional CF qZ-source and

Fig. 8. Voltage gain comparison.

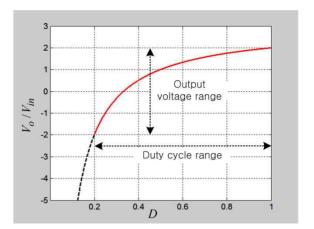

semi-qZ-source inverters. The voltage gain curve of the proposed inverter is redrawn in Fig. 9 to determine the duty cycle and output voltage range of the proposed inverter.

Assuming that the inverter output voltage is represented by (24), then the modulation index (M) of the inverter is expressed as follows:

$$V_o = V_m \sin \omega t \,, \tag{24}$$

$$M = \frac{V_m}{V_{in}} \,. \tag{25}$$

By substituting (24) and (25) into (20), the following formula is obtained:

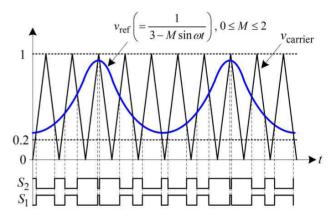

$$D = \frac{1}{3 - M \sin \omega t}, (0 \le M \le 2). \tag{26}$$

Fig. 9 shows that the proposed inverter can generate an output voltage up to twice the input voltage. Thus, the maximum modulation index is 2. When M = 2, the duty cycle of the proposed inverter ranges from 0.2 to 1.0 as shown in Fig. 9

Fig. 10 illustrates the modulation scheme of the proposed inverter. It shows that the reference ( $v_{ref}$ ) and carrier ( $v_{carrier}$ ) signals are compared to generate the required gate signals.

## IV. DEVICE STRESS AND PASSIVE COMPONENT DESIGN

The mode analysis of the proposed inverter shows that the voltages across all three inductors ( $L_1$ ,  $L_2$ , and  $L_o$ ) of the proposed inverter are the same in each corresponding operation mode. The results are summarized in Table I. The three inductor voltages in mode 1 are equal to  $V_{in}$ , whereas the three inductor voltages in mode 2 are equal to  $V_{C_2}$ . Therefore, the three inductors can be coupled into one

Fig. 9. Duty cycle range and achievable output voltage range of the proposed inverter.

Fig. 10. Gate signal generation of the proposed inverter.

$\begin{array}{c} \text{TABLE I} \\ \text{Voltages across} \ \ \textit{L}_{\!1} \ , \ \textit{L}_{\!2} \ , \text{and} \ \ \textit{L}_{\!0} \end{array}$

|           | Mode 1                                     | Mode 2                                           |  |

|-----------|--------------------------------------------|--------------------------------------------------|--|

|           | $(S_1, S_x = \text{on}, S_2 = \text{off})$ | $(S_1, S_x = \text{off}, S_2 = \text{on})$       |  |

| $V_{L_1}$ | $V_{in}$                                   | $V_{in} + V_{C_x} + V_{C_2} - V_{C_1} = V_{C_2}$ |  |

| $V_{L_2}$ | $V_{C_1} - V_{in} = V_{in}$                | $V_{C_2}$                                        |  |

| $V_{L_o}$ | $V_o - (V_{C_2} + V_{in}) = V_{in}$        | $V_o - V_{C_1} = V_{C_2}$                        |  |

inductor core [18]. This procedure significantly reduces inductor volume, and consequently, total inverter size. Fig. 11 shows the circuit of the proposed inverter that uses a coupled inductor with the inductor polarity dots marked.

From (18) and (19), as well as the defined labels in Fig. 11, switch voltage stresses are derived as follows:

$$V_{S_1} = V_{S_2} = V_{S_x} = V_{C_1} - (V_{C_2} + V_{in}) = \frac{V_{in}}{D}.$$

(27)

From (21) and (22), as well as the defined labels in Fig. 11, switch current stresses are also derived as follows:

Fig. 11. Proposed inverter that uses a coupled inductor for  $L_1$ ,  $L_2$ , and  $L_o$ .

TABLE II Comparison of Switch Stresses

|       | CF qZ-source inverter (Fig. 4) |                  | Proposed inverter  |                                        |

|-------|--------------------------------|------------------|--------------------|----------------------------------------|

|       | Voltage                        | Current          | Voltage            | Current                                |

|       | stress                         | stress           | stress             | stress                                 |

| $S_1$ | $\underline{V_{in}}$           | $-\frac{I_o}{D}$ |                    | $-\left(\frac{1-2D}{D(1-D)}\right)I_o$ |

| $S_2$ | D                              | $\frac{I_o}{D}$  | $\frac{V_{in}}{D}$ | $\frac{I_o}{D}$                        |

| $S_x$ | Not applicable                 |                  |                    | $\left(\frac{1}{1-D}\right)I_o$        |

$$I_{S_1} = I_{L_1} + I_{S_x} + I_{L_2} + I_{L_o} = \left(\frac{2D - 1}{D(1 - D)}\right) I_o,$$

(28)

$$I_{S_2} = -(I_{L_1} + I_{L_2} + I_{L_o}) = \frac{I_o}{D}.$$

(29)

Table II shows the switch stresses of the proposed inverter and their comparison with those of the single-phase CF qZ-source inverter. The minus (–) sign in the current stress indicates that  $I_o$  is a negative quantity at the corresponding duty cycle.

### V. EXPERIMENT RESULTS

A 120 W prototype inverter is built and tested to verify the performance of the proposed inverter. Table III shows the detailed electrical specifications of the proposed prototype inverter.

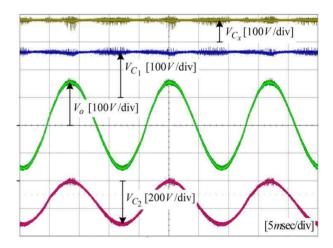

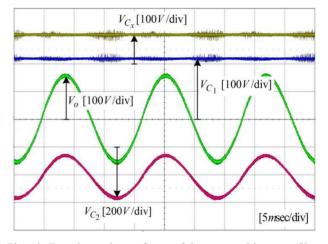

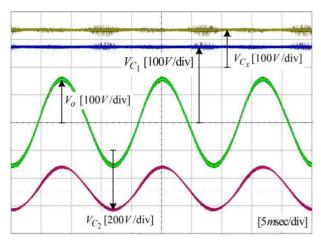

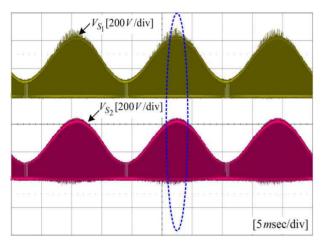

Figs. 12, 13, and 14 show the experimental waveforms of the proposed inverter when  $V_{in}=80$ , 105, and 135 V, respectively. The output voltage and output power are 110 Vrms and 120 W, respectively. The voltages across  $C_x$  and  $C_1$  are nearly equal to  $V_{in}$  and  $2V_{in}$ , respectively.

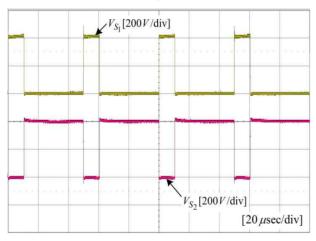

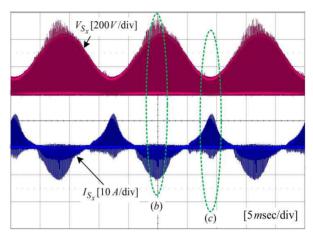

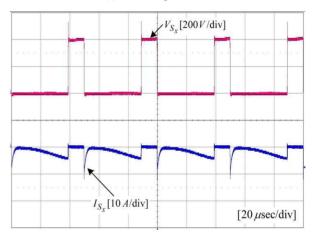

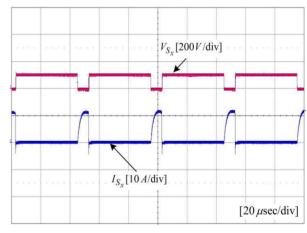

Fig. 15(a) shows the experimental waveform of switches  $S_1$  and  $S_2$  when  $V_{in} = 80$  V, M = 1.95, and  $P_o = 120$  W. Fig. 15(b) shows the zoomed-in switching waveforms of Fig. 15(a). Fig. 16(a) shows the experimental waveforms of the voltage and current of switch  $S_{\chi}$ . Figs. 16(b) and 16(c) show

TABLE III

ELECTRICAL SPECIFICATIONS OF THE PROPOSED INVERTER

| Outp             | ut power        | 120 W                       |  |

|------------------|-----------------|-----------------------------|--|

| Output vol       | tage/frequency  | 110 Vrms/60 Hz              |  |

| Switchin         | ng frequency    | 20 kHz                      |  |

| $S_1$ ,          | $S_2, S_x$      | FGH20N60SFD<br>(600 V/20 A) |  |

|                  | Core            | PQ5050 ferrite core         |  |

| Coupled inductor | Number of turns | 55 turns                    |  |

|                  | $L_1, L_2, L_o$ | 680 μH                      |  |

| (                | $C_x, C_1$      | 30 μF                       |  |

| C                | $C_2, C_o$      | 8.8 μF                      |  |

Fig. 12. Experimental waveforms of the proposed inverter ( $V_{in} = 80 \text{ V}, M = 1.95$ ).

Fig. 13. Experimental waveforms of the proposed inverter ( $V_{in} = 105 \text{ V}$ , M = 1.48).

the zoomed-in waveforms of the dotted boxes in Fig. 16(a).

An inductor with approximately 500 nH is used in the experiment to limit switch  $S_x$  current. A slight voltage

Fig. 14. Experimental waveforms of the proposed inverter ( $V_{in} = 135 \text{ V}$ , M = 1.15).

(a) Switching waveforms.

(b) Zoomed-in waveforms of (a).

Fig. 15. Switching waveforms ( $V_{in} = 80 \text{ V}, M = 1.95$ ).

spike is observed in switch  $S_x$  because of this inductance, but the spike is low and the current is limited. The current directions of  $S_x$  depend on output voltage polarity.

(a) Switching waveforms.

(b) Zoomed-in waveforms of (a).

(c) Zoomed-in waveforms of (a).

Fig. 16. Waveforms of switch  $S_x$ .

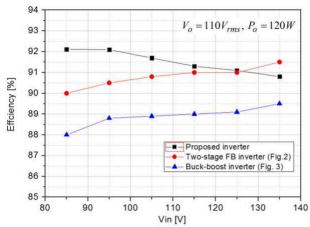

Figs. 16(b) and 16(c) show the waveforms when the output voltage has a negative and positive polarity, respectively. Fig. 17 shows the measured efficiency curve of the proposed inverter when input voltage varies. The efficiency of the proposed inverter is compared with those of the inverters shown in Figs. 2 and 3. Similar switching devices are used

Fig. 17. Measured efficiency of the proposed inverter and its comparison with the inverter shown in Figs. 2 and 3.

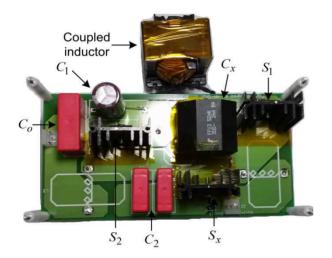

Fig. 18. Photograph of the proposed inverter .

for the comparison.

Fig. 18 shows a photograph of the proposed inverter.

### VI. CONCLUSIONS

This study presents an extended boost single-phase qZ-source inverter based on the existing CF single-phase qZ-source inverter. With an additional circuit that consists of  $S_x$  and  $C_x$ , the output voltage of the proposed inverter can be extended up to twice the input voltage.

Similar to the existing single-phase qZ-source and semi-qZ-source inverters, the proposed inverter shares a common ground between DC input voltage and AC output voltage. Therefore, the possible ground leakage current problem, particularly in transformer-less grid-tied PV applications, can be eliminated with the proposed inverter.

A 120 W prototype inverter is built and successfully tested to verify the operation principle of the proposed inverter. With its extended boost property and doubly grounded features, the proposed inverter is promising for applications

with low input voltage sources such as batteries, PV cells, and fuel cells.

#### ACKNOWLEDGMENT

This research was partly supported by the MSIP(Ministry of Science, ICT & Future Planning), Korea, under the C-ITRC(Convergence Information Technology Research Center) support program (NIPA-2014-H0401-14-1004) supervised by the NIPA(National IT Industry Promotion Agency) and partly supported by Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education, Science and Technology(2012R1A1A1044058).

### REFERENCES

- R. O. Caceres and I. Barbi, "A boost DC-AC converter: analysis, design, and experimentation," *IEEE Trans. Power Electron.*, Vol. 14, No. 1, pp. 134-141, Jan. 1999.

- [2] C. M. Wang, "A novel single-stage full-bridge buck-boost inverter," *IEEE Trans. Power Electron.*, Vol. 19, No. 1, pp. 150-159, Jan. 2004.

- [3] M. Jang, M. Ciobotaru, and V. G. Agelidis, "A single-stage fuel cell energy system based on a buck-boost inverter with a backup energy storage unit," *IEEE Trans. Power Electron.*, Vol. 27, No. 6, pp. 2825-2834, Jun. 2012.

- [4] P. Sanchis, A. Ursaea, E. Gubia, and L. Marroyo, "Boost DC-AC inverter: A new control strategy," *IEEE Trans. Power Electron.*, Vol. 20, No. 2, pp. 343-353, Mar. 2005.

- [5] J. M. A. Myrzik and M. Calais, "String and module integrated inverters for single-phase grid connected photovoltaic systems – A review," in 2003 IEEE Bologna PowerTech Conf. Proc., Vol. 2, 2003.

- [6] O. Lopez, F. D. Freijedo, A. G. Yepes, P. Fernandez-Comesaa, J. Malvar, R. Teodorescu, and J. Doval-Gandoy, "Eliminating ground current in a transformerless photovoltaic application," *IEEE Trans. Energy Convers.*, Vol. 25, No. 1, pp. 140-147, Mar. 2010.

- [7] S. Araujo, P. Zacharias, and R. Mallwitz, "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 9, pp. 3118-3128, Sep. 2010.

- [8] F. Z. Peng, "Z-source inverter," *IEEE Trans. Ind. Appl.*, Vol. 39, No. 2, pp. 504-510, Mar./Apr. 2003.

- [9] J. Anderson and F. Z. Peng, "Four quasi-Z-Source inverters," in *Power Electronics Specialists Conference (PESC 2008)* IEEE, pp. 2743-2749, 2008.

- [10] S. Yang, F. Z. Peng, Q. Lei, R. Inoshita, and Z. Qian, "Current-fed quasi-z-source inverter with voltage buck-boost and regeneration capability," *IEEE Trans. Ind. Appl.*, Vol. 47, No. 2, pp. 882-892, Mar./Apr. 2011.

- [11] W. Qian, F. Z. Peng, and H. Cha, "Trans-Z-source inverters," *IEEE Trans. Power Electron.*, Vol. 26, No. 12, pp. 3453-3463, Dec. 2011.

- [12] Y. Tang, S. Xie, C. Zhang, "Single-phase Z-Source inverter," IEEE Trans. Power Electron., Vol. 26, No. 12, pp. 3869-3873, Dec. 2011.

- [13] D. Cao, S. Jiang, X. Yu, and F. Z. Peng, "Low-cost semi-Z-source inverter for single-phase photovoltaic

- systems," *IEEE Trans. Power Electron.*, Vol. 26, No. 12, pp. 3514-3523, Dec. 2011.

- [14] F. Z. Peng, "Z-source networks for power conversion," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, pp. 1258-1265, 2008.

- [15] F. L. Luo and H. Ye, "Positive output super-lift converters," *IEEE Trans. Power Electron.*, Vol. 18, No. 1, pp. 105-113, Jan. 2003.

- [16] F. L. Luo and H. Ye, "Positive output multiple-lift push-pull switched-capacitor luo-converters," *IEEE Trans. Ind. Electron.*, Vol. 51, No. 3, pp. 594-602, Jun. 2004.

- [17] M. Shen, F. Z. Peng, and L. M. Tolbert, "Multilevel DC–DC power conversion system with multiple DC sources," *IEEE Trans. Power Electron.*, Vol. 23, No. 1, pp. 420-426, Jan. 2008.

- [18] A. F. Witulski, "Introduction to modeling of transformers and coupled inductors," *IEEE Trans. Power Electron.*, Vol. 10, No. 3, pp. 349-357, May 1995.

Hyun-Hak Shin received his B.S. in Electrical Engineering from Youngnam University, Korea in 2012. He is currently working toward his M.S. at the School of Energy Engineering, Kyungpook National University. His current research interests include pulse-width modulation AC-AC converters. Z-source inverters, and

solid-state transformers (SST).

Honnyong Cha received his B.S. and M.S. in Electronics Engineering from Kyungpook National University, Daegu, Korea in 1999 and 2001, respectively, and his Ph.D. in Electrical Engineering from Michigan State University, East Lansing, MI, USA in 2009. He was a research engineer at Power System Technology (PSTEK) Company, An-san,

Korea from 2001 to 2003. He also worked as a senior researcher at the Korea Electrotechnology Research Institute (KERI), Changwon, Korea from 2010 to 2011. He joined Kyungpook National University, Daegu, Korea in 2011 as an assistant professor at the School of Energy Engineering. His main research interests include high power DC–DC converters, DC–AC inverters, Z-source inverters, and power conversion for electric vehicles and wind-power generation.

Hongjoon Kim received his B.S. in Electrical and Electronics Engineering from Kyungpook National University, Daegu, Korea in 1997, M.S. in Electrical Engineering from the University of Southern California, CA, USA in 1999, and Ph.D. in Electrical Engineering from the University of Wisconsin, Madison, WI, USA in 2006. He

worked at the city college of the City University of New York as an assistant professor from 2006 to 2011. He joined the Electrical Engineering Department of Kyungpook National University in 2011 and currently works as an associate professor. His research focuses on high-frequency electronic devices and systems. He is also interested in solid-state device physics for high-power and high-frequency applications.

Heung-Geun Kim was born in Korea in 1956. He received his B.S., M.S., and Ph.D. in Electrical Engineering from Seoul National University in 1980, 1982, and 1988, respectively. He has been with the Department of Electrical Engineering at Kyungpook National University since 1984, where he is currently a full professor and the

director of the Microgrid Research Center. He was a visiting scholar at the Department of Electrical and Computer Engineering of the University of Wisconsin-Madison, USA from 1990 to 1991 and at the Department of Electrical Engineering of the Michigan State University, USA from 2006 to 2007. His current research interests are AC machine control, PV power generation, and micro-grid systems.