**JPE 14-6-13**

http://dx.doi.org/10.6113/JPE.2014.14.6.1197

ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Carrier Phase-Shift PWM to Reduce Common-Mode Voltage for Three-Level T-Type NPC Inverters

Tuyen D. Nguyen\*, Dzung Quoc Phan\*, Dat Ngoc Dao\*, and Hong-Hee Lee

\*Faculty of Electrical and Electronics Eng., HoChiMinh City University of Technology, VNU-HCM, HoChiMinh

City, Vietnam

†School of Electrical Eng., University of Ulsan, Ulsan, Korea

#### **Abstract**

Common-mode voltage (CMV) causes overvoltage stress to winding insulation and damages AC motors. CMV with high dv/dt causes leakage currents, which create noise problems for equipment installed near the converter. This study proposes a new pulse-width modulation (PWM) strategy for three-level T-type NPC inverters. This strategy substantially eliminates CMV. The principle for selecting suitable triangle carrier signals for the three-level T-type NPC is described. The proposed method can mitigate the peak value of CMV by 50% compared with the phase disposition pulse-width modulation method. Furthermore, the proposed method exhibits better harmonic spectrum and lower root mean square value for the CMV than those of the reduced-CMV method on the basis of the phase opposition disposition PWM scheme with modulation index higher than 0.5. The proposed modulation can easily be implemented using software without any additional hardware modifications. Both simulation and experimental results demonstrate that the proposed carrier phase-shift PWM method has good output waveform performance and reduces CMV.

**Key words:** Common-mode voltage, Phase disposition PWM, Phase opposition disposition PWM, Sinusoidal PWM, Three-level inverter, T-type NPC

### I. INTRODUCTION

Interest in multilevel topologies has been increasing because of the many possibilities in power electronics applications, such as in the military, e-vehicles, and renewable energy. Multilevel converters synthesize output voltage from more than two voltage levels. Therefore, the spectrum of the output signal is significantly improved when compared with that of classical two-level converters. The multilevel inverter reduces voltage constraints on switches while lowering the total harmonic distortion (THD) of output voltages [1]-[5]. The main drawback of multilevel converters

is the number of switches, which increases with the number of levels.

Multilevel inverters are classified into three groups: neutral-point-clamped (NPC) inverters, floating point capacitor inverters, and cascade H-bridge inverters, with NPC inverters being the most widely used [6]-[8]. Recently, T-type NPC (T-NPC) inverters have been proposed as more efficient alternatives to traditional NPC inverters [9], [10]. Until recently, multilevel NPC inverters have received considerable attention for commercial applications, and many researchers have focused on improving the output performance while reducing the power losses, the number of power switches, and the common-mode voltage (CMV) of such converters [11]-[15]. Previous research deemed CMV reduction to be important in extending the lifetime of electrical equipment.

CMV attributed to high-speed pulse-width modulation (PWM) in power converters introduces numerous problems

Manuscript received May 29, 2014; accepted Oct. 8, 2014

Recommended for publication by Associate Editor Kyo-Beum Lee.

†Corresponding Author: hhlee@mail.ulsan.ac.kr

Tel: +82-52-259-2187, Fax: +82-52-259-2186, University of Ulsan

\*Faculty of Electrical and Electronics Eng., HoChiMinh City University of Technology, VNU-HCM, Vietnam

within an electrical system. CMW is the main source of early motor-winding failure, bearing deterioration, and wide-band electromagnetic interference. Reducing the CMV within the power converter is important. Two main solutions used to reduce CMV have been presented in previous research. One solution is based on the use of additional hardware, such as passive filters, active cancellers, or electromagnetic interference filters, to mitigate CMV [16], [17]. However, this method introduces increased converter volume, weight, and cost. Another solution is to investigate the modulation technique. Using suitable PWM, mitigating the CMV is achievable within the power converter. Several studies have proposed CMV reduction for NPC topology by applying the appropriate modulation techniques. However, these methods focus on the SVPWM method, which has several disadvantages [18], [19]. This method requires complex calculations and tables to synthesize the reference output voltage. In [20]-[22], the phase opposition disposition (POD) was proposed to reduce CMV for NPC. However, this method has high THD in the output voltage, a high RMS value, and a poor harmonics spectrum in the CMV.

To overcome the drawbacks of phase disposition (PD) PWM and POD PWM schemes, this study proposes a novel carrier-based PWM method for use with T-NPC to eliminate CMV. The proposed strategy uses three-phase carriers of the same frequency with a phase difference of 120°. The proposed method is simple to implement and does not require any additional hardware. The advantages of the proposed method are as follows:

- Eliminates the peak value of the CMV, and the magnitude is reduced by 50% compared with that when using the conventional PD PWM scheme.

- Exhibits better harmonic spectrum for CMV and reduces the RMS of CMV when with the conventional POD PWM scheme.

The remainder of this paper is organized as follows: The three-level T-type NPC operation and the effect of the switching state on CMV are described in Section II. The conventional PD and POD schemes are also presented in this section. The proposed method is presented in Section III. The simulation and experimental results are provided in Sections IV and V, respectively. Study conclusions are provided in the final section.

# II. CMV ANALYSIS AND CONVENTIONAL METHODS

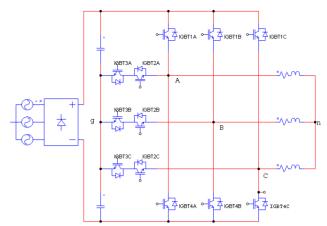

## A. Three-Level T-Type NPC Inverter Topology

The three-level T-type NPC inverter topology is illustrated in Fig. 1. Each leg of the TNPC consists of four power-switch devices: IGBT1X and IGBT4X (X = A,B,C) are connected to the positive and negative poles of the dc power supply, respectively, and one bidirectional switch (IGBT2X and

Fig. 1. Three-level T-NPC Inverter topology.

TABLE I

SWITCHING STATES OF THE T-NPC

| Switching | Switching Status |        |        |        | Output             |

|-----------|------------------|--------|--------|--------|--------------------|

| State     |                  |        |        |        | Voltage            |

| $S_X$     | IGBT1X           | IGBT2X | IGBT3X | IGBT4X | $V_{Xg}$           |

| +1        | ON               | ON     | OFF    | OFF    | V <sub>dc</sub> /2 |

| 0         | OFF              | ON     | ON     | OFF    | 0                  |

| -1        | OFF              | OFF    | ON     | ON     | $-V_{dc}/2$        |

IGBT3X) connects the middle point of the dc-link to the load. The three-level T-type NPC topology is simpler than that of conventional NPC and provides some advantages that are unavailable in conventional NPC, such as low conduction losses, fewer power switches, and small size [9], [10].

The switching states of the power switches and the output voltage of the three-level T-Type NPC are shown in Table I. The three phase levels of common point voltage that can be generated on each phase leg are  $\pm V_{dc} = 10^{-2}$ , where  $V_{dc} = 10^{-2}$  is the dc-link voltage, and X represents each phase (X = A, B, or C).

### B. Common-Mode Voltage Analysis

The CMV of the three-level T-Type NPC is defined as the voltage between load neutral point n and the mid-point of dc-link voltage g, as shown in Fig. 1. We assumed that the three-phase RL load is balanced. The CMV is derived from the following equations:

$$v_{Ag} = v_{ng} + R_A i_A + L_A \frac{di_A}{dt}$$

$$v_{Bg} = v_{ng} + R_B i_B + L_B \frac{di_B}{dt}$$

$$v_{Cg} = v_{ng} + R_C i_C + L_C \frac{di_C}{dt}$$

(1)

where  $v_{Ag}$ ,  $v_{Bg}$ , and  $v_{Cg}$  are the three phase output voltages with respect to ground point g; and  $i_A$ ,  $i_B$ , and  $i_C$  are the three phase output currents.

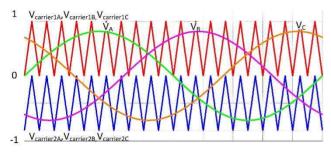

Fig. 2. Carrier and reference waveforms for three-level T-NPC inverter using PD PWM scheme.

Fig. 3. Carrier and reference waveforms for three-level T-NPC inverter using POD PWM scheme.

Given that the three-phase load is balanced, the CMV becomes

$$v_{ng} = \frac{1}{3} \left( v_{Ag} + v_{Bg} + v_{Cg} \right)$$

(2)

The CMV depends on the switching states of the three-level T-type NPC inverter and can be determined using the following switching functions:

$$V_{ng} = \frac{V_{dc}}{6} (S_A + S_B + S_C)$$

(3)

Eq. (3) and Table I show that the CMV has seven values: 0,  $\pm V_0/6$ ,  $\pm V_0/3$ , and  $\pm V_0/2$ . They are provided in detail in Table II. Regardless of the AC source, the CMV is determined by the output voltages, which depend only on the switching states of the three-level T-type NPC inverter.

### C. Conventional Methods

- 1) Phase Disposition (PD) PWM Scheme: The PD PWM scheme is used in the carrier-based implementation [15],[16]. Fig. 2 shows the basic principle of the PD PWM scheme using double triangle carrier signals. The upper carrier signal (V<sub>carrier1X</sub>) is used to generate the gate signal for switch IGBT1X, IGBT3X. The lower carrier signal (V<sub>carrier2X</sub>) is used to generate the gate signal for the switch IGBT2X, IGBT4X. Two carrier waveforms are arranged so that every carrier is in phase; one is above zero and the other is below zero.

- 2) Conventional Reduced-CMV Method Based on Phase Opposition Disposition PWM Scheme: For POD schemes, the three carrier signals above zero are in phase, and the three carrier signals below zero are also in phase. However, the upper carrier signal and the lower carrier signal are in

TABLE II

CMV ACCORDING TO SWITCHING STATES

| Switching state (S <sub>A</sub> S <sub>B</sub> S <sub>C</sub> ) | CMV         |

|-----------------------------------------------------------------|-------------|

| 000,-101,10-1,01-1, 0-11,1-10,-110                              | 0           |

| 111                                                             | $V_{dc}/2$  |

| -1-1-1                                                          | $-V_{dc}/2$ |

| 110, 101, 011                                                   | $V_{dc}/3$  |

| -1-10, -10-1, 0-1-1                                             | $-V_{dc}/3$ |

| 1-1-1,11-1,-11-1, -100,0-10,00-1                                | $-V_{dc}/6$ |

| 11-1,1-11,-111, 100,010,001                                     | $V_{dc}/6$  |

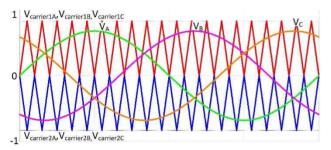

opposite phase, as shown in Fig. 3.

As shown in Figs. 3 and 4, the upper triangle magnitude is normalized from 1 to 0, and the lower triangle magnitude is normalized from -1 to 0.

# III. PROPOSED CARRIER PHASE-SHIFT PWM METHOD FOR CMV REDUCTION

Table II shows that by employing 19 switching states (000, -101, 10-1, 01-1, 0-11, 1-10, -110, 1-1-1, 11-1, -11-1, -100, 0-10, 00-1, 11-1, 1-11, -111, 100, 010, 001) to synthesize the reference output voltage, the peak value of CMV is limited at  $V_{dv}/6$ .

We assume that the normalized three-phase reference outputs are given as

$$V_{A} = m\sin(\omega t) \tag{4}$$

$$V_B = m \sin\left(\omega t - \frac{2\pi}{3}\right) \tag{5}$$

$$V_C = m \sin\left(\omega t + \frac{2\pi}{3}\right),\tag{6}$$

where m is the modulation index, and  $\omega$  is the input angular frequency.

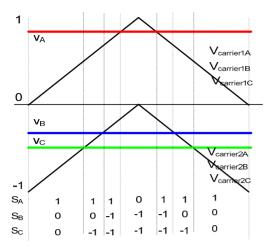

Two conditions are possible for the six different situations when the three phase output voltages are balanced. In the first condition, two input phase voltages are positive, and one phase voltage is negative. In the second condition, two input phase voltages are negative, and one phase voltage is positive. Without losing the generality of the analysis, we assume that the output voltage of Phase A is positive and the output voltages of Phases B and C are negative, as shown in Fig. 3. Therefore, the possible switching states for Phase A are 1 or 0, and the possible switching states for Phases B and C are 0 or -1. Fig. 4 shows that the switching state (0-1-1) causes the CMV to be at  $-V_{dc}/3$ . Thus, to reduce the CMV peak, we must avoid using this switching state to synthesize the reference output voltages. Two carrier signals are used in the conventional PD and POD methods. In this study, carrier phase-shift PWM is proposed based on six carrier signals that are used to generate a gating pulse for the three-level T-type NPC.

Fig. 4 Reference output voltage, triangle carrier signals, and switching states of the conventional PD PWM method.

The proposed carrier phase shift is developed based on the conventional PD PWM method. According to Table II, the peak CMV can be reduced from  $V_{dc}/2$  to  $V_{dc}/6$  if the switching states 111, -1-1-1, 110, 101, 011, -1-10, -10-1, and 0-1-1 are not used.

Given that the input voltages are balanced as shown in Eq. (7), two other conditions are possible: (1) Two input phase voltages are positive and one phase voltage is negative; and (2) Two input phase voltages are negative and one phase voltage is positive.

$$V_A + V_R + V_C = 0 (7)$$

$V_{\rm A} + V_{\rm B} + V_{\rm C} = 0 \eqno(7)$  Without losing the generality of the analysis, we assume that  $\,V_{\rm A}>0,\,\,V_{\rm B}<0,\,\,V_{\rm C}<0$  . Table II and Fig. 1 shows that the switching stage becomes 0-1-1 and it causes the peak CMV to become higher than  $V_{dc}/6$ .

The relationship between the reference output voltage and the carrier signals are given in Eq. (8) for the switching state 0-1-1.

$$\begin{aligned} 0 &< V_A < V_{carrier1A} \\ V_B &< V_{carrier2B} < 0 \\ V_C &< V_{carrier2C} < 0 \end{aligned} \tag{8}$$

From Fig. 2, the relationship between the upper and lower carrier signals is

$$V_{carrier1B} - V_{carrier2B} = 1; V_{carrier1C} - V_{carrier2C} = 1$$

(9)

Substituting Eq. (9) into Eq. (8), we have

$$\begin{aligned} 0 &< V_A < V_{carrier1A} \\ V_B &< V_{carrier1B} - 1 < 0 \\ V_C &< V_{carrier1C} - 1 < 0 \end{aligned} \tag{10}$$

From Eqs. (8) and (10), we can obtain Eq. (11):

$$0 < V_A + V_B + V_C < V_{carrier1A} + V_{carrier1B} + V_{carrier1C} - 2$$

$$\tag{11}$$

Therefore,

$$V_{carrier1A} + V_{carrier1B} + V_{carrier1C} > 2$$

(12)

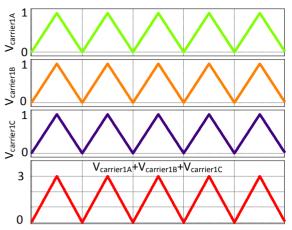

Fig. 5. Carrier waveforms for three-level T-type NPC inverter using PD PWM scheme.

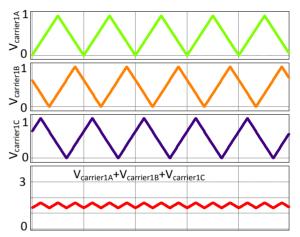

Fig. 6. Carrier waveforms for three-level T-type NPC inverter using proposed carrier phase shift PWM scheme.

To reduce CMV, the state 0-1-1 must be avoided. Therefore, the relationship between three carrier signals has to fully meet Eq. (13).

$$V_{carrier1A} + V_{carrier1B} + V_{carrier1C} < 2 \tag{13}$$

Fig. 5 shows the three upper carrier signals for legs A, B, and C through the conventional SPWM method. The sum of the three carrier signals is larger than 2. Therefore, a peak CMV with the value  $V_{dc}/3$  is obtained.

If the three carrier signals for Phases A, B, and C are chosen with a displacement of 120°, as shown in Fig. 6, the sum of the three carrier signals is less than 2. Thus, the maximum CMV is V<sub>dc</sub>/6. In the proposed carrier phase-shift method, the upper carrier signal and lower carrier signals for each leg are in phase. However, three upper and lower carrier signals for legs A, B, and C are out of phase by 120°.

### SIMULATION RESULTS

We conducted simulations using PSIM 9.0 software to verify the effectiveness of the new SVM method. The system is simulated with the following parameters:

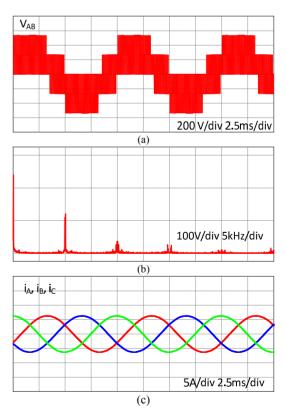

Fig. 7 (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Three phase output currents using the PD PWM method.

- Dc-link voltage  $V_{dc} = 530 \text{ V}$

- Three-phase RL load:  $R = 30 \Omega$ , L = 15 mH

- Modulation index m = 0.8

- Output frequency:  $f_{out} = 50 \text{ Hz}$

- PWM frequency = 10 kHz

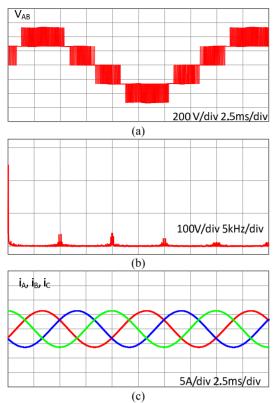

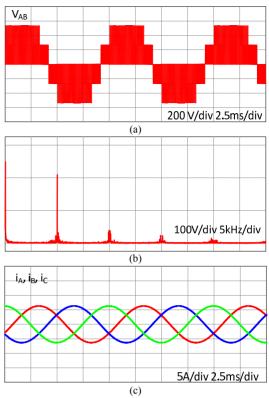

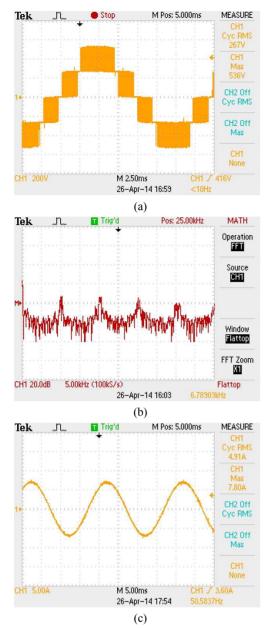

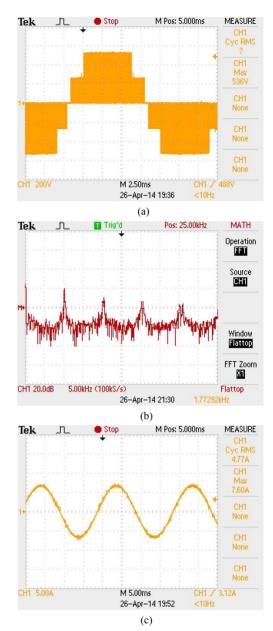

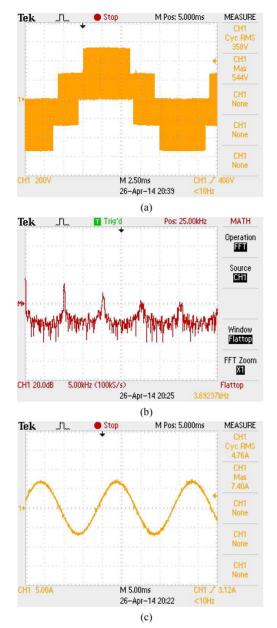

Figs. 7 to 9 show the line-to-line output voltage, its FFT, and the three-phase output currents for the modulation index m = 0.8 and output frequency 50 Hz using the PD, POD, and PWM schemes, respectively. The proposed PWM method provides the same sinusoidal output currents as those of the other PWM methods. The different output voltage waveforms result from different modulation methods. The fast Fourier transform (FFT) results of the line-to-line output voltage show fewer harmonics for the proposed method than for the conventional reduced-CMV-based POD method. However, the THD of the line-to-line output voltage with the proposed method slightly increases compared with that of the conventional PD PWM method.

Figs. 10 to 12 show the CMV waveforms and their FFT analysis when employing the PD, the conventional reduced-CMV-based POD method, and the proposed method, respectively, at an output frequency of 50 Hz and a modulation index of 0.8. The conventional reduced-CMV-based POD method and the new carrier phase-shift method provide the same CMV peak value (88 V). Fig. 10 shows the CMV pulses of magnitude  $V_{\rm dc}/3$  (177 V)

Fig. 8 (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Three phase output currents using the POD PWM method.

Fig. 9. (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Three phase output currents using the proposed carrier phase-shift PWM method.

Fig. 10. (a) Common-mode voltage. (b) FFT using the PD PWM method with m=0.8 and  $f_{out}=50$  Hz.

Fig. 11. (a) Common-mode voltage. (b) FFT using the POD PWM method with m=0.8 and  $f_{out}=50$  Hz.

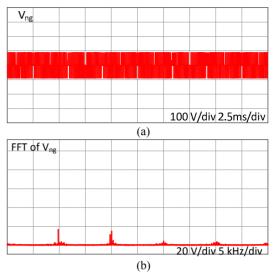

when the PD method is applied. Compared with the conventional PD method, the proposed method significantly reduces the CMV peak value by 50%. Furthermore, the spectrum analysis of the CMV shows that the CMV of the proposed PWM scheme contains fewer harmonic components compared with the conventional PD and POD PWM schemes.

### V. EXPERIMENTAL RESULTS

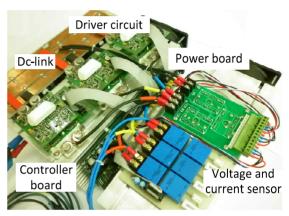

To validate the proposed theories and simulations, we designed an experimental setup in the laboratory. The experimental prototype is shown in Fig. 13. The half-bridge IGBT modules SEMiX202GB128Ds (1,200 V) were selected for switch pairs IGBT1X, IGBT4X. The bidirectional IGBT modules SK60GM123 (1,200 V) were chosen for the switch pairs IGBT2X, IGBT3X. The prototype is controlled with the use of a high-performance, floating-point digital signal

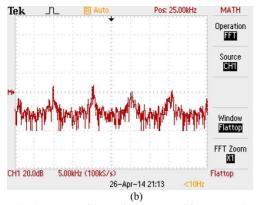

Fig. 12. (a) Common-mode voltage. (b) FFT using the proposed PWM method with m=0.8 and  $f_{out}=50$  Hz.

Fig. 13. Laboratory T-NPC prototype.

processor (DSP) 90 MHz TMS320F28069 from Texas Instruments. The parameters used in the experiment are the same as in the simulation. The PWM operates at 10 kHz.

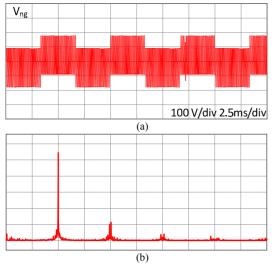

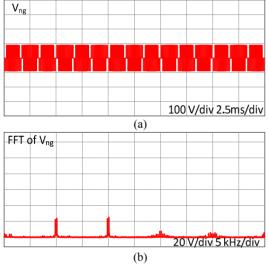

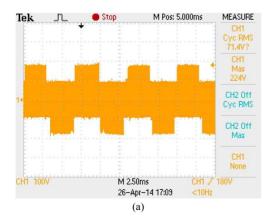

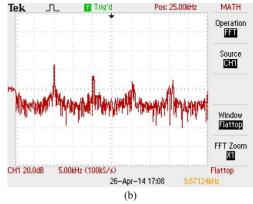

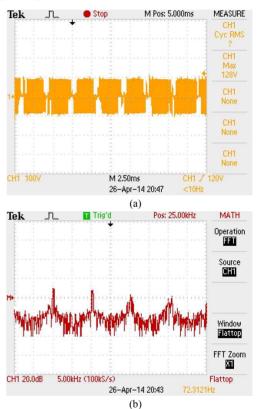

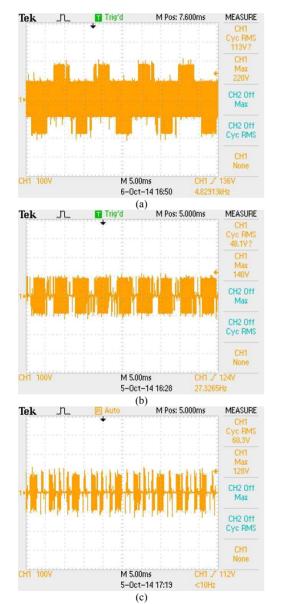

Figs. 14 to 16 show the experimental results for the line-to-line output voltage, its FFT, and the output currents of the conventional PD, POD, and proposed PWM methods, respectively. Every method provides almost pure sinusoidal output currents, and the proposed PWM method does not decrease the performance of the output currents. The spectrum and phase output voltage are comparable to the output performance for the two conventional methods and the proposed carrier phase-shift PWM method. Figs. 14b, 15b, and 16b show the harmonic spectrum of the output line-to-line voltage for the three PWM methods. The spectrums indicate that the proposed PWM method has good voltage compared with the conventional reduced-CMV-based POD method. However, the proposed method has several drawbacks. The performance of the output voltage using the proposed method is worse than that of the PD PWM method and exhibits a trade-off between CMV reduction and output voltage performance.

Fig. 14. (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Output current at an output frequency of 50 Hz and a modulation index of m = 0.8 using the PD method.

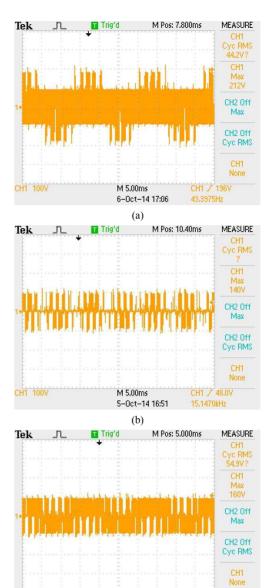

Fig. 17 shows the CMV waveforms of the three-level T-type NPC inverter when the PD PWM method is applied. The peak value of the CMV is achieved at 177 V, which corresponds to V<sub>dc</sub>/3. Figs. 18 and 19 show the CMV of the three-level T-type NPC inverter when the conventional reduced-CMV method (POD method) and the proposed method are used, respectively. The two methods reduce the peak value of CMV. The peak value of CMV decreases from 177 V to 86 V, which corresponds to V<sub>dc</sub>/6. Compared with the conventional PD method, the proposed method significantly reduces the CMV peak value by 50%. According to an FFT of the CMV, the new SVM method generates a smaller harmonic component than that of the PD

Fig. 15. (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Output current at an output frequency of 50 Hz and a modulation index of m = 0.8 using the POD method.

### PWM method.

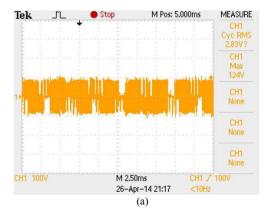

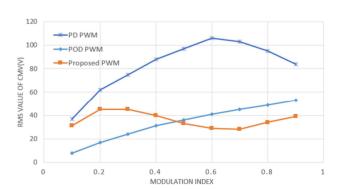

The performance of the proposed PWM method has been also tested by considering low modulation index and low frequency. The CMV with PD, POD, and the proposed carrier phase shift PWM methods at f=30Hz, m=0.6, and f=20Hz, m=0.3 are shown in Figs. 20 and 21, respectively. The POD and carrier phase shift PWM methods provides a 50% reduction in the CMV (peak value) compared with the conventional PD PWM method. Fig. 22 shows the RMS value of the CMV with the PD, POD, and the proposed PWM methods according to the modulation index. Compared with the conventional reduced CMV–POD PWM method, the proposed method provides a lower RMS value for the CMV

Fig. 16. Experimental results of (a) Line-to-line output voltage. (b) FFT of line-to-line output voltage. (c) Output current at an output frequency of 50 Hz and a modulation index of m=0.8 using the proposed PWM method.

Fig. 17. (a) CMV waveforms and (b) its FFT with PD method at an output frequency of 50 Hz and a modulation index of m = 0.8.

Fig. 18. (a) CMV waveforms. (b) Its FFT with POD method at an output frequency of 50 Hz and a modulation index of m = 0.8.

Fig. 19. (a) CMV waveforms. (b) Its FFT with proposed method at an output frequency of 50 Hz and a modulation index of m = 0.8.

Fig. 20. CMV waveforms. (a) PD PWM. (b) POD PWM methods. (c) The proposed method at an output frequency of 30 Hz and a modulation index of m = 0.6.

Fig. 21. Experimental result of CMV waveforms. (a) PD PWM. (b) POD PWM methods. (c) The proposed method at an output frequency of 20 Hz and a modulation index of m = 0.3.

(c)

5-0ct-14 17:37

Fig. 22. Comparison with the RMS values for different CMV.

at the modulation index higher than 0.5. However, at a lower modulation index, the RMS value of the CMV with the proposed method becomes higher than that using the POD PWM method. Thus, using a combined PWM algorithm that uses the proposed POD PWM method with a low modulation index as well as using the proposed method at high modulation index to control full output voltage range is recommended.

### VI. CONCLUSIONS

A carrier phase-shift PWM method is proposed in this study to reduce CMV for three-level T-type NPC inverters. The proposed method achieves a peak value of CMV, which is reduced by 50% compared with that of the conventional PD PWM method. The proposed method has a lower RMS value of CMV than the POD PWM method at a modulation index higher than 0.5. The proposed method is implemented simply, and no additional computations are needed beyond those of conventional PD and POD PWM schemes. Finally, experimental results have been provided to verify the theoretical analysis and simulation results.

#### ACKNOWLEDGMENT

This work was supported by 2014 Research Funds of Hyundai Heavy Industries for University of Ulsan.

### REFERENCES

- [1] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, Vol. 49, No. 4, pp. 724-738, Aug. 2002.

- [2] J.-S. Lai and F. Z. Peng, "Multilevel converters-a new breed of power converters," *IEEE Trans. Ind. Appl.*, Vol. 32, No. 3, pp. 509-517, May/Jun 1996.

- [3] K.-M. Tsang and W.-L. Chan, "Single DC source three-phase multilevel inverter using reduced number of switches," *IET Power Electron.*, Vol. 7, No. 4, pp. 775-783, Apr. 2014.

- [4] J. D. Barros, J. F. A. Silva, and E. G. A. Jesus, "Fast-predictive optimal control of NPC multilevel converters," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 2, pp. 619-627, Feb. 2013.

- [5] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 6, pp. 2930-2945, Dec. 2007.

- [6] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 8, pp. 2553-2580, Aug. 2010.

- [7] I. D. Pharne, and Y. N. Bhosale, "A review on multilevel inverter topology," *Power, Energy and Control (ICPEC)*, 2013 International Conference on, pp. 700-703, 2013.

- [8] R. P. Vishvakarma, S. P. Singh, and T. N. Shukla, "Multilevel inverters and its control strategies: A comprehensive review," *Power, Control and Embedded Systems (ICPCES)*, 2012 2nd International Conference on, pp. 1-9, 2012.

- [9] U.-M. Choi, H.-H. Lee, and K.-B. Lee, "Simple neutral-point voltage control for three-level inverters using a discontinuous pulse width modulation," *IEEE Trans. Energy Convers.*, Vol. 28, No. 2, pp. 434-443, Jun. 2013.

- [10] M. Schweizer and J. W. Kolar, "High efficiency drive system with 3-level T-type inverter," *Power Electronics and Applications (EPE 2011), Proceedings of the 2011-14th European Conference on*, pp. 1-10, 2011.

- [11] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," *IET Power Electron.*, Vol. 4, No. 8, pp. 951-958, Sep. 2011.

- [12] Y. Jiao, S. Lu, F. C. Lee, "Switching performance optimization of a high power high frequency three-level active neutral point clamped phase leg," *IEEE Trans. Power Electron.*, Vol. 29, No. 7, pp. 3255-3266, Jul. 2014.

- [13] Y. Irouz, M. T. Bina, and B. Eskandari, "Efficiency of three-level neutral-point clamped converters: analysis and experimental validation of power losses, thermal modelling and lifetime prediction," *IET Power Electron.*, Vol. 7, No. 1, pp. 209-219, Jan. 2014

- [14] Q. Chen, Q. Wang, G. Li, and W. Jiang, "Analysis and comparison of power losses in 3L-NPC inverter with SHPWM control," *Electrical Machines and Systems* (ICEMS), 2012 15th International Conference on, pp. 1-5, 2012.

- [15] K.-M. Tsang and W.-L. Chan, "Single DC source three-phase multilevel inverter using reduced number of switches," *IET Power Electron.*, Vol. 7, No. 4, pp. 775-783, Apr. 2014.

- [16] H. Akagi, H. Hasegawa, and T. Doumoto, "Design and performance of a passive EMI filter for use with a voltage-source PWM inverter having sinusoidal output voltage and zero common-mode voltage," *IEEE Trans. Power Electron.*, Vol. 19, No. 4, pp. 1069-1076, Jul. 2004.

- [17] H. Akagi and T. Doumoto, "An approach to eliminating high-frequency shaft voltage and ground leakage current from an inverter-driven motor," *IEEE Trans. Ind. Appl.*, Vol. 40, No. 4, pp. 1162-1169, Jul./Aug. 2004.

- [18] C. Bharatiraja, S. Raghu, and R. Palanisamy, "A new space vector pulse width modulation for reduction of common mode voltage in three level neutral point diode clamped multilevel inverter," Advances in Engineering, Science and Management (ICAESM), 2012 International Conference on, pp. 694-699, 2012.

- [19] L. Long, Y. Zhang, and G. Kuang, "A modified space vector modulation scheme to reduce common mode voltage for cascaded NPC/H-bridge inverter," *Power Electronics* and Motion Control Conference (IPEMC), 2012 7th International, Vol. 3, pp. 1837-1841, 2012.

- [20] A. Radan, A. H. Shahirinia, and M. Falahi, "Evaluation of carrier-based PWM methods for multi-level inverters," *Industrial Electronics*, 2007. ISIE 2007. IEEE International Symposium on, pp. 389-394, 2007.

- [21] I. M. Salagae and H. du T Mouton, "Natural balancing of neutral-point-clamped converters under POD pulsewidth modulation," *Power Electronics Specialist Conference*, 2003. PESC '03. 2003 IEEE 34th Annual, Vol. 1, pp. 47-52 Vol. 1, 2003.

[22] M. M. Renge and H. M. Suryawanshi, "Multilevel inverter to reduce common mode voltage in AC motor drives using SPWM technique," *Journal of Power Electronics*, Vol. 11, No. 1, pp. 21-27, Jan. 2011.

**Tuyen D. Nguyen** was born in BinhDinh, Vietnam, in 1982. He received his B.S. degree in electrical engineering from the University of Technology, Hochiminh City, Vietnam, in 2004 and his Ph.D degree from the University of Ulsan, Ulsan, Korea in 2012. He is currently a lecturer for the Faculty of Electrical and Electronics Engineering, Hochiminh city

University of Technology, VNU-HCM, Vietnam. His research interests include power electronics, electrical machine drives, and low cost inverter and renewable energy, especially matrix converters

**Dzung Quoc Phan** was born in Saigon, Vietnam, in 1967. He received his Dipl.-Eng. degree in electromechanical engineering from Donetsk Polytechnic Institute, Donestk City, Ukraine, in 1991 and his Ph.D degree in engineering sciences from Kiev Polytechnic Institute, Kiev City, Ukraine, in 1995. He became an Associate Professor in electrical

engineering at University of Technology, Hochiminh City, Vietnam in 2010. He is currently senior lecturer for the Faculty of Electrical and Electronics Engineering, University of Technology, Hochiminh City, Vietnam. His research areas include power electronics and electric machines, static power converters, especially multilevel converters and its applications in renewable energy and micro-grids.

**Dat Ngoc Dao** was born in BinhDinh province, Vietnam on 24 February 1990. He studied electrical engineering five years at the University of Technology, Hochiminh city, Vietnam and received his B.S. degree in 2014. He focused on power electronics, digital control and designing power converter, inverter, photovoltaic applications, motor

drivers during his studies. His thesis dealt with design and a high-power high-efficiency three-phase three-level inverter used to inject the power of PV panels into the national grid. Since 2012, Dat Ngoc Dao has worked at the Advanced Power Electronics Laboratory in the university, where he is conducting research on a national project.

Hong-Hee Lee received his B.S., M.S., and Ph.D. in Electrical Engineering from Seoul National University, Seoul, Korea, in 1980, 1982, and 1990, respectively. From 1994 to 1995, he was a Visiting Professor at the Texas A&M University. He has been a Professor in the School of Electrical Engineering in the Department of Electrical

Engineering, University of Ulsan, Ulsan, Korea since 1985. He is also the Director of the Network-based Automation Research Center (NARC), which is sponsored by the Ministry of Trade, Industry and Energy. His research interests include power electronics, network-based motor control, and renewable energy. Dr. Lee is a member of the Institute of Electrical and Electronics Engineers (IEEE), the Korean Institute of Power Electronics (KIPE), the Korean Institute of Electrical Engineers (KIEE), and the Institute of Control, Robotics and Systems (ICROS). He is now the President of KIPE.